ZHCAEI4 September 2024 PCA9306 , TCA39306 , TCA9548A

2.1 什么是挂起时间效应?为什么会出现挂起时间?

本应用手册将挂起时间效应定义为 I2C 总线在从高电平到低电平的总线转换期间完全拉至 VOL 之前处于空闲状态(即挂起)的时间长度(通常以纳秒为单位)。如果转换率足够快,则可能会在上升沿发生这种情况。产生这种效应的部分原因在于 passFET 的漏源电阻发生变化,但更直接的原因是 I2C 总线上的寄生电容。图 2-4 展示了与之前使用 TCA39306 相同的示例电路,但这次加入了寄生总线电容 CBUS1 和 CBUS2。

图 2-4 使用 TCA39306 且包含寄生总线电容

图 2-4 使用 TCA39306 且包含寄生总线电容如果目标器件将 SDA 拉至低电平,CBUS2 的电压(即 passFET 漏极或源极的电压)可以拉至 VOL,如图 2-5 所示。

图 2-5 SDA2 被拉至 VOL 且 CBUS2 充电至 5.0V

图 2-5 SDA2 被拉至 VOL 且 CBUS2 充电至 5.0VI2C 标准中定义的输出低电压 VOL 指定了 VOL = 0.4V 时的最小低电平输出电流 > 3mA。本例中假设 VOL 接近 GND,因为开漏驱动器的电阻非常小。

当目标器件拉低至接近 VOL 时,源极电压可能会降低,从而导致 VGS 增加并快速超过 passFET 的阈值电压。这会将 passFET 置于低阻抗状态,将 SDA1 连接到 SDA2。然后目标器件可以检测到 CBUS1 上的电荷,如图 2-6 所示。

图 2-6 passFET 导通,从而允许目标器件检测到 CBUS1 上的电荷

图 2-6 passFET 导通,从而允许目标器件检测到 CBUS1 上的电荷这正是产生挂起时间效应的地方。只有当寄生总线电容 CBUS1 和 CBUS2 上的电荷达到平衡时,SDA2 才能继续拉至 V OL,从而有效地挂起 I2C 总线。一旦总线寄生电容 CBUS1 和 CBUS2 上的电荷达到平衡,SDA2 就能继续拉低至 VOL。SDA1 可以跟随 SDA2,但由于 passFET 导通 电阻,SDA1 的 RDS_ON 压降可能会高于 SDA2。

I2C 总线挂起的时间取决于多个因素。

- 系统中的寄生总线电容值

- 电压电源电平

- 相对于最大总线电容,哪一侧首先拉至低电平

- 驱动强度

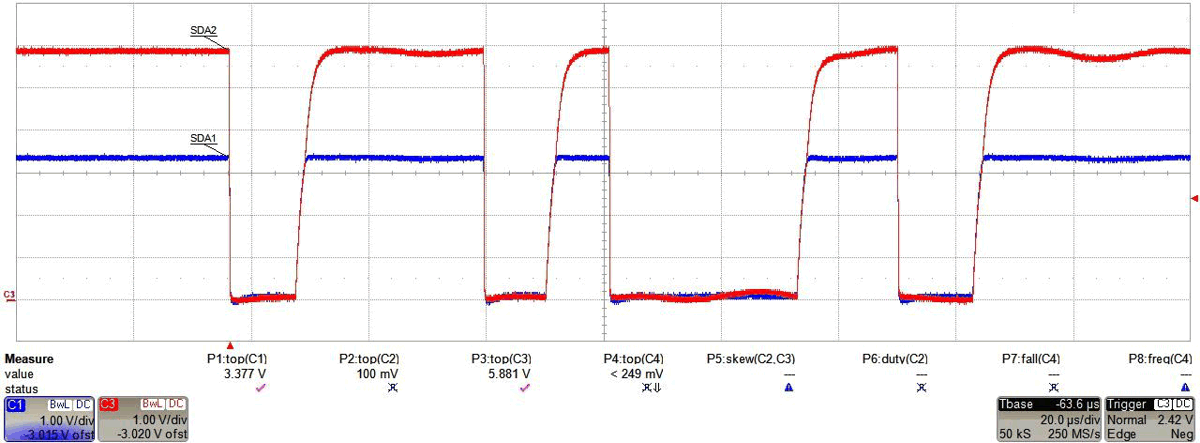

在测试 TCA39306 的挂起时间时,这种现象在较大的时间刻度下并不明显。图 2-7 显示了在 SDA 上发送地址 0x74 时的示波器截图。数据被恰当地标记为 SDA1(控制器侧)和 SDA2(目标器件侧)。I2C 以 100kHz 的频率发送,转换器每侧都有 10kΩ 上拉电阻器。

图 2-7 通过 TCA39306 发送地址 0x74(VCC1 = 3.3V、VCC2 = 5.0V、CBUS1 = 100pF、CBUS2 = 100pF、目标器件侧 (SDA2) 拉至低电平时)

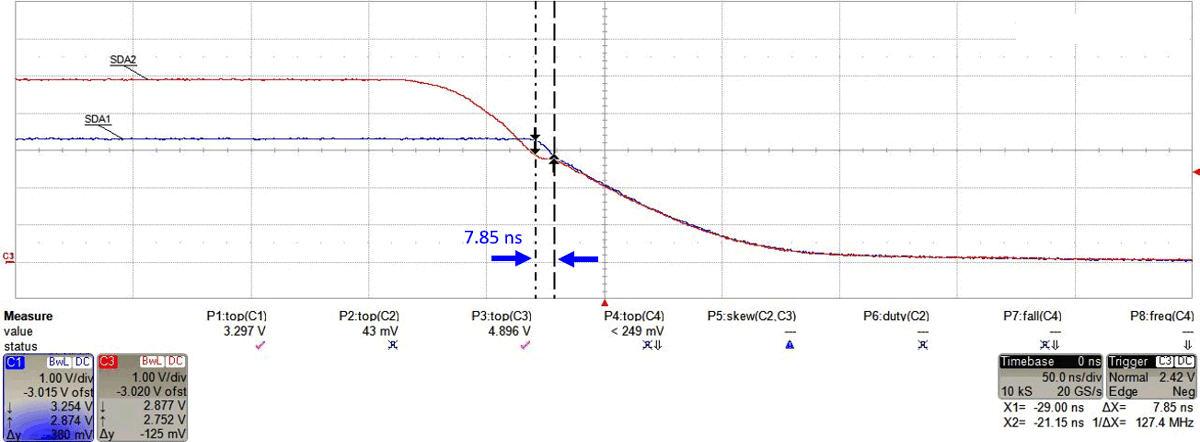

图 2-7 通过 TCA39306 发送地址 0x74(VCC1 = 3.3V、VCC2 = 5.0V、CBUS1 = 100pF、CBUS2 = 100pF、目标器件侧 (SDA2) 拉至低电平时)当时间刻度更改为每格 50.0ns 时,该效应变得更加明显,如图 2-8 所示。

图 2-8 VCC1 = 3.3V、VCC2 = 5.0V、CBUS1 = C BUS2 = 100pF、目标器件侧 (SDA2) 拉至低电平

图 2-8 VCC1 = 3.3V、VCC2 = 5.0V、CBUS1 = C BUS2 = 100pF、目标器件侧 (SDA2) 拉至低电平该测试中测得的挂起时间为 7.85ns。通过调整前面列出的四个参数,可以延长总线挂起的时间:寄生总线电容、电源电平、驱动侧和驱动强度。由于无法在内部更改驱动强度,因此本应用手册并未探讨驱动强度。

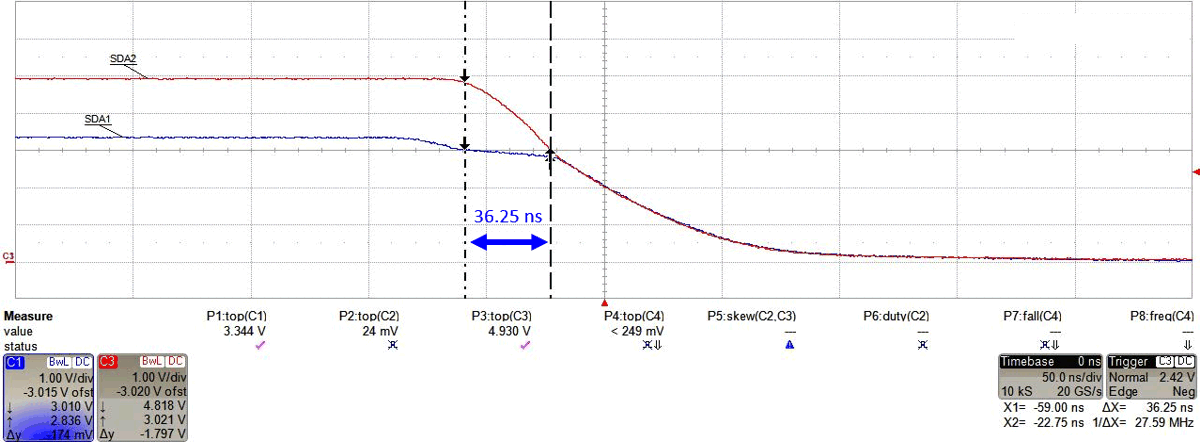

将驱动侧更改为控制器侧 (SDA1) 时,挂起时间会增加到约 36.25ns,如图 2-9 所示。

图 2-9 VCC1 = 3.3V、VCC2 = 5.0V、CBUS1 = C BUS2 = 100pF、控制器侧 (SDA1) 拉至低电平

图 2-9 VCC1 = 3.3V、VCC2 = 5.0V、CBUS1 = C BUS2 = 100pF、控制器侧 (SDA1) 拉至低电平回顾图 2-6 中的设置,目标器件的总线电容 CBUS2 会充电至 5.0V,而控制器的总线电容 CBUS1 会充电至 3.3V。挂起时间的增加导致目标器件侧拉低与控制器侧拉低之间的时间差为 7.85ns 至 36.25ns。拉低控制器侧会导致更长的挂起时间,因为在 passFET 的另一端存在电压更大的电容器。在 passFET 导通 后,控制器会突然检测到这个 5.0V 电容器,其中电荷开始流动。目标器件侧拉低会更快,因为 5.0V 电容器会首先放电,而控制器侧的一个 3.3V 电容器会第二个放电。

当寄生总线电容变大时,挂起时间会增加。这是因为较大的电容器就像容量较大的电池,能够储存更多的电荷。考虑 CBUS1 = 100pF 且 CBUS2 = 400pF 的情况,重新排列以下电压与电容的公式。

如果电容保持不变,则电压的增加也意味着电容器上的电荷 Q 会增加。因此,

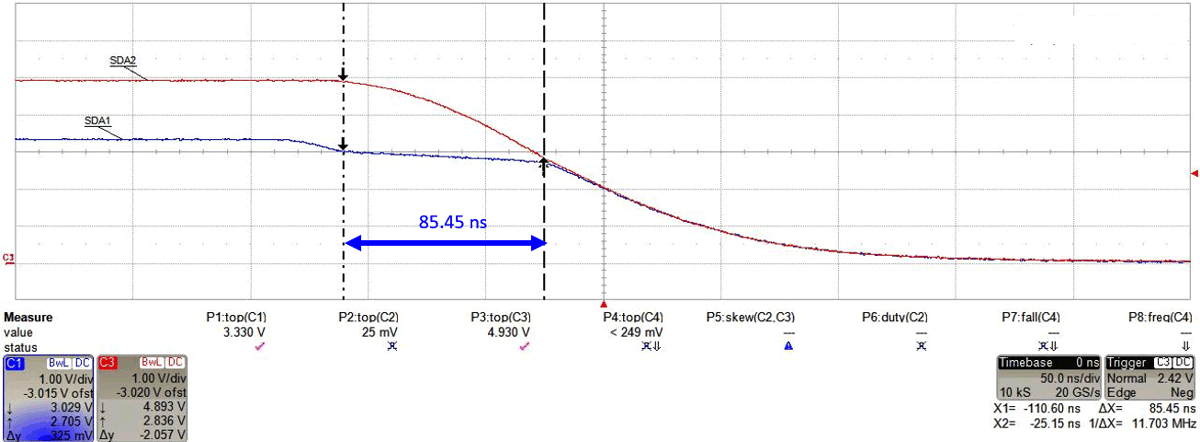

与充电至 5V 的 100pF 电容器相比,充电至 5V 的 400pF 电容器所存储的电荷更多。虽然两个电容器表现出相同的电压,但 400pF 寄生电容器具有更大的电荷储存容量。因此,当控制器侧 (SDA1) 被拉至低电平时,由于 passFET 目标器件侧 (SDA2) 的 400pF 寄生电容上存储了更多的电荷,因此可能会存在更长的挂起时间。这会使总线在 SDA 达到 VOL 之前保持更长的时间。图 2-10 展示了这一效应。

图 2-10 VCC1 = 3.3V、VCC2 = 5.0V、CBUS1 = 100pF、CBUS2 = 400pF、控制器侧 (SDA1) 拉至低电平

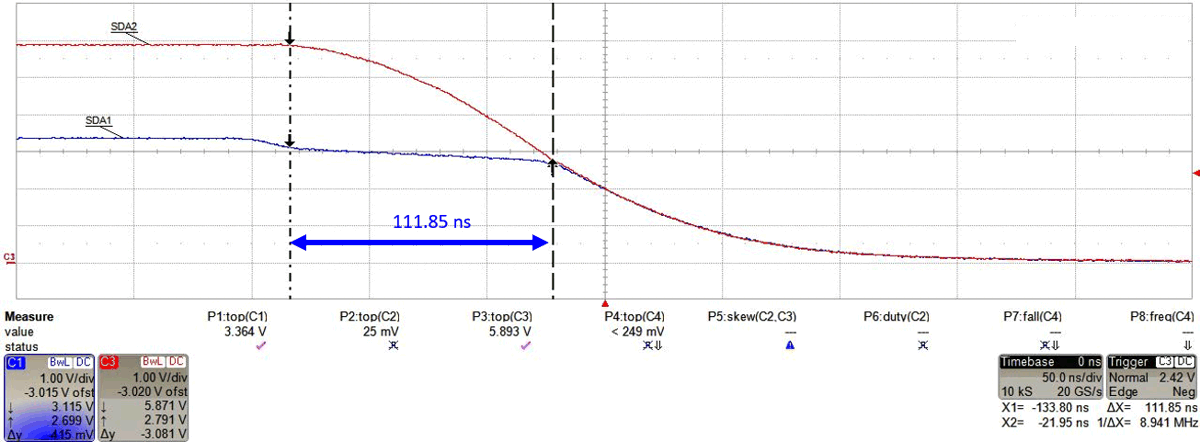

图 2-10 VCC1 = 3.3V、VCC2 = 5.0V、CBUS1 = 100pF、CBUS2 = 400pF、控制器侧 (SDA1) 拉至低电平挂起时间增加到 85.45ns,超过了图 2-9 中的两倍。当 VCC2 的电源电压增加到 6.0V 时,挂起时间会更长。电势的增加会导致 CBUS2 上的总电荷增加。图 2-11 展示了因 VCC2 上的电源电压增大而导致的挂起时间延长。

图 2-11 VCC1 = 3.3V、VCC2 = 6.0V、CBUS1 = 100pF、CBUS2 = 400pF、控制器侧 (SDA1) 拉至低电平

图 2-11 VCC1 = 3.3V、VCC2 = 6.0V、CBUS1 = 100pF、CBUS2 = 400pF、控制器侧 (SDA1) 拉至低电平