ZHCAEJ8 October 2024 TAC5412-Q1

2.3 信号发生器 1 频率

寄存器 B0_P18_R32 (0x20) 至 B0_P1_R47 (0x2F) 配置 SG1 频率。SG1 频率配置是在振幅和输出通道配置之后进行的。请参阅节 2.2。

这组公式为 SG1 频率配置生成寄存器系数:

方程式 2.

方程式 3.

方程式 4.

方程式 5.

方程式 6.

方程式 7.

方程式 8.

方程式 9.

请注意生成的 LSB 值右移 1 位。这对于执行正确的 I2C 命令非常重要。这些公式会生成用于 SG1 频率配置的 I2C 命令脚本中的最高有效位 (msb) 和最低有效位 (lsb) 值。

SG1 频率配置是一对 32 位 I2C 命令,向所有输出通道写入单个频率。在这种频率配置中,不隔离任何通道。信号会基于通道选择配置,仅出现在所选的任何输出通道上。请参阅节 2.2。

SG1 在所选的所有通道上保持相同的频率。通常,对于 SG1 和 SG2,所有通道中都维持一种振幅和频率配置。

下面是用于 SG1 频率配置的示例脚本模板。此脚本模板显示了寄存器系数的放置。这是基于上述 h_msb、h_lsb、y_msb 和 y_lsb 公式的结果以及本节末尾的 SG1 示例脚本得出的。

#Based off SG1's 600Hz example script.

#64-bit command from SG1 to OUT1

#w a0 20 [31:24] [23:16] [15:8] [7:0] [31:24] [23:16] [15:8] [7:0]

#64-bit command from SG1 to OUT2

#w a0 28 [31:24] [23:16] [15:8] [7:0] [31:24] [23:16] [15:8] [7:0]

#based off SG1 frequency equations.

#w a0 20 [h_msb] [y_msb ]

#w a0 28 [h_lsb, right shift by 1-bit] [y_lsb, right shift by 1-bit]

#600Hz from SG1.

w a0 20 99 7f ec 00 7f 9a fc b8 #[h_msb] [y_msb]

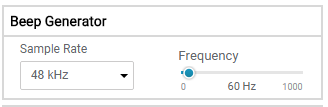

w a0 28 1c ea f1 80 0a 0a f2 99 #[h_lsb] [y_lsb] 在 PPC3 中,SG1频率配置是使用频率滚动 GUI 完成的。图 2-3 是 SG1 频率滚动 GUI 的图像。

图 2-3 SG1 频率配置 GUI

图 2-3 SG1 频率配置 GUI表 2-3 用于 SG1 频率配置的可编程寄存器映射

| 页 | 寄存器 | 说明 |

|---|---|---|

0x12 | 0x20 | 可编程 OUT1 BEEP GEN sin(x) 系数字节 [31:24] |

| 0x12 | 0x21 | 可编程 OUT1 BEEP GEN sin(x) 系数字节 [23:16] |

| 0x12 | 0x22 | 可编程 OUT1 BEEP GEN sin(x) 系数字节 [15:8] |

| 0x12 | 0x23 | 可编程 OUT1 BEEP GEN sin(x) 系数字节 [7:0] |

| 0x12 | 0x24 | 可编程 OUT1 BEEP GEN cos(x) 系数字节 [31:24] |

| 0x12 | 0x25 | 可编程 OUT1 BEEP GEN cos(x) 系数字节 [23:16] |

| 0x12 | 0x26 | 可编程 OUT1 BEEP GEN cos(x) 系数字节 [15:8] |

0x12 | 0x27 | 可编程 OUT1 BEEP GEN cos(x) 系数字节 [7:0] |

| 0x12 | 0x28 | 可编程 OUT2 BEEP GEN sin(x) 系数字节 [31:24] |

| 0x12 | 0x29 | 可编程 OUT2 BEEP GEN sin(x) 系数字节 [23:16] |

| 0x12 | 0x2A | 可编程 OUT2 BEEP GEN sin(x) 系数字节 [15:8] |

| 0x12 | 0x2B | 可编程 OUT2 BEEP GEN sin(x) 系数字节 [7:0] |

| 0x12 | 0x2C | 可编程 OUT2 BEEP GEN cos(x) 系数字节 [31:24] |

| 0x12 | 0x2D | 可编程 OUT2 BEEP GEN cos(x) 系数字节 [23:16] |

| 0x12 | 0x2E | 可编程 OUT2 BEEP GEN cos(x) 系数字节 [15:8] |

| 0x12 | 0x2F | 可编程 OUT2 BEEP GEN cos(x) 系数字节 [7:0] |

# Key: w a0 XX YY ==> write to I2C address 0xa0, to register 0xXX, data 0xYY

# # ==> comment delimiter

#

#The following list gives an example sequence of items that must be #executed in the time between powering the device up and reading data #from the device. Note that there are other valid sequences depending #on which features are used.

#See the corresponding EVM user guide for jumper settings and audio #connections.

#

# Line-Out Fully-Differential 2-channel : OUT1P_M- Ch1, OUT2P_M- Ch2.

# FSYNC = 48 kHz (Output Data Sample Rate), BCLK = 12.288 MHz (BCLK/FSYNC = 256) ###################################################################

#SG1 example script

#SG1; DAC1 OUT1P & OUT1M; Differential 600Hz

w a0 00 00 # locate page x00

w a0 01 01 # device reset

w a0 02 09 # vref and dreg enable

w a0 00 01 # locate page x01

w a0 2d 08 # enable SG1

#Channel selection and amplitude configuration

w a0 00 11 # locate page 0x11

w a0 68 40 00 40 00 # mix SG1 to DAC1 L & R Channels and

# set the amplitude to full-scale, 0dB.

#Frequency configuration

w a0 00 00 # locate page 0x00

w a0 7f 00 # locate book 0x00

w a0 00 12 # locate page 0x12

#600Hz

w a0 20 99 7f ec 00 7f 9a fc b8 #sinx and cosx upper bits

w a0 28 1c ea f1 80 0a 0a f2 99 #sinx and cosx lower bits

#Output configuration

w a0 00 00 # locate page 0x00

#differential mode is the default output mode

#w a0 64 24 #option to set to single-ended mode

w a0 76 0c #enable DAC1, CH 1 & 2 180deg out of phase diff. mode

w a0 78 40 #enable DAC