ZHCAEJ8 October 2024 TAC5412-Q1

3.5 ADSR 包络示例脚本

ADSR 包络示例脚本演示了所有 ADSR 参数的使用。

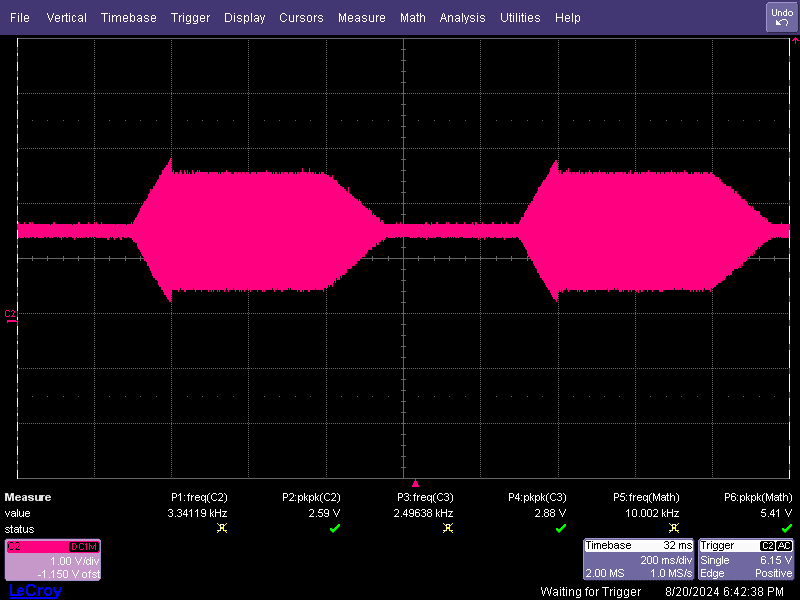

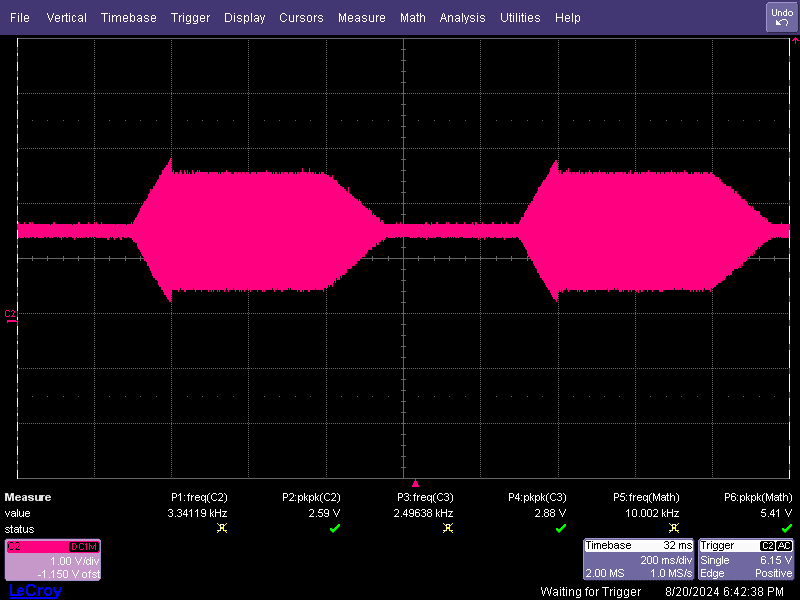

图 3-3 ADSR 包络示波器捕获

图 3-3 ADSR 包络示波器捕获

# Key: w a0 XX YY ==> write to I2C address 0xa0, to register 0xXX, data 0xYY

# # ==> comment delimiter

#

#The following list gives an example sequence of items that must be #executed in the time between powering the device up and reading data #from the device. Note that there are other valid sequences depending #on which features are used.

#See the corresponding EVM user guide for jumper settings and audio #connections.

#

# Line-Out Fully-Differential 2-channel : OUT1P_M- Ch1, OUT2P_M- Ch2.

# FSYNC = 48 kHz (Output Data Sample Rate), BCLK = 12.288 MHz (BCLK/FSYNC = 256) ###################################################################

#ADSR Example Script

#ALL ADSR parameters demonstrated on SG2 CPM

#Note: CPM mode does not require ADSR enable script, only acknowledgement #script.

w a0 00 00 #locate page x00

w a0 01 01 # device reset

w a0 00 00 # locate page 0x00

w a0 02 09 # come out of sleep mode with VREF and DREG up

w a0 00 01 # locate page 0x01

w a0 2d 04 # enable chirp only

w a0 00 17 # locate page 0x17

w a0 7c 14 f1 a6 c6 # 10kHz chirp start frequency

w a0 00 18 #locate page 0x18

w a0 08 00 00 00 00 # chirp delta frequency of 0 Hz

w a0 00 1c # locate page 0x1c

w a0 40 00 00 00 00 # adsr_note

#restart timer

w a0 50 00 00 bb 80 #48k samples for 1s

#sustain timer

w a0 54 00 00 5d c0 #24000 samples at 500ms

#attack timer

w a0 58 00 03 69 cd # 100ms

#release timer

w a0 5c ff fe 4b 18 #200ms @ k = 1.04167e-4. Use full-scale susatin level #to achieve accurate reading.

#sustian level

w a0 64 33 33 33 33 # sustain lvl at k=0.8

#decay timer

w a0 60 ff f2 58 e3 #5ms

#channel selection

w a0 00 11 #locate page 0x11

w a0 70 40 00 40 00 # Please refer the table to set volumes #accrodingly

w a0 74 40 00 40 00 # Please refer the table to set volumes #accordingly

w a0 00 00 # locate page 0x00

w a0 76 0c # enable 2 DAC channels

w a0 78 40 # enable DAC

图 3-3 ADSR 包络示波器捕获

图 3-3 ADSR 包络示波器捕获