ZHCAEJ8 October 2024 TAC5412-Q1

2.2 信号发生器 1 振幅和输出通道

表 2-1 中的寄存器 B0_P17_R104 (0x68) 至 B0_P17_111 (0x6F) 配置振幅电平并选择 SG1 的输出通道。

配置振幅的两种方法是执行 I2C 脚本或使用 PPC3 混音系数。

表 2-1 演示了这两种方法如何以 0.56dB 的增益步长增大或减小振幅。在这里,I2C 脚本要求每个通道具有 16 位寄存器。每种振幅和通道选择配置都需要执行一条 32 位 I2C 命令。

此示例脚本模板将 OUT1 和 OUT2 的每个模拟输出通道置于 32 位 I2C 命令中。该模板也适用于所有 SG2 寄存器。

以 Vrms 为单位的满量程值和以 dB 为单位的最大增益与 0x40000 相关。这组成了 32 位 I2C 命令的 16 位。

#Example template to configure SG1 to OUT1P&M and OUT2P&M. Same format #applies to SG2 registers.

#w a0 68 [OUT1M] [OUT1M] [OUT1P] [OUT1P]

#w a0 6C [OUT2M] [OUT2M] [OUT2P] [OUT2P]

#w xx XX [15:8] [7:0] [15:8] [7:0]

# This is a 32-bit I2C command. Here, OUT1P has full gain while OUT1M has #no gain.

w a0 68 00 00 40 00 SG1 示例脚本中有一个有关使用 I2C 命令进行振幅和通道选择的示例。PPC3 提供的系数范围介于 1 到 0 之间。要通过这些系数预测增益(以 dB 为单位),请使用...

方程式 1.

以 Vrms 为单位的满量程值和以 dB 为单位的最大增益与系数 1 相关。

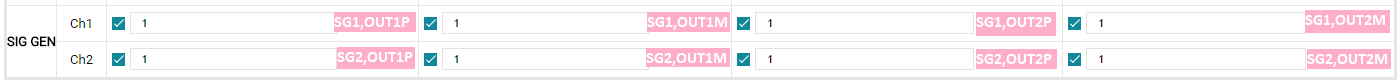

图 2-2 演示了信号发生器如何使用混音系数在 PPC3 中配置振幅。

图 2-2 振幅和输出通道配置 GUI

图 2-2 振幅和输出通道配置 GUI表 2-4 展示了如何导航至音调发生器 GUI。

表 2-1 振幅电平配置

| 十进制值 | 16 位 I2C 命令 | 混音系数 | 增益 dB | Vrms |

|---|---|---|---|---|

| d16384 | 0x4000 | 1 | 0dB | 2Vrms |

| d8192 | 0x2000 | 0.5 | -6dB | 1Vrms |

| d64 | 0x0100 | 0.016 | -35.90dB | - |

| d0 | 0x0000 | - | - | - |

表 2-2 SG1 振幅和输出通道的可编程寄存器映射

| 页 | 寄存器 | 说明 | 复位值 |

|---|---|---|---|

| 0x11 | 0x68 | 侧链 DAC 混频器,SG1 至 OUT1M 系数字节 [15:8] | 0x00 |

| 0x11 | 0x69 | 侧链 DAC 混频器,SG1 至 OUT1M 系数字节 [7:0] | 0x00 |

| 0x11 | 0x6A | 侧链 DAC 混频器,SG1 至 OUT1P 系数字节 [15:8] | 0x00 |

| 0x11 | 0x6B | 侧链 DAC 混频器,SG1 至 OUT1P 系数字节 [7:0] | 0x00 |

| 0x11 | 0x6C | 侧链 DAC 混频器,SG1 至 OUT2M 系数字节 [15:8] | 0x00 |

| 0x11 | 0x6D | 侧链 DAC 混频器,SG1 至 OUT2M 系数字节 [7:0] | 0x00 |

| 0x11 | 0x6E | 侧链 DAC 混频器,SG1 至 OUT2P 系数字节 [15:8] | 0x00 |

| 0x11 | 0x6F | 侧链 DAC 混频器,SG1 至 OUT2P 系数字节 [7:0] | 0x00 |