ZHCAEK7 October 2024 TPLD1201 , TPLD1201-Q1

3 在 InterConnect Studio (ICS) 中配置时序宏单元

振荡器分频器以及计数器宏单元可用于生成各种频率。计数器输出的频率可通过以下公式计算:fout = fclk/(DATA + 1)。复位后,将需要 2 个额外的时钟周期以进行时钟同步。

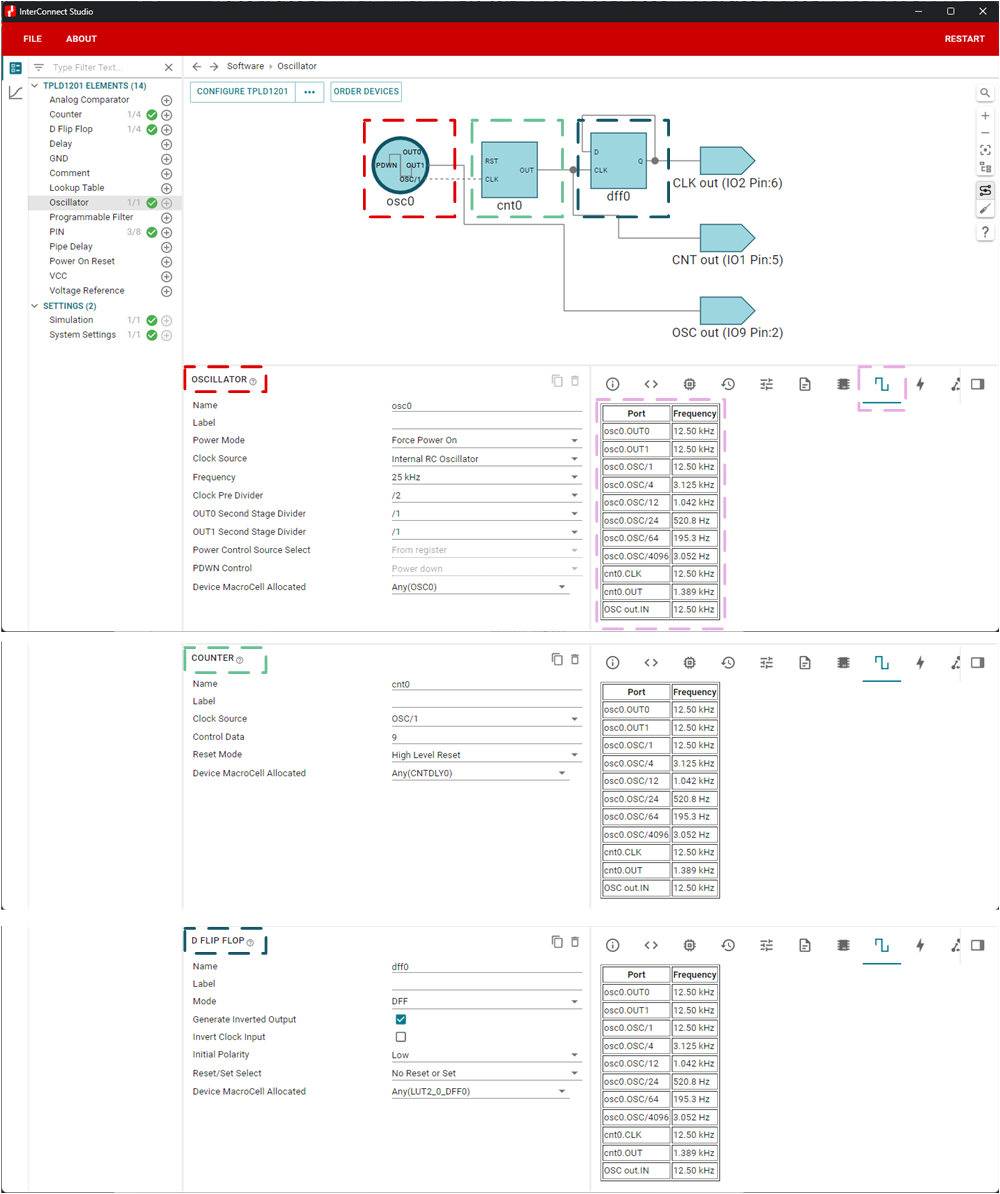

下面图 3-1 中所示的电路(在 InterConnect Studio (ICS) 中配置)显示了一个使用 TPLD1201 中的 25kHz 振荡器生成 50% 占空比的 625Hz 方波的示例。要实现这一点,将振荡器预分频器设置为 2 分频,从而将基础频率更改为 12.5kHz。为生成 1.25kHz 信号,以下是计数器宏单元时钟端口的输入,可通过上述公式计算得出:fout = 12.5kHz/10,其中 fclk = 12.5kHz,DATA = 9。为了实现 50% 占空比,计数器的输出随后馈入 D 型触发器,该触发器将输入频率进一步除以 2,从而生成 625Hz 信号。

图 3-1 InterConnect Studio (ICS) 中的时序分量配置

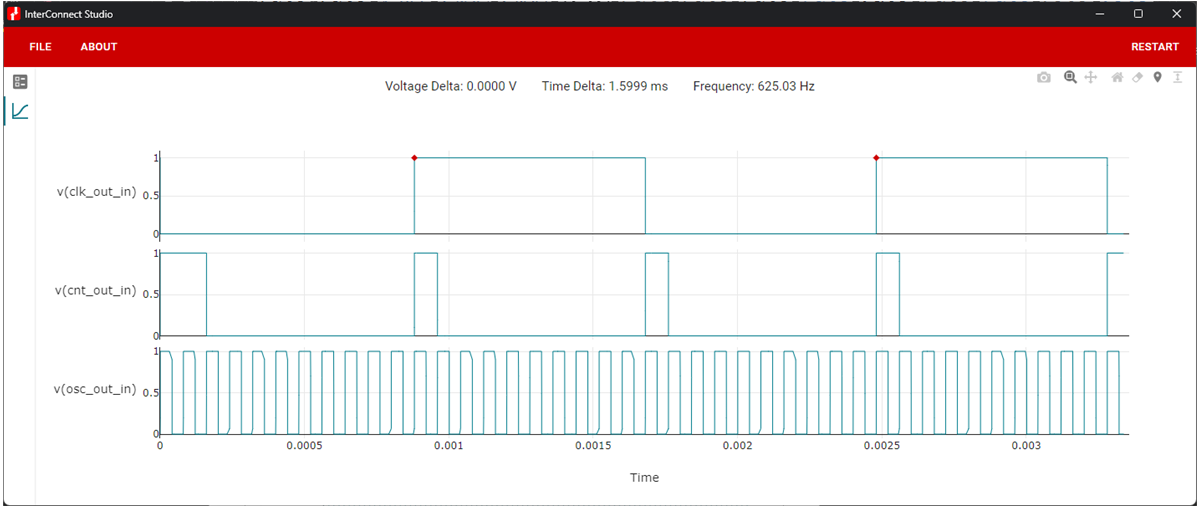

图 3-1 InterConnect Studio (ICS) 中的时序分量配置图 3-2 和图 3-3 分别显示了 ICS 内的电路仿真结果,以及 TPLD1201 中电路的逻辑分析仪捕获结果。

图 3-2 ICS 仿真输出

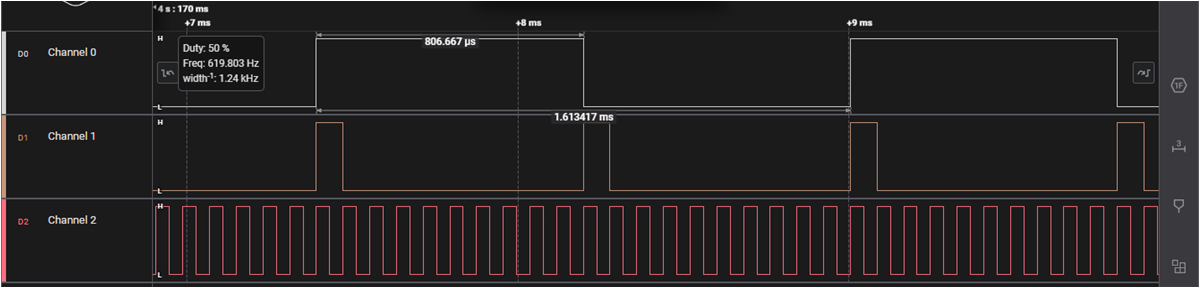

图 3-2 ICS 仿真输出 图 3-3 TPLD1201 输出的逻辑分析仪捕获结果

图 3-3 TPLD1201 输出的逻辑分析仪捕获结果