ZHCAEK7 October 2024 TPLD1201 , TPLD1201-Q1

4 同步信号示例

可以使用延迟发生器宏单元来同步两个信号。延迟发生器将输入信号延迟的时间为 td = (DATA + td_err + 2)/fclk,其中 td_err 为输入和时钟之间相移产生的误差,fclk 为传递到延迟发生器时钟输入端的信号的频率。要正确使用延迟发生器,需要注意的一点是输入信号的脉宽(高电平和低电平)必须大于时钟输入周期的三倍。

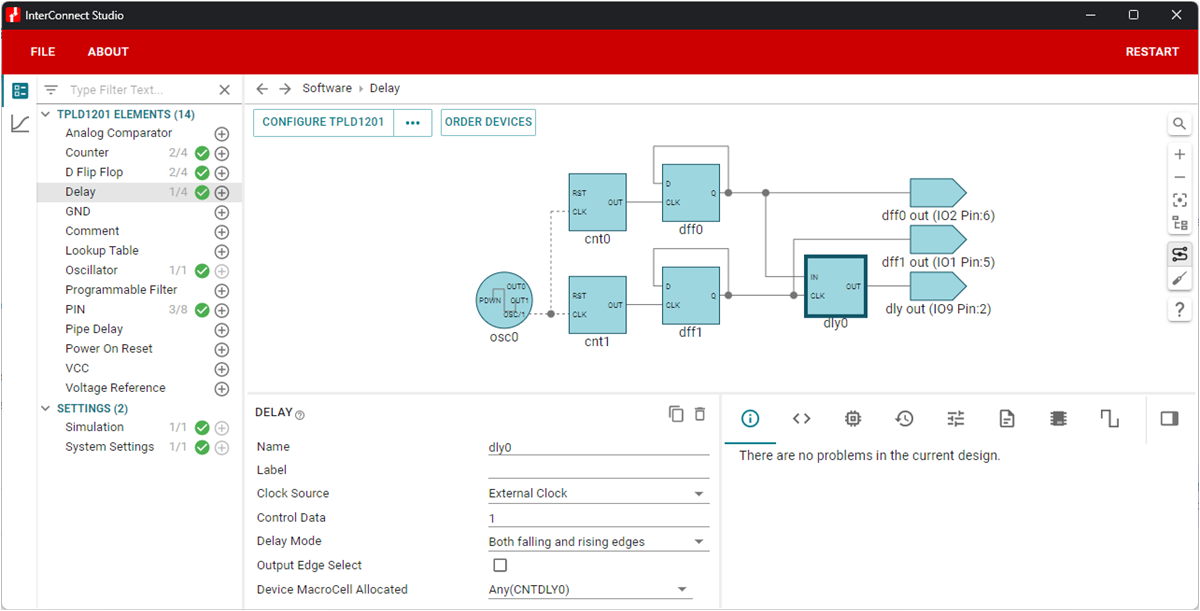

图 4-1 中所示的电路生成两个信号,一个信号的输出频率约为 357Hz,另一个信号的输出频率约为 4.17kHz。较慢信号应路由到延迟发生器的 IN 端口,而较快信号使用“External Clock”选项,应路由到 CLK 端口。

图 4-1 同步信号示例电路

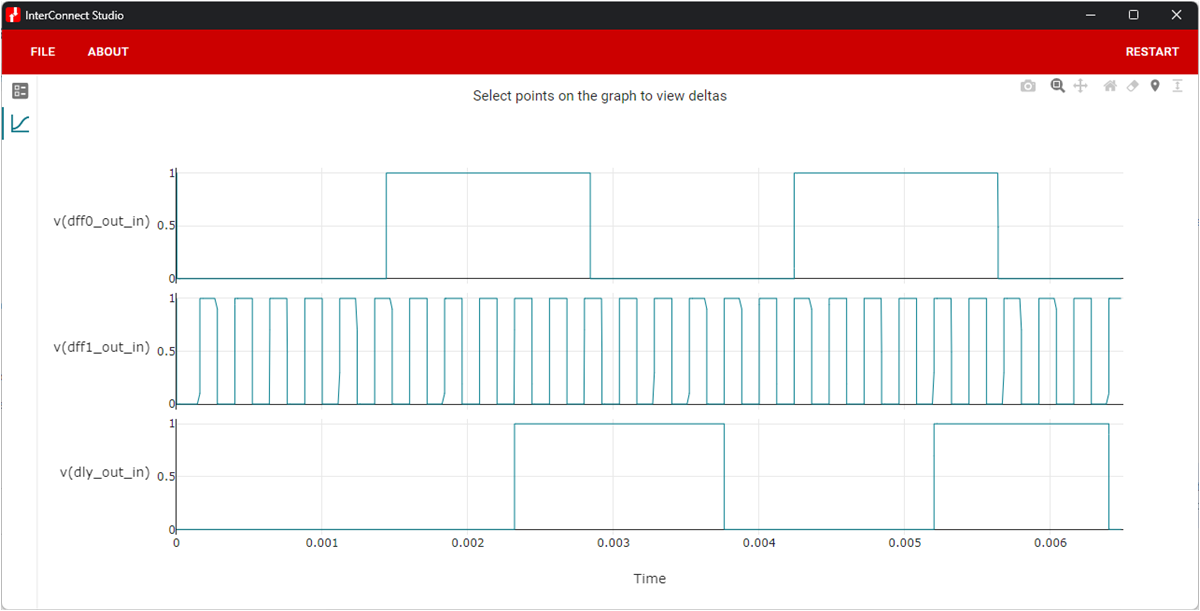

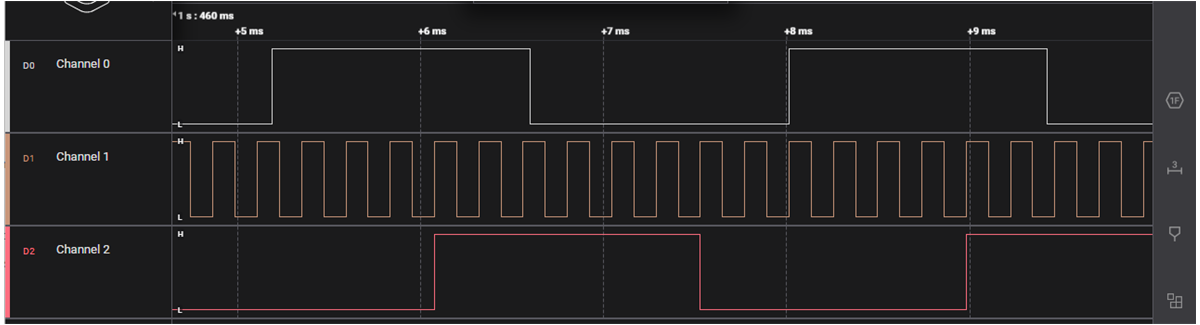

图 4-1 同步信号示例电路ICS 中的仿真结果和 TPLD1201 上测量的逻辑分析仪捕获结果分别如图 4-2 和图 4-3 所示。从图中可以看出,dff0_out 和 dff1_out 信号最初是异步的,随后使用 dly0 将 dff0_out 同步到 dff1_out。注意:如果两个信号的频率不是计算因数,则延迟将导致输入信号轻微失真。

图 4-2 同步信号电路的 ICS 仿真

图 4-2 同步信号电路的 ICS 仿真 图 4-3 同步信号电路的逻辑分析仪捕获结果

图 4-3 同步信号电路的逻辑分析仪捕获结果