ZHCAEN2 October 2024 TPLD1201 , TPLD1201-Q1 , TPLD1202 , TPLD1202-Q1 , TPLD801 , TPLD801-Q1

TI 可编程逻辑器件 (TPLD) 可以配置为单稳态多谐振荡器(也称为单稳态电路),在接收到可变长度的输入触发信号后,会输出固定长度的脉冲信号。图 1 所示的设计利用 TPLD 器件中的内部振荡器、计数器和查找表模块来构建不可重复触发的单稳态电路。

图 1 单稳态电路原理图

图 1 单稳态电路原理图示例配置

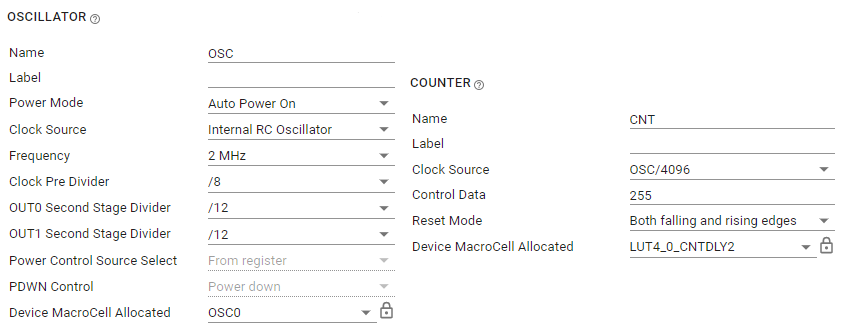

2MHz 振荡器预先经过 8 分频,输出频率为 250kHz。计数器模块(图 1 中的 CNT)进一步对该频率进行 4096 分频,因此在 CLK 输入端由 61Hz 信号进行驱动。计数器模块数据设置为 255,这意味着计数器每 255 个时钟周期输出一个高电平脉冲。在此设计中,计数器模块的输入频率周期为 1 ÷ 61Hz = 16.4ms,这意味着计数器大约每 4.2s 输出一个高电平脉冲。这也意味着在接收到适当的输入触发信号后,输出脉冲宽度将大约为 4.2s。

图 2 振荡器和计数器配置

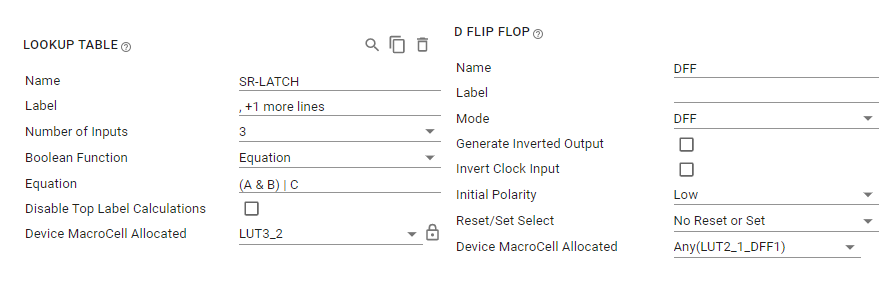

图 2 振荡器和计数器配置计数器模块的输出经过反相并连接到配置为 SR 锁存器的查找表。配置为 SR 锁存器的 LUT 的 C 输入端连接到名为 SET 的输入引脚以提供所需的触发信号。当 SET 输出高电平脉冲时,SR 锁存器将输出高电平,而 DFF 会锁存输入信号并开始输出脉冲信号。DFF 还会复位计数器模块,以便计数器模块必须对来自内部振荡器的所有 255 个时钟周期进行计数。一旦计数器从内部振荡器接收到 255 个时钟周期,该模块就会发出高电平脉冲,使 SR 锁存器复位 DFF,直到 SET 引脚接收到另一个高电平脉冲。

图 3 DFF 和 LUT(SR 锁存器)配置

图 3 DFF 和 LUT(SR 锁存器)配置设计注意事项

- 输出脉冲宽度可以使用公式(计数器数据 × tCNT)计算得出,其中 tCNT 等于计数器 CLK 输入的周期,即(1 ÷ 计数器时钟频率)。在上述设计中,计数器时钟频率为 61Hz,tCNT 为 16.4ms

- 输入脉冲宽度必须大于 3tCNT 才能触发单稳态,因为复位时计数器模块会在接下来的两个传入时钟周期内发出高电平脉冲

- TPLD 振荡器的精度为 ±5%,输出脉宽可能因器件而具有很大差异。如果需要生成精密脉冲,请考虑通过晶体振荡器提供外部时钟信号

- 如果使用按钮或其他噪声输入信号来触发脉冲,请将输入引脚配置为施密特触发输入,并提供外部 RC 滤波器,以防触发不必要的脉冲

- 是否需要其他帮助?请在 TI E2E™ 逻辑支持论坛 中向我们的工程师提问