ZHCAEO8B March 2022 – November 2024 AM620-Q1 , AM623 , AM625 , AM625-Q1

- 1

- 摘要

- 商标

- 1概述

- 2DDR4 电路板设计和布局布线指南

- 3LPDDR4 电路板设计和布局布线指南

- 4LPDDR4 电路板设计仿真

- 5附录:AM62x ALW 和 AMC 封装延迟

- 6修订历史记录

4.4 时域反射法 (TDR) 分析

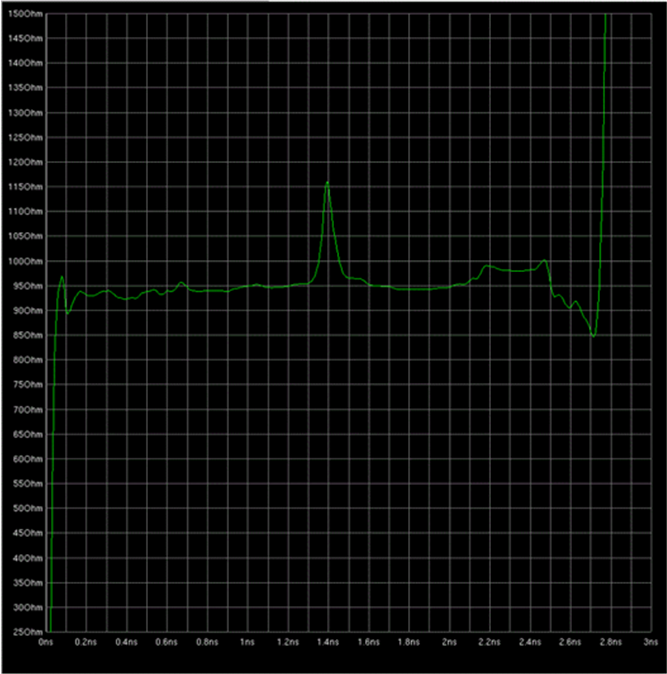

许多设计修正旨在保持一致的布线阻抗,因此时域反射法 (TDR) 分析是用于评估设计质量的一种重要分析方法。下面绘制了布线阻抗与布线长度之间的函数关系,如图 4-1 所示。

图 4-1 阻抗不匹配的 TDR 图示例

图 4-1 阻抗不匹配的 TDR 图示例如图 4-1 所示,TDR 图突出显示了布线中从一端到另一端的阻抗不连续性。此方法依赖于来自布线远端的反射波形。由于存在往返时间,图中对应于布线中特定点的延迟实际上相当于该点到源的距离的 2 倍。在评估阻抗不连续性的原因时需要考虑到这一点。

可通过读取由提取工具生成的 S 参数模型并在“时域”模式下对其进行评估来生成 TDR 图。HyperLynx 等标准 EDA 仿真器可以执行此功能。建议优化设计,使其与标称布线阻抗的偏差处于 ±5% 以内。

TDR 图不是通过/失败测试,而是侧重于为检查设计是否有合理机会实现所需性能提供指南。