ZHCAEO8B March 2022 – November 2024 AM620-Q1 , AM623 , AM625 , AM625-Q1

- 1

- 摘要

- 商标

- 1概述

- 2DDR4 电路板设计和布局布线指南

- 3LPDDR4 电路板设计和布局布线指南

- 4LPDDR4 电路板设计仿真

- 5附录:AM62x ALW 和 AMC 封装延迟

- 6修订历史记录

4.5.3.3 模板报告

将捕获与眼图模板相关的最小抖动和噪声容限。这些模板依赖于数据速率,包括:

- 用于功能测试的 SOC 芯片焊盘上的数据读取眼图模板

- DRAM 引脚/BGA 上用于合规性测试的数据写入眼图模板(JEDEC 规格)

- DRAM 引脚/BGA 上用于合规性测试的 CA 总线眼图模板(JEDEC 规格)

仿真器应至少生成 2 组眼图:

- Vref 设置为正方向 Vref_set_tol 字节偏移的最佳 Vref(JEDEC 规范中定义了 Vref_set_tol)

- Vref 设置为负方向 Vref_set_tol 字节偏移的理想 Vref

系统级裕量是上面列出的所有眼图测量中最坏情况下的噪声和抖动裕量(跨 SSHT 和 FFLT 角)。对于在 DRAM 器件上捕获的所有波形,应在 BGA 引脚和 DRAM 焊盘上计算裕度。

表 4-3 LPDDR4 眼图模板定义/要求

| 参数 | 模板形状 | LPDDR4-1600 | LPDDR4-3200 | LPDDR4-3733 |

|---|---|---|---|---|

| CA 眼图模板 TcIVW | 矩形 (1) | 0.3 UI | 0.3UI (1) | (2) |

| CA 眼图模板 VcIVW | 矩形 (1) | 175mV | 155mV (1) | (2) |

| 写入眼图模板 TdIVW | 矩形 (1) | 0.22 UI | 0.25UI (1) | (2) |

| 写入眼图模板 VdIVW | 矩形 (1) | 140mV | 140mV (1) | (2) |

| 读取眼图模板 TdIVW | 菱形 | 0.42 UI | 0.61UI | 0.66UI |

| 读取眼图模板 VdIVW | 菱形 | 140mV | 140mV | 140mV |

(1) 从 JEDEC 规范复制:低功耗双倍数据速率 4 (LPDDR4)。

(2) 相关详细信息,请联系 DRAM 供应商。

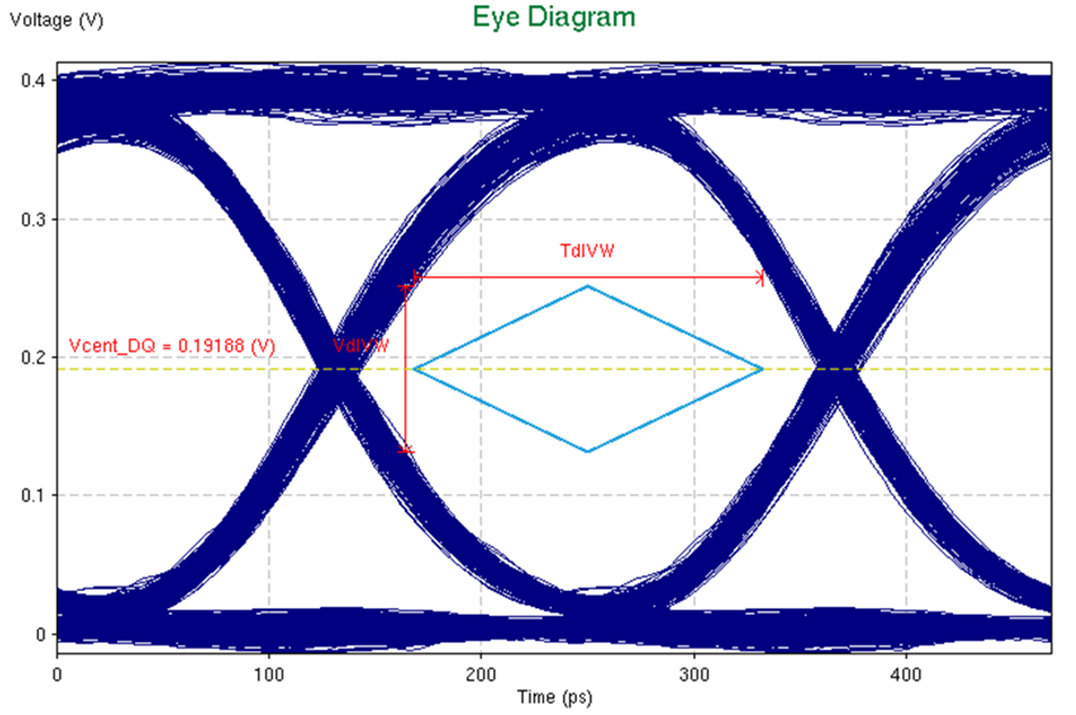

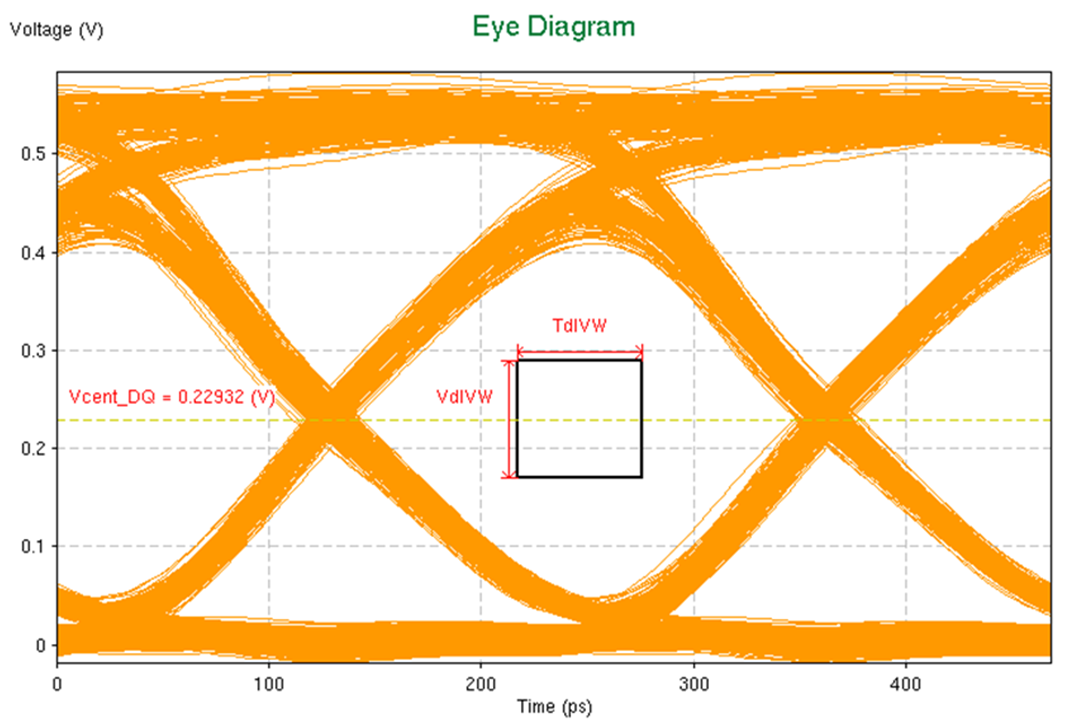

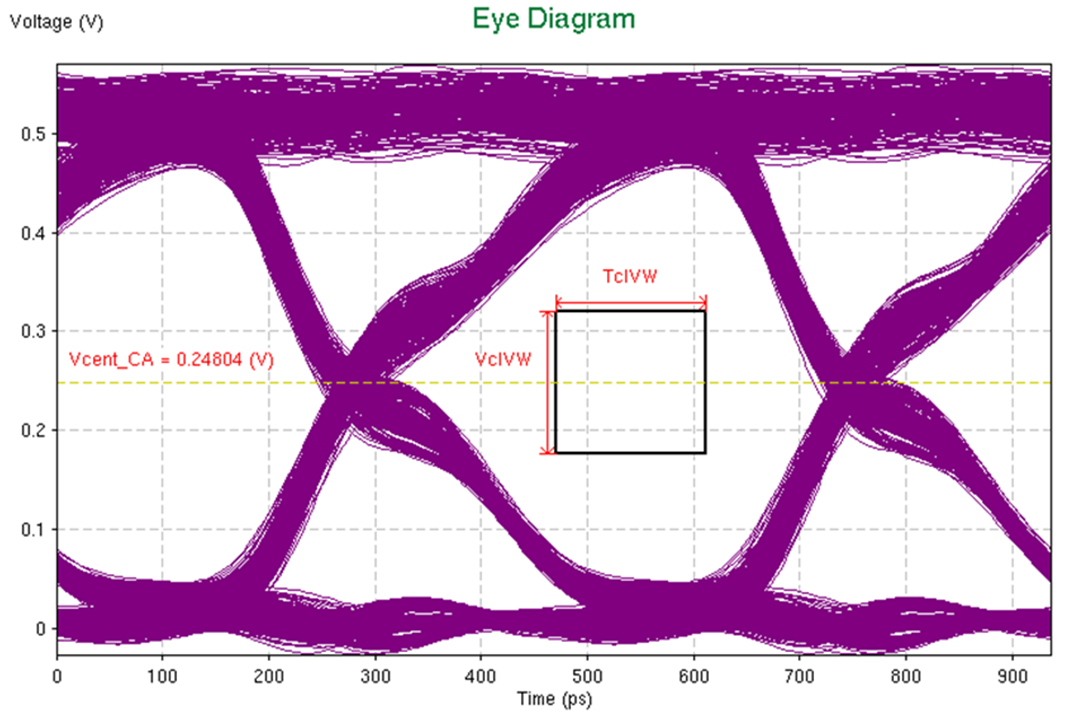

图 4-4 至图 4-6 显示了所捕获的波形中转换为眼图的眼图模板定义。

图 4-4 具有菱形眼图模板的示例仿真 LPDDR4-4266 读取眼图

图 4-4 具有菱形眼图模板的示例仿真 LPDDR4-4266 读取眼图 图 4-5 具有矩形 JEDEC 眼图模板的示例仿真 LPDDR4-4266 写入眼图

图 4-5 具有矩形 JEDEC 眼图模板的示例仿真 LPDDR4-4266 写入眼图 图 4-6 具有矩形 JEDEC 眼图模板的示例仿真 LPDDR4-4266 CA 眼图

图 4-6 具有矩形 JEDEC 眼图模板的示例仿真 LPDDR4-4266 CA 眼图