ZHCS234B August 2012 – January 2016 PCM5141 , PCM5142

PRODUCTION DATA.

- 1 特性

- 2 应用

- 3 说明

- 4 修订历史记录

- 5 Device Comparison

- 6 Pin Configuration and Functions

-

7 Specifications

- 7.1 Absolute Maximum Ratings

- 7.2 ESD Ratings

- 7.3 Recommended Operating Conditions

- 7.4 Thermal Information

- 7.5 Electrical Characteristics

- 7.6 Timing Requirements: SCK Input

- 7.7 Timing Requirements: PCM Audio Data

- 7.8 Timing Requirements: I2S Master

- 7.9 Timing Requirements: XSMT

- 7.10 Switching Characteristics

- 7.11 Typical Characteristics

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3

Feature Description

- 8.3.1 Terminology

- 8.3.2 Audio Data Interface

- 8.3.3 XSMT Pin (Soft Mute / Soft Un-Mute)

- 8.3.4 Audio Processing

- 8.3.5 DAC Outputs

- 8.3.6

Reset and System Clock Functions

- 8.3.6.1 Clocking Overview

- 8.3.6.2 Clock Slave Mode With Master and System Clock (SCK) Input (4 Wire I2S)

- 8.3.6.3 Clock Slave Mode With BCK PLL to Generate Internal Clocks (3-Wire PCM)

- 8.3.6.4 Clock Generation Using the PLL

- 8.3.6.5 PLL Calculation

- 8.3.6.6 Clock Master Mode from Audio Rate Master Clock

- 8.3.6.7 Clock Master from a Non-Audio Rate Master Clock

- 8.4 Device Functional Modes

- 8.5 Programming

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Register Maps

- 13器件和文档支持

- 14机械、封装和可订购信息

8 Detailed Description

8.1 Overview

The integrated PLL on the device provided adds the flexibility to remove the system clock (commonly known as master clock), allowing a 3-wire I2S connection and reducing system EMI. In addition, the PLL is completely programmable, allowing the device to become the I2S clock master and drive a DSP serial port as a slave. The PLL also accepts a non-standard clock (up to 50 MHz) as a source to generate the audio related clock (for example, 24.576 MHz).

Powersense undervoltage protection utilizes a two-level mute system. Upon clock error or system power failure, the device digitally attenuates the data (or last known good data) and then mutes the analog circuit.

Compared with existing DAC technology, the PCM514x devices offer up to 20-dB lower out-of-band noise, reducing EMI and aliasing in downstream amplifiers/ADCs (from traditional 100-kHz OBN measurements to

3 MHz).

The PCM514x devices accept industry-standard audio data formats with 16- to 32-bit data. Sample rates up to 384 kHz are supported.

8.2 Functional Block Diagram

8.3 Feature Description

8.3.1 Terminology

Control registers in this data sheet are given by REGISTER BIT/BYTE NAME (Page.x HEX ADDRESS). SE refers to single-ended analog inputs. SCK (System Clock) and MCLK (Master Clock) are used interchangeably. Sampling frequency is symbolized by fS. Full scale is symbolized by FS. Sample time as a unit is symbolized by tS.

8.3.2 Audio Data Interface

8.3.2.1 Audio Serial Interface

The audio interface port is a 3-wire serial port with the signals LRCK, BCK, and DIN. BCK is the serial audio bit clock, used to clock the serial data present on DIN into the serial shift register of the audio interface. Serial data is clocked into the PCM514x on the rising edge of BCK. LRCK is the serial audio left/right word clock. LRCK polarity for left/right is given by the format selected.

Table 4. PCM514x Audio Data Formats, Bit Depths and Clock Rates

| CONTROL MODE | FORMAT | DATA BITS | MAX LRCK FREQUENCY [fS] | SCK RATE [x fS] | BCK RATE [x fS] |

|---|---|---|---|---|---|

| Software Control (SPI or I2S) |

I2S/LJ | 32, 24, 20, 16 | Up to 192 kHz | 128 – 3072 | 64, 48, 32 |

| 384 kHz | 64, 128 | 64, 48, 32 | |||

| TDM/DSP | 32, 24, 20, 16 | Up to 48 kHz | 128 – 3072 | 128, 256 | |

| 96 kHz | 128 – 512 | 128, 256 | |||

| 192 kHz | 128, 192, 256 | 128 | |||

| Hardware Control | I2S/LJ | 32, 24, 20, 16 | Up to 192 kHz | 128 – 3072 | 64, 48, 32 |

| 384 kHz | 64, 128 | 64, 48, 32 |

The PCM514x requires the synchronization of LRCK and system clock, but does not need a specific phase relation between LRCK and system clock.

If the relationship between LRCK and system clock changes more than ±5 SCK, internal operation (using an onchip oscillator) is initialized within one sample period and analog outputs are forced to the bipolar zero level until resynchronization between LRCK and system clock is completed.

If the relationship between LRCK and BCK are invalid more than 4 LRCK periods, internal operation (using an onchip oscillator) is initialized within one sample period and analog outputs are forced to the bipolar zero level until resynchronization between LRCK and BCK is completed.

8.3.2.2 PCM Audio Data Formats

The PCM514x supports industry-standard audio data formats, including standard I2S and left-justified. Data formats are selected via Register (Pg0Reg40). All formats require binary twos-complement, MSB-first audio data; up to 32-bit audio data is accepted.

The PCM514x also supports right-justified and TDM/DSP in software control mode. I2S, LJ, RJ, and TDM/DSP are selected using Register (Pg0Reg40). All formats require binary twos-complement, MSB-first audio data. Up to 32 bits are accepted. Default setting is I2S and 24-bit word length.

Figure 15. Left-Justified Audio Data Format

Figure 15. Left-Justified Audio Data Format

The following data formats are only available in software mode.

NOTE

In TDM Modes, Duty Cycle of LRCK should be 1x BCK at minimum. Rising edge is considered frame start.

8.3.2.3 Zero Data Detect

The PCM514x has a zero-detect function. When the device detects the continuous zero data for both left and right channels, or separate channels, Analog mutes are set to both OUTL and OUTR, or separate OUTL and OUTR. These are controlled by Page 0, Register 65, D(2:1) as shown in Table 5.

Continuous Zero data cycles are counted by LRCK, and the threshold of decision for analog mute can be set by Page 0, Register 59, D(6:4) for L-ch, and D(2:0) for Rch as shown in Table 6. Default values are 0 for both channels.

In Hardware mode, the device uses default values. By default, Both L-ch and R-ch have to be zero data for zero data detection to begin the muting process etc.

Table 5. Zero Data Detection Mode

| ATMUTECTL | VALUE | FUNCTION |

|---|---|---|

| Bit : 2 | 0 | Independently L-ch or R-ch are zero data for zero data detection |

| 1 (Default) | Both L-ch and R-ch have to be zero data for zero data detection | |

| Bit : 1 | 0 | Zero detection and analog mute are disabled for R-ch |

| 1 (Default) | Zero detection analog mute are enabled for R-ch | |

| Bit : 0 | 0 | Zero detection analog mute are disabled for L-ch |

| 1 (Default) | Zero detection analog mute are enabled for L-ch |

Table 6. Zero Data Detection Time

| ATMUTETIML / ATMUTETIMR | NUMBER OF LRCKs | TIME AT 48 kHz |

|---|---|---|

| 0 0 0 | 1024 | 21 ms |

| 0 0 1 | 5120 | 106 ms |

| 0 1 0 | 10240 | 213 ms |

| 0 1 1 | 25600 | 533 ms |

| 1 0 0 | 51200 | 1.066 sec |

| 1 0 1 | 102400 | 2.133 sec |

| 1 1 0 | 256000 | 5.333 sec |

| 1 1 1 | 512000 | 10.66 sec |

8.3.3 XSMT Pin (Soft Mute / Soft Un-Mute)

An external digital host controls the PCM514x soft mute function by driving the XSMT pin with a specific minimum rise time (tr) and fall time (tf) for soft mute and soft un-mute. The PCM514x requires tr and tf times of less than 20 ns. In the majority of applications, this is no problem; however, traces with high capacitance may have issues.

When the XSMT pin is shifted from high to low (3.3 V to 0 V), a soft digital attenuation ramp begins. –1-dB attenuation is then applied every sample time from 0 dBFS to –∞. The soft attenuation ramp takes 104 samples.

When the XSMT pin is shifted from low to high (0 V to 3.3 V), a soft digital un-mute is started. 1-dB gain steps are applied every sample time from –∞ to 0 dBFS. The un-mute takes 104 samples.

In systems where XSMT is not required, it can be directly connected to AVDD.

8.3.4 Audio Processing

8.3.4.1 PCM514x Audio Processing Options

8.3.4.1.1 Overview

The PCM514x features a fully-programmable miniDSP core. The algorithms for the miniDSP must be loaded into the device after power up. The miniDSP has direct access to the digital stereo audio stream, offering the possibility for advanced DSP algorithms with very low group delay. The miniDSP can run up to 1024 instructions on every audio sample at a 48-kHz sample rate.

NOTE

At higher sampling frequencies, fewer instruction cycles are available. (For example, 512 instructions can be done in a 96-kHz frame.)

The PCM514x supports two different code sources. ROM based process flow (See the next section for how to select) and RAM based process flow. In program 31 (RAM based), different algorithms can be called from ROM - such as EQ, DRC and Zero Crossing volume control. Please see the PurePath Studio Development Environment for more details.

8.3.4.1.2 miniDSP Instruction Register

Registers on Page 152-169 are 25-bit instructions for the miniDSP engine. For details, see Table 53. 7 bits of Instr(32:25) in Base register +0 are reserved bits. 1 bit of Instr(24) - (LSB) in Base register +0 is MSB bit of 25 bit instruction. These instructions control miniDSP operation. When the fully programmable miniDSP mode is enabled and the DAC channel is powered up, the read and write access to these registers is disabled.

8.3.4.1.3 Digital Output

The PCM514x supports an SDOUT output. This can be selected within the process flow, and driven out of a GPIO pin selected in the register map (for example, Page 0 / Register 80). Users should note that the I2S output will be attenuated by 0.5 dB. A full scale (FS) output will actually be FS-0.5dB. This can be compensated for within the process flow using PurePath Studio. The I2S output can be a separate audio stream to the analog DAC output, allowing 2.1 and 2.2 systems to be implimented. By default, the SDOUT is not linked to the volume control registers on Page 0 / Register 60, 61, 62. However, it is possible to configure the SDOUT component in Purepath studio to mirror that register.

8.3.4.1.4 Software

Software development for the PCM514x is supported through TI's comprehensive PurePath ™Studio; a powerful, easy-to-use tool designed specifically to simplify software development on the PCM514x miniDSP audio platform.

Please visit the PCM514x product folder on www.ti.com to learn more about PurePath Console and the latest status on available, ready-to-use DSP algorithms.

8.3.4.2 Interpolation Filter

The PCM514x provides 4 types of interpolation filters, selectable by writing to Page 0, Register 43, D(4:0).

Additional RAM based Hybrid Flows can be implemented by selecting Program 31, and downloading instructions and coefficients to the device.

Table 7. ROM Preset Programs

| PROGRAM NUMBER | D(4:0) | DESCRIPTION | MINIMUM CYCLES |

|---|---|---|---|

| 0 | 0 0000 | Reserved | |

| 1 | 0 0001 | Normal x8/x4/x2/x1 Interpolation Filter(1) | 256 |

| 2 | 0 0010 | Low Latency x8/x4/x2/x1 Interpolation Filter(1) | 256 |

| 3 | 0 0011 | High Attenuation x8/x4/x2 Interpolation Filter(1) | 512 |

| 4 | 0 0100 | Reserved | |

| 5 | 0 0101 | Preset Process Flow | |

| 6 | 0 0110 | Reserved | |

| 7 | 0 0111 | Asymmetric FIR Interpolation Filter(1) | 512 |

| : | : | Reserved | |

| 31 | 1 1111 | RAM program / Hybrid Flows |

The PCM514x supports four sampling modes (single rate, dual rate, quad rate, and octal rate) which produce different oversampling rates (OSR) in the interpolation digital filter operation. These are shown in Table 8.

Table 8. Sampling Modes and Oversampling Rates

| SAMPLING MODE | SAMPLING FREQUENCY (fS) kHz | OVERSAMPLING RATE (OSR) |

|---|---|---|

| Single Rate | 8 | 8 or 16 |

| 16 | ||

| 32 | ||

| 44.1 | ||

| 48 | ||

| Dual Rate | 88.2 | 4 |

| 96 | ||

| Quad Rate | 176.4 | 2 |

| 192 | ||

| Octal Rate | 384 | 1 (Bypass) |

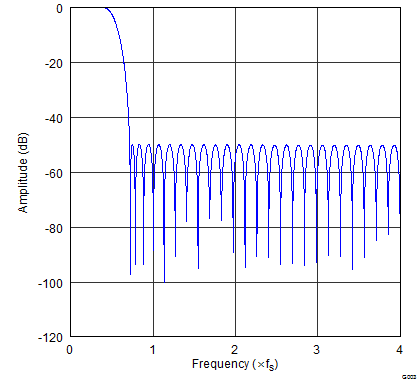

Table 9. Normal x8 Interpolation Filter, Single Rate

| PARAMETER | CONDITION | VALUE (TYP) | VALUE (MAX) | UNIT |

|---|---|---|---|---|

| Filter Gain Pass Band | 0 ……. 0.45 × fS | ±0.01 | dB | |

| Filter Gain Stop Band | 0.55 × fS ….. 7.455 × fS | -60 | dB | |

| Filter Group Delay | 20 × ts | S |

SPACE

Figure 21. Normal x8 Interpolation Filter

Figure 21. Normal x8 Interpolation Filter Frequency Response

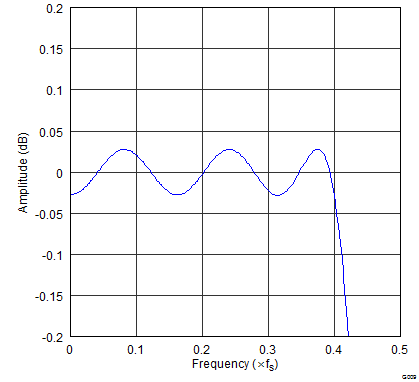

Figure 23. Normal x8 Interpolation Filter Passband Ripple

Figure 23. Normal x8 Interpolation Filter Passband Ripple

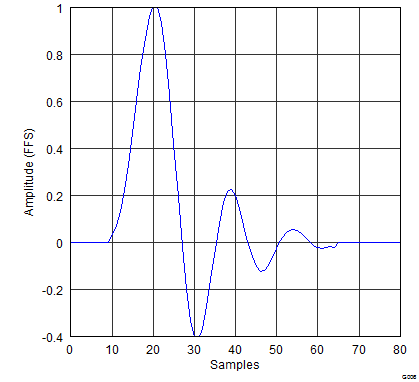

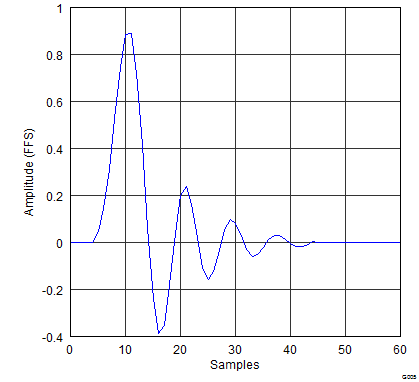

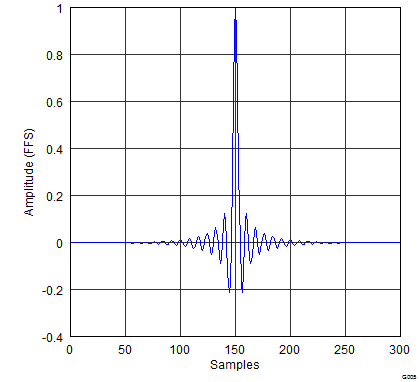

Figure 22. Normal x8 Interpolation Filter

Figure 22. Normal x8 Interpolation Filter Impulse Response

Table 10. Normal x4 Interpolation Filter, Dual Rate

| PARAMETER | CONDITION | VALUE (TYP) | VALUE (MAX) | UNIT |

|---|---|---|---|---|

| Filter Gain Pass Band | 0 ……. 0.45 × fS | ±0.01 | dB | |

| Filter Gain Stop Band | 0.55 × fS ….. 3.455 × fS | -60 | dB | |

| Filter Group Delay | 20 × ts | S |

SPACE

Figure 24. Normal x4 Interpolation Filter

Figure 24. Normal x4 Interpolation Filter Frequency Response

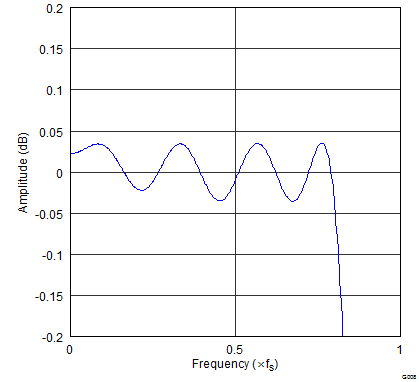

Figure 26. Normal x4 Interpolation Filter Passband Ripple

Figure 26. Normal x4 Interpolation Filter Passband Ripple

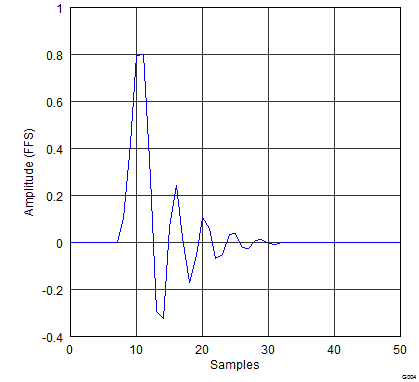

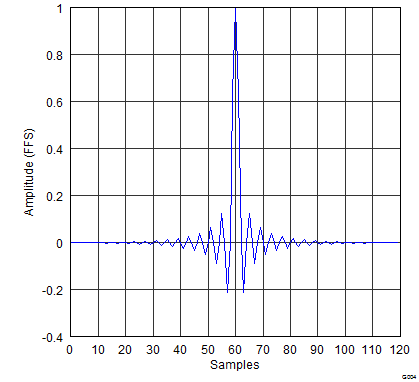

Figure 25. Normal x4 Interpolation Filter

Figure 25. Normal x4 Interpolation Filter Impulse Response

Table 11. Normal x2 Interpolation Filter, Quad Rate

| PARAMETER | CONDITION | VALUE (TYP) | VALUE (MAX) | UNIT |

|---|---|---|---|---|

| Filter Gain Pass Band | 0 ……. 0.45 × fS | ±0.01 | dB | |

| Filter Gain Stop Band | 0.55 × fS ….. 1.455 × fS | -60 | dB | |

| Filter Group Delay | 20 × ts | S |

SPACE

Figure 27. Normal x2 Interpolation Filter

Figure 27. Normal x2 Interpolation Filter Frequency Response

Figure 29. Normal x2 Interpolation Filter Passband Ripple

Figure 29. Normal x2 Interpolation Filter Passband Ripple

Figure 28. Normal x2 Interpolation Filter

Figure 28. Normal x2 Interpolation Filter Impulse Response

Table 12. Low Latency x8 Interpolation Filter, Single Rate

| PARAMETER | CONDITION | VALUE (TYP) | VALUE (MAX) | UNIT |

|---|---|---|---|---|

| Filter Gain Pass Band | 0 ……. 0.45 × fS | ±0.001 | dB | |

| Filter Gain Stop Band | 0.55 × fS ….. 7.455 × fS | -52 | dB | |

| Filter Group Delay | 3.5 × ts | S |

SPACE

Figure 30. Low Latency x8 Interpolation Filter

Figure 30. Low Latency x8 Interpolation Filter Frequency Response

Figure 32. Low Latency x8 Interpolation Filter Passband Ripple

Figure 32. Low Latency x8 Interpolation Filter Passband Ripple

Figure 31. Low Latency x8 Interpolation Filter

Figure 31. Low Latency x8 Interpolation Filter Impulse Response

Table 13. Low Latency x4 Interpolation Filter, Dual Rate

| PARAMETER | CONDITION | VALUE (TYP) | VALUE (MAX) | UNIT |

|---|---|---|---|---|

| Filter Gain Pass Band | 0 ……. 0.45 × fS | ±0.001 | dB | |

| Filter Gain Stop Band | 0.55 × fS ….. 3.455 × fS | -52 | dB | |

| Filter Group Delay | 3.5 × ts | S |

SPACE

Figure 33. Low Latency x4 Interpolation Filter

Figure 33. Low Latency x4 Interpolation Filter Frequency Response

Figure 35. Low Latency x4 Interpolation Filter Passband Ripple

Figure 35. Low Latency x4 Interpolation Filter Passband Ripple

Figure 34. Low Latency x4 Interpolation Filter

Figure 34. Low Latency x4 Interpolation Filter Impulse Response

Table 14. Low Latency ×2 Interpolation Filter, Quad Rate

| PARAMETER | CONDITION | VALUE (TYP) | VALUE (MAX) | UNIT |

|---|---|---|---|---|

| Filter Gain Pass Band | 0 ……. 0.45 × fS | ±0.001 | dB | |

| Filter Gain Stop Band | 0.55 × fS ….. 1.455 × fS | -52 | dB | |

| Filter Group Delay | 3.5 × ts | S |

SPACE

Figure 36. Low Latency x2 Interpolation Filter

Figure 36. Low Latency x2 Interpolation Filter Frequency Response

Figure 38. Low Latency x2 Interpolation Filter Passband Ripple

Figure 38. Low Latency x2 Interpolation Filter Passband Ripple

Figure 37. Low Latency x2 Interpolation Filter

Figure 37. Low Latency x2 Interpolation Filter Impulse Response

Table 15. Asymmetric FIR x8 Interpolation Filter, Single Rate

| PARAMETER | CONDITION | VALUE (TYP) | VALUE (MAX) | UNIT |

|---|---|---|---|---|

| Filter Gain Pass Band | 0 ……. 0.40 × fS | ±0.05 | dB | |

| Filter Gain Stop Band | 0.72 × fS ….. 7.28 × fS | –50 | dB | |

| Filter Group Delay | 1.2 × ts | S |

SPACE

Figure 39. Asymmetric FIR x8 Interpolation Filter Frequency Response, Single Rate

Figure 39. Asymmetric FIR x8 Interpolation Filter Frequency Response, Single Rate

Figure 41. Asymmetric FIR x8 Interpolation Filter Passband Ripple, Single Rate

Figure 41. Asymmetric FIR x8 Interpolation Filter Passband Ripple, Single Rate

Figure 40. Asymmetric FIR x8 Interpolation Filter Impulse Response, Single Rate

Figure 40. Asymmetric FIR x8 Interpolation Filter Impulse Response, Single Rate

Table 16. Asymmetric FIR x4 Interpolation Filter, Dual Rate

| PARAMETER | CONDITION | VALUE (TYP) | VALUE (MAX) | UNIT |

|---|---|---|---|---|

| Filter Gain Pass Band | 0 ……. 0.40 × fS | ±0.05 | dB | |

| Filter Gain Stop Band | 0.72 × fS ….. 3.28 × fS | –50 | dB | |

| Filter Group Delay | 1.2 × ts | S |

SPACE

Figure 42. Asymmetric FIR x4 Interpolation Filter Frequency Response, Dual Rate

Figure 42. Asymmetric FIR x4 Interpolation Filter Frequency Response, Dual Rate

Figure 44. Asymmetric x4 Interpolation Filter Passband Ripple, Dual Rate

Figure 44. Asymmetric x4 Interpolation Filter Passband Ripple, Dual Rate

Figure 43. Asymmetric FIR x4 Interpolation Filter Impulse Response, Dual Rate

Figure 43. Asymmetric FIR x4 Interpolation Filter Impulse Response, Dual Rate

Table 17. Asymmetric FIR x2 Interpolation Filter, Quad Rate

| PARAMETER | CONDITION | VALUE (TYP) | VALUE (MAX) | UNIT |

|---|---|---|---|---|

| Filter Gain Pass Band | 0 ……. 0.40 × fS | ±0.05 | dB | |

| Filter Gain Stop Band | 0.72 × fS ….. 1.28 × fS | –50 | dB | |

| Filter Group Delay | 1.2 × ts | S |

SPACE

Figure 45. Asymmetric FIR x2 Interpolation Filter Frequency Response, Quad Rate

Figure 45. Asymmetric FIR x2 Interpolation Filter Frequency Response, Quad Rate

Figure 47. Asymmetric x2 Interpolation Filter Passband Ripple, Quad Rate

Figure 47. Asymmetric x2 Interpolation Filter Passband Ripple, Quad Rate

Figure 46. Asymmetric FIR x2 Interpolation Filter Impulse Response, Quad Rate

Figure 46. Asymmetric FIR x2 Interpolation Filter Impulse Response, Quad Rate

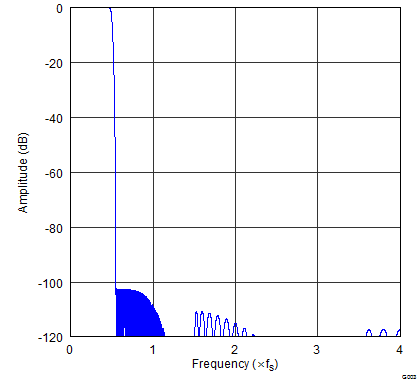

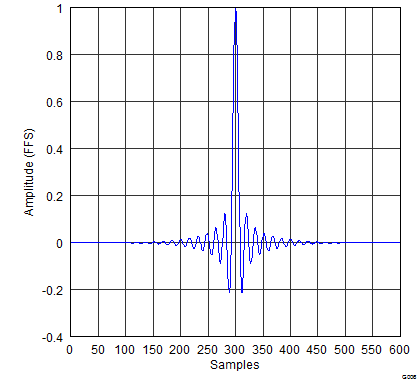

Table 18. High-Attentuation x8 Interpolation Filter, Single Rate

| PARAMETER | CONDITION | VALUE (TYP) | VALUE (MAX) | UNIT |

|---|---|---|---|---|

| Filter Gain Pass Band | 0 ……. 0.45 × fS | ±0.0005 | dB | |

| Filter Gain Stop Band | 0.55 × fS ….. 7.455 × fS | –100 | dB | |

| Filter Group Delay | 33.7 × tS | S |

SPACE

Figure 48. High-Attentuation x8 Interpolation Filter Frequency Response, Single Rate

Figure 48. High-Attentuation x8 Interpolation Filter Frequency Response, Single Rate

Figure 50. High-Attentuation x8 Interpolation Filter Passband Ripple, Single Rate

Figure 50. High-Attentuation x8 Interpolation Filter Passband Ripple, Single Rate

Figure 49. High-Attentuation x8 Interpolation Filter Impulse Response, Single Rate

Figure 49. High-Attentuation x8 Interpolation Filter Impulse Response, Single Rate

Table 19. High-Attentuation x4 Interpolation Filter, Dual Rate

| PARAMETER | CONDITION | VALUE (TYP) | VALUE (MAX) | UNIT |

|---|---|---|---|---|

| Filter Gain Pass Band | 0 ……. 0.45 × fS | ±0.0005 | dB | |

| Filter Gain Stop Band | 0.55 × fS ….. 3.455 × fS | –100 | dB | |

| Filter Group Delay | 33.7 × tS | S |

SPACE

Figure 51. High-Attentuation x4 Interpolation Filter Frequency Response, Dual Rate

Figure 51. High-Attentuation x4 Interpolation Filter Frequency Response, Dual Rate

Figure 53. High-Attentuation x4 Interpolation Filter Passband Ripple, Dual Rate

Figure 53. High-Attentuation x4 Interpolation Filter Passband Ripple, Dual Rate

Figure 52. High-Attentuation x4 Interpolation Filter Impulse Response, Dual Rate

Figure 52. High-Attentuation x4 Interpolation Filter Impulse Response, Dual Rate

Table 20. High-Attentuation x2 Interpolation Filter, Quad Rate

| PARAMETER | CONDITION | VALUE (TYP) | VALUE (MAX) | UNIT |

|---|---|---|---|---|

| Filter Gain Pass Band | 0 ……. 0.45 × fS | ±0.0005 | dB | |

| Filter Gain Stop Band | 0.55 × fS ….. 1.455 × fS | –100 | dB | |

| Filter Group Delay | 33.7 × tS | S |

SPACE

Figure 54. High-Attentuation x2 Interpolation Filter Frequency Response, Quad Rate

Figure 54. High-Attentuation x2 Interpolation Filter Frequency Response, Quad Rate

Figure 56. High-Attentuation x2 Interpolation Filter Passband Ripple, Quad Rate

Figure 56. High-Attentuation x2 Interpolation Filter Passband Ripple, Quad Rate

Figure 55. High-Attentuation x2 Interpolation Filter Impulse Response, Quad Rate

Figure 55. High-Attentuation x2 Interpolation Filter Impulse Response, Quad Rate

8.3.4.3 Fixed Audio Processing Flow (Program 5)

The PCM514x implements signal processing capabilities and interpolation filtering via processing blocks. These fixed processing blocks give users the choice of how much and what type of signal processing they may use and which interpolation filter is applied.

The signal processing blocks available are:

- Biquad filters

- Multiband DRC

- Mono mixer

- Stereo mixer

- Master volume

The addresses of the coefficients are fixed when selecting the fixed processing flow, however, if these components are used in the RAM source mode (Program 31) the registers for coefficients will change. Users can find more details in Purepath Studio.

NOTE

This process flow requires 1024 instruction cycles. Therefore, it will only function at sampling frequencies up to 48 kHz.

8.3.4.3.1 Processing Blocks – Detailed Descriptions

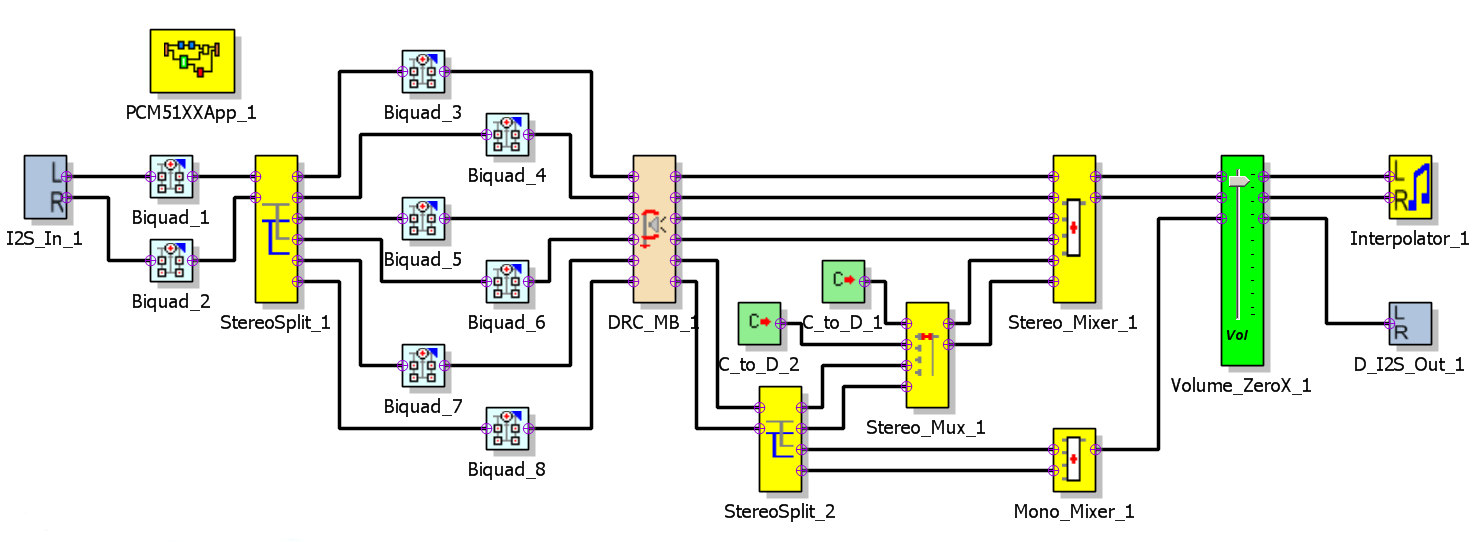

Figure 57 shows the fixed processing flow.

Figure 57. Preset Process Flow

Figure 57. Preset Process Flow

Figure 58 shows a screen capture of PurePath Studio.

Figure 58. PurePath Studio Screen Capture

Figure 58. PurePath Studio Screen Capture

8.3.4.3.2 Biquad Section

The transfer function of each of the biquad filters is given by Equation 1.

Figure 59. Biquad Block

Figure 59. Biquad Block

Table 21. Biquad Filter Coefficients

| FILTER | CHANNEL | COEFFICIENT | REGISTER |

|---|---|---|---|

| BIQUAD (1) - 1 BIQUAD (2) - 1 | Lch, Rch |

N0 | C10 (Pg 44, Reg 48 ,49, 50, 51) |

| N1 | C11 (Pg 44, Reg 52, 53, 54, 55) | ||

| N2 | C12 (Pg 44, Reg 56, 57, 58, 59) | ||

| D1 | C13 (Pg 44, Reg 60, 61, 62, 63) | ||

| D2 | C14 (Pg 44, Reg 64, 65, 66, 67) | ||

| BIQUAD (1) - 2 BIQUAD (2) - 2 | Lch, Rch |

N0 | C15 (Pg 44, Reg 68, 69, 70, 71) |

| N1 | C16 (Pg 44, Reg 72, 73, 74, 75) | ||

| N2 | C17 (Pg 44, Reg 76, 77, 78, 79) | ||

| D1 | C18 (Pg 44, Reg 80, 81, 82, 83) | ||

| D2 | C19 (Pg 44, Reg 84, 85, 86, 87) | ||

| BIQUAD (1) - 3 BIQUAD (2) - 3 | Lch, Rch |

N0 | C20 (Pg 44, Reg 88, 89, 90, 91) |

| N1 | C21 (Pg 44, Reg 92, 93, 94, 95) | ||

| N2 | C22 (Pg 44, Reg 96, 97, 98, 99) | ||

| D1 | C23 (Pg 44, Reg 100, 101, 102, 103) | ||

| D2 | C24 (Pg 44, Reg 104, 105, 106, 107) | ||

| BIQUAD (1) - 4 BIQUAD (2) - 4 | Lch, Rch |

N0 | C25 (Pg 44, Reg 108, 109, 110, 111) |

| N1 | C26 (Pg 44, Reg 112, 113, 114, 115) | ||

| N2 | C27 (Pg 44, Reg 116, 117, 118, 119) | ||

| D1 | C28 (Pg 44, Reg 120, 121, 122, 123) | ||

| D2 | C29 (Pg 44, Reg 124, 125, 126, 127) | ||

| BIQUAD (1) - 5 BIQUAD (2) - 5 | Lch, Rch |

N0 | C30 (Pg 45, Reg 8, 9, 10, 11) |

| N1 | C31 (Pg 45, Reg 12, 13, 14, 15) | ||

| N2 | C32 (Pg 45, Reg 16, 17, 18, 19) | ||

| D1 | C33 (Pg 45, Reg 20, 21, 22, 23) | ||

| D2 | C34 (Pg 45, Reg 24, 25, 26, 27) | ||

| BIQUAD (1) - 6 BIQUAD (2) - 6 | Lch, Rch |

N0 | C35 (Pg 45, Reg 28, 29, 30, 31) |

| N1 | C36 (Pg 45, Reg 32, 33, 34, 35) | ||

| N2 | C37 (Pg 45, Reg 36, 37, 38, 39) | ||

| D1 | C38 (Pg 45, Reg 40, 41, 42, 43) | ||

| D2 | C39 (Pg 45, Reg 44, 45, 46, 47) | ||

| BIQUAD (3) - 1 BIQUAD (4) - 1 | Lch, Rch |

N0 | C40 (Pg 45, Reg 48, 49, 50, 51) |

| N1 | C41 (Pg 45, Reg 52, 53, 54, 55) | ||

| N2 | C42 (Pg 45, Reg 56, 57, 58, 59) | ||

| D1 | C43 (Pg 45, Reg 60, 61, 62, 63) | ||

| D2 | C44 (Pg 45, Reg 64, 65, 66, 67) | ||

| BIQUAD (3) - 2 BIQUAD (4) - 2 | Lch, Rch |

N0 | C45 (Pg 45, Reg 68, 69, 70, 71) |

| N1 | C46 (Pg 45, Reg 72, 73, 74, 75) | ||

| N2 | C47 (Pg 45, Reg 76, 77, 78, 79) | ||

| D1 | C48 (Pg 45, Reg 80, 81, 82, 83) | ||

| D2 | C49 (Pg 45, Reg 84, 85, 86, 87) | ||

| BIQUAD (5) - 1 BIQUAD (6) - 1 | Lch, Rch |

N0 | C50 (Pg 45, Reg 88, 89, 90, 91) |

| N1 | C51 (Pg 45, Reg 92, 93, 94, 95) | ||

| N2 | C52 (Pg 45, Reg 96, 97, 98, 99) | ||

| D1 | C53 (Pg 45, Reg 100, 101, 102, 103) | ||

| D2 | C54 (Pg 45, Reg 104, 105, 106, 107) | ||

| BIQUAD (5) - 2 BIQUAD (6) - 2 | Lch, Rch |

N0 | C55 (Pg 45, Reg 108, 109, 110, 111) |

| N1 | C56 (Pg 45, Reg 112, 113, 114, 115) | ||

| N2 | C57 (Pg 45, Reg 116, 117, 118, 119) | ||

| D1 | C58 (Pg 45, Reg 120, 121, 122, 123) | ||

| D2 | C59 (Pg 45, Reg 124, 125, 126, 127) | ||

| BIQUAD (7) - 1 BIQUAD (8) - 1 | Lch, Rch |

N0 | C60 (Pg 46, Reg 8, 9, 10, 11) |

| N1 | C61 (Pg 46, Reg 12, 13, 14, 15) | ||

| N2 | C62 (Pg 46, Reg 16, 17, 18, 19) | ||

| D1 | C63 (Pg 46, Reg 20, 21, 22, 23) | ||

| D2 | C64 (Pg 46, Reg 24, 25, 26, 27) | ||

| BIQUAD (7) - 2 BIQUAD (8) - 2 | Lch, Rch |

N0 | C65 (Pg 46, Reg 28, 29, 30, 31) |

| N1 | C66 (Pg 46, Reg 32, 33, 34, 35) | ||

| N2 | C67 (Pg 46, Reg 36, 37, 38, 39) | ||

| D1 | C68 (Pg 46, Reg 40, 41, 42, 43) | ||

| D2 | C69 (Pg 46, Reg 44, 45, 46, 47) |

8.3.4.3.3 Dynamic Range Compression

Dynamic range compression (DRC) improves the overall listening experience. Typical music signals are characterized by crest factors (the ratio of peak signal power to average signal power) of 12 dB or more. To avoid audible distortion due to clipping of peak signals, the gain of the DAC channel must be adjusted so as not to cause hard clipping. As a result, the low applied gain during nominal periods causes the perception that the signal is not loud enough. To overcome this problem, the DRC in the PCM514x continuously monitors the output of the DAC Digital Volume control to detect its power level with respect to 0-dB full-scale. When the power level is low, the DRC increases the input signal gain to make it sound louder, and reduces the gain during peaks to avoid hard clipping. The DRC enables louder audio during nominal periods with a clearer, more pleasant listening experience.

The 3-band DRC function applies DRC to 3 different mono/stereo signals with 3 different time constants. The same DRC curve is applied on all the signals, enabling a multi-band DRC solution. The underlying DRC algorithm is the same as that available with the DRC component in PurePath Studio. In this instance, the DRC gain acts on each signal in time-multiplexed order, for example, 1-2-3, 1-2-3, 1-2-3.

Table 22. DRC Coefficients

| COEFFICIENT | REGISTER |

|---|---|

| DRC_MB_1_DRC_1_DRCAE | C70 (Pg 46, Reg 48, 49, 50, 51) |

| DRC_MB_1_DRC_1_DRC1AE | C71 (Pg 46, Reg 52, 53, 54, 55) |

| DRC_MB_1_DRC_1_DRCAA | C72 (Pg 46, Reg 56, 57, 58, 59) |

| DRC_MB_1_DRC_1_DRC1AA | C73 (Pg 46, Reg 60, 61, 62, 63) |

| DRC_MB_1_DRC_1_DRCAD | C74 (Pg 46, Reg 64, 65, 66, 67) |

| DRC_MB_1_DRC_1_DRC1AD | C75 (Pg 46, Reg 68, 69, 70, 71) |

| DRC_MB_1_DRC_2_DRCAE | C76 (Pg 46, Reg 72, 73, 74, 75) |

| DRC_MB_1_DRC_2_DRC1AE | C77 (Pg 46, Reg 76, 77, 78, 79) |

| DRC_MB_1_DRC_2_DRCAA | C78 (Pg 46, Reg 80, 81, 82, 83) |

| DRC_MB_1_DRC_2_DRC1AA | C79 (Pg 46, Reg 84, 85, 86, 87) |

| DRC_MB_1_DRC_2_DRCAD | C80 (Pg 46, Reg 88, 89, 90, 91) |

| DRC_MB_1_DRC_2_DRC1AD | C81 (Pg 46, Reg 92, 93, 94, 95) |

| DRC_MB_1_DRC_3_DRCAE | C82 (Pg 46, Reg 96, 97, 98, 99) |

| DRC_MB_1_DRC_3_DRC1AE | C83 (Pg 46, Reg 100, 101, 102, 103) |

| DRC_MB_1_DRC_3_DRCAA | C84 (Pg 46, Reg 104, 105, 106, 107) |

| DRC_MB_1_DRC_3_DRC1AA | C85 (Pg 46, Reg 108, 109, 119, 111) |

| DRC_MB_1_DRC_3_DRCAD | C86 (Pg 46, Reg 112, 113, 114, 115) |

| DRC_MB_1_DRC_3_DRC1AD | C87 (Pg 46, Reg 116, 117, 118, 119) |

| DRC_MB_1_DRC_DRCK0 | C88 (Pg 46, Reg 120, 121, 122, 123) |

| DRC_MB_1_DRC_DRCK1 | C89 (Pg 46, Reg 124, 125, 126, 127) |

| DRC_MB_1_DRC_DRCK2 | C90 (Pg 47, Reg 8, 9, 10, 11) |

| DRC_MB_1_DRC_DRCMT1 | C91 (Pg 47, Reg 12, 13, 14, 15) |

| DRC_MB_1_DRC_DRCMT2 | C92 (Pg 47, Reg 16, 17, 18, 19) |

| DRC_MB_1_DRC_DRCOFF1 | C93 (Pg 47, Reg 20, 21, 22, 23) |

| DRC_MB_1_DRC_DRCOFF2 | C94 (Pg 47, Reg 24, 25, 26, 27) |

| DRC_MB_1_MinusOne_Q22 | C95 (Pg 47, Reg 28, 29, 30, 31) |

| DRC_MB_1_MinusTwo_Q22 | C96 (Pg 47, Reg 32, 33, 34, 35) |

| DRC_MB_1_One_M2 | C97 (Pg 47, Reg 36, 37, 38, 39) |

| DRC_MB_1_Zero | C98 (Pg 47, Reg 40, 41, 42, 43) |

| DRC_MB_1_En_dB | C99 (Pg 47, Reg 44, 45, 46, 47) |

| DRC_MB_1_Minus__Zero_dB | C100 (Pg 47, Reg 48, 49, 50, 51) |

| DRC_MB_1_60_dB | C101 (Pg 47, Reg 52, 53, 54, 55) |

| DRC_MB_1_Minus_60_dB | C102 (Pg 47, Reg 56, 57, 58, 59) |

| DRC_MB_1_12_dB | C103 (Pg 47, Reg 60, 61, 62, 63) |

| DRC_MB_1_Offset | C104 (Pg 47, Reg 64, 65, 66, 67) |

| DRC_MB_1_K | C105 (Pg 47, Reg 68, 69, 70, 71) |

| DRC_MB_1_x / DRC_MB_1_DRC | C106 (Pg 47, Reg 72, 73, 74, 75) |

| DRC_MB_1_48_dB | C107 (Pg 47, Reg 76, 77, 78, 79) |

| DRC_MB_1_Minus_48_dB | C108 (Pg 47, Reg 80, 81, 82, 83) |

| DRC_MB_1_c1_3 | C109 (Pg 47, Reg 84, 85, 86, 87) |

| DRC_MB_1_c1_2 | C110 (Pg 47, Reg 88, 89, 90, 91) |

| DRC_MB_1_c1_1 | C111 (Pg 47, Reg 92, 93, 94, 95) |

| DRC_MB_1_c1_0 | C112 (Pg 47, Reg 96, 97, 98, 99) |

| DRC_MB_1_O1_1 | C113 (Pg 47, Reg 100, 101, 102, 103) |

| DRC_MB_1_S1_1 | C114 (Pg 47, Reg 104, 105, 106, 107) |

| DRC_MB_1_O1_2 | C115 (Pg 47, Reg 108, 109, 119, 111) |

| DRC_MB_1_S1_2 | C116 (Pg 47, Reg 112, 113, 114, 115) |

| DRC_MB_1_O1_3 | C117 (Pg 47, Reg 116, 117, 118, 119) |

| DRC_MB_1_S1_3 | C118 (Pg 47, Reg 120, 121, 122, 123) |

| DRC_MB_1_One_1_Q17 | C119 (Pg 47, Reg 124, 125, 126, 127) |

| DRC_MB_1_Scale1 | C120 (Pg 48, Reg 8, 9, 10, 11) |

| DRC_MB_1_x1Coeff | C121 (Pg 48, Reg 12, 13, 14, 15) |

| DRC_MB_1_c2_3 | C122 (Pg 48, Reg 16, 17, 18, 19) |

| DRC_MB_1_c2_2 | C123 (Pg 48, Reg 20, 21, 22, 23) |

| DRC_MB_1_c2_1 | C124 (Pg 48, Reg 24, 25, 26, 27) |

| DRC_MB_1_c2_0 | C125 (Pg 48, Reg 28, 29, 30, 31) |

| DRC_MB_1_O2_1 | C126 (Pg 48, Reg 32, 33, 34, 35) |

| DRC_MB_1_S2_1 | C127 (Pg 48, Reg 36, 37, 38, 39) |

| DRC_MB_1_O2_2 | C128 (Pg 48, Reg 40, 41, 42, 43) |

| DRC_MB_1_S2_2 | C129 (Pg 48, Reg 44, 45, 46, 47) |

| DRC_MB_1_O2_3 | C130 (Pg 48, Reg 48, 49, 50, 51) |

| DRC_MB_1_S2_3 | C131 (Pg 48, Reg 52, 53, 54, 55) |

| DRC_MB_1_One_2_Q17 | C132 (Pg 48, Reg 56, 57, 58, 59) |

| DRC_MB_1_Scale2 | C133 (Pg 48, Reg 60, 61, 62, 63) |

| DRC_MB_1_x2Coeff | C134 (Pg 48, Reg 64, 65, 66, 67) |

| DRC_MB_1_R1_1 | C135 (Pg 48, Reg 68, 69, 70, 71) |

| DRC_MB_1_R1_2 | C136 (Pg 48, Reg 72, 73, 74, 75) |

| DRC_MB_1_R2_1 | C137 (Pg 48, Reg 76, 77, 78, 79) |

| DRC_MB_1_R2_2 | C138 (Pg 48, Reg 80, 81, 82, 83) |

| DRC_MB_1_Band1_GainC | C139 (Pg 48, Reg 84, 85, 86, 87) |

| DRC_MB_1_Band2_GainC | C140 (Pg 48, Reg 88, 89, 90, 91) |

| DRC_MB_1_Band3_GainC | C141 (Pg 48, Reg 92, 93, 94, 95) |

| DRC_MB_1_MinusOne_M1 | C142 (Pg 48, Reg 96, 97, 98, 99) |

| DRC_MB_1_One_M1 | C143 (Pg 48, Reg 100, 101, 102, 103) |

| DRC_MB_1_Band1_GainE | C144 (Pg 48, Reg 104, 105, 106, 107) |

| DRC_MB_1_Band2_GainE | C145 (Pg 48, Reg 108, 109, 110, 111) |

| DRC_MB_1_Band3_GainE | C146 (Pg 48, Reg 112, 113, 114, 115) |

| DRC_MB_1_minus_One_M2 | C147 (Pg 48, Reg 116, 117, 118, 119) |

8.3.4.3.4 Stereo Mixer

Three stereo inputs are mixed into one stereo output with input signal gain given by Equation 2.

where

- i=1:2,3

Figure 60 and Table 23 show the stereo mixer operation.

Figure 60. Stereo Mixer Block

Figure 60. Stereo Mixer Block

Table 23. Stereo Mixer Coefficients

| COEFFICIENT | REGISTER |

|---|---|

| Stereo_Mixer_1_MixGain1 | C148 (Pg 48, Reg 120, 121, 122, 123) |

| Stereo_Mixer_1_MixGain2 | C149 (Pg 48, Reg 124, 125, 126, 127) |

| Stereo_Mixer_1_MixGain3 | C150 (Pg 49, Reg 8, 9, 10, 11) |

8.3.4.3.5 Stereo Multiplexer

The Stereo Multiplexer selects one or two from 4 stereo input channels.

Figure 61. Stereo Multiplexer Block

Figure 61. Stereo Multiplexer Block

Table 24. Stereo Multiplexer Select Coefficient

| COEFFICIENT | REGISTER |

|---|---|

| Stereo_Mux_1_MuxSelect | C152 (Pg 49, Reg 16, 17, 18, 19) |

Table 25. Stereo Multiplexer Input Coefficient

| COEFFICIENT | REGISTER |

|---|---|

| C_to_D_1_Coefval C_to_D_2_Coefval |

C153 (Pg 49, Reg 20, 21, 22, 23) |

8.3.4.3.6 Mono Mixer

The Mono Mixer computes a weighted sum of 2 input channels and produces an output.

Figure 62. Mono Mixer Block

Figure 62. Mono Mixer Block

Table 26. Mono Mixer Coefficients

| COEFFICIENT | REGISTER |

|---|---|

| Mono_Mixer_1_MixGain1 | C154 (Pg 49, Reg 24, 25, 26, 27) |

| Mono_Mixer_1_MixGain2 | C155 (Pg 49, Reg 28, 29, 30, 31) |

8.3.4.3.7 Master Volume Control

The Master Volume controls the volume using a linear ramp and zero crossing detection for transitions.

Table 27. Mono Mixer Coefficients

| COEFFICIENT | REGISTER |

|---|---|

| Volume_ZeroX_1_volcmd | C158 (Pg 49, Reg 40, 41, 42, 43) |

| Volume_ZeroX_1_volout | C159 (Pg 49, Reg 44, 45, 46, 47) |

| Volume_ZeroX_1_volout_loudness | C160 (Pg 49, Reg 48, 49, 50, 51) |

| Volume_ZeroX_1_MinusOne_M2 | C161 (Pg 49, Reg 52, 53, 54, 55) |

| Volume_ZeroX_1_workingval_1_pre_CRAM | C162 (Pg 49, Reg 56, 57, 58, 59) |

| Volume_ZeroX_1_volout_pre1 | C163 (Pg 49, Reg 60, 61, 62, 63) |

| Volume_ZeroX_1_workingval_2_pre_CRAM | C164 (Pg 49, Reg 64, 65, 66, 67) |

| Volume_ZeroX_1_volout_pre2 | C165 (Pg 49, Reg 68, 69, 70, 71) |

| Volume_ZeroX_1_workingval_3_pre_CRAM | C166 (Pg 49, Reg 72, 73, 74, 75) |

| Volume_ZeroX_1_volout_pre3 | C167 (Pg 49, Reg 76, 77, 78, 79) |

| Volume_ZeroX_1_One_M2 | C168 (Pg 49, Reg 80, 81, 82, 83) |

| Volume_ZeroX_1_Zero | C169 (Pg 49, Reg 84, 85, 86, 87) |

| MinusOne_Int | C170 (Pg 49, Reg 88, 89, 90, 91) |

| MinusOne_M1 | C171 (Pg 49, Reg 92, 93, 94, 95) |

| One_M2 | C172 (Pg 49, Reg 96, 97, 98, 99) |

| One_M1 | C173 (Pg 49, Reg 100, 101, 102, 103) |

| Zero | C174 (Pg 49, Reg 104, 105, 106, 107) |

8.3.4.3.8 Miscellaneous Coefficients

Table 28. Miscellaneous Coefficients

| COEFFICIENT | REGISTER |

|---|---|

| DRC_MB_1_DataBlock | C175 (Pg 49, Reg 108, 109, 110, 111) |

| DRC_MB_1_CoeffBlock | C176 (Pg 49, Reg 112, 113, 114, 115) |

| Volume_ZeroX_1_DataBlock | C177 (Pg 49, Reg 116, 117, 118, 119) |

| Volume_ZeroX_1_CoeffBlock | C178 (Pg 49, Reg 120, 121, 122, 123) |

| plus_one | C179 (Pg 49, Reg 124, 125, 126, 127) |

| ADD_OF_filter_in_L | C180 (Pg 50, Reg 8, 9, 10, 11) |

| ADD_OF_filter_in_R | C181 (Pg 50, Reg 12, 13, 14, 15) |

8.3.5 DAC Outputs

8.3.5.1 Analog Outputs

The PCM514x devices include a two-channel DAC, with single-ended outputs. The full-scale output voltage is 2.1Vrms with ground center output. A dc-coupled load is supported in addition to an ac-coupled load, if the load resistance conforms to the specification. The PCM514x DAC outputs on the OUTL and OUTR terminals have market-leading low out-of-band noise, which offer up to 20dB lower out-of-band noise compared with existing DAC technology.

Most applications require an external low-pass RC filter (470Ω + 2.2nF) to provide sufficient out-of-band noise rejection. This RC filter provides the added advantage of improved protection against ESD damage.

8.3.5.2 Recommended Output Filter for the PCM514x

The diagram in Figure 63 shows the recommended output filter for the PCM514x. The new PCM514x next-generation current segment architecture offers excellent out-of-band noise, making a traditional 20-kHz low pass filter a thing of the past.

The RC settings below offer a –3-dB filter point at 153 kHz (approximately), giving the DAC the ability to reproduce virtually all frequencies through to it’s maximum sampling rate of 384 kHz. A NP0/C0G type capacitor is strongly recommended for the shunt capacitor for lowest distortion.

Figure 63. Recommended Output Lowpass Filter for 10-kΩ Operation

Figure 63. Recommended Output Lowpass Filter for 10-kΩ Operation

8.3.5.3 Choosing Between VREF and VCOM Modes

VREF mode is the default configuration. This mode allows full 2.1-Vrms signal output. As shown in Recommended Operating Conditions, the minimum AVDD to avoid clipping is 3.2 V.

VCOM mode allows setting a custom common-mode voltage when required by the application. This somewhat limits the output signal swing before clipping.

8.3.5.3.1 Voltage Reference and Output Levels

The PCM514x devices have an internal, fixed band-gap reference voltage, with default operation in VREF mode. No external decoupling capacitor is required for this mode.

The PCM514x devices can be operated with a common-mode voltage output (VCOM mode) at the VCOM pin by setting Page 1, Register 1, D(0) to 1. In this mode, an external decoupling capacitor is required.

When using this DAC in VREF mode, the output-signal voltage is independent of the power-supply voltage: The D/A conversion gain in VREF mode yields a 2.1-Vrms output voltage with a digital full-scale input. However, in VREF mode, an output waveform may clip due to the limitations that may be present in the analog power supply voltage. On the other hand, the full-scale output voltage in VCOM mode is proportional to the analog power supply AVDD (for example, (2.1 × AVDD / 3.3) Vrms).

8.3.5.3.2 Mode Switching Sequence, from VREF Mode to VCOM Mode

Following register setting sequence is recommended for changing VREF mode to VCOM mode.

| 1. | Page 0 / Register 2 | RQST = 1: Standby mode |

| 2. | Page 1 / Register 8 | RCMF = 1: Fast ramp up → on |

| 3. | Page 1 / Register 9 | VCPD = 0: VCOM is power on |

| 4. | Wait 3 ms with external capacitor = 1 µF | |

| 5. | Page 1 / Register 8 | RCMF = 0: Fast ramp up → off |

| 6. | Page 1 / Register 1 | OSEL = 1: VCOM mode |

| 7. | Page 0 / Register 2 | RQST = 0: Normal mode |

8.3.5.4 Digital Volume Control

A basic digital volume control with range from 24 dB to –103 dB and mute is available on each channels by Page 0, Resister 61, D(7:0) for L-ch and Register 62, D(7:0) for R-ch. These volume controls all have 0.5-dB step programmability over most gain and attenuation ranges. Table 29 lists the detailed gain versus programmed setting for this basic volume control. Volume can be changed for both L-ch and R-ch at the same time or independently by Page 0, Register 60, D(1:0). When D(1:0) set 00 (default), independent control is selected. When D(1:0) set 01, R-ch accords with L-ch volume. When D(1:0) set 10, L-ch accords with R-ch volume. To set D(1:0) to 11 is prohibited.

NOTE

This volume control is done externally to the miniDSP and only influences the analog DAC output. Any changes to the SDOUT data should be done in the miniDSP process flow.

Table 29. Digital Volume Control Settings

| GAIN SETTING | BINARY DATA | GAIN (dB) | COMMENTS |

|---|---|---|---|

| 0 | 0000-0000 | 24.0 | Positive maximum |

| 1 | 0000-0001 | 23.5 | |

| : | : | — | |

| 46 | 0010-1110 | 1.0 | |

| 47 | 0010-1111 | 0.5 | |

| 48 | 0011-0000 | 0.0 | No attenuation (default) |

| 49 | 0011-0001 | –0.5 | |

| 50 | 0011-0010 | –1.0 | |

| 51 | 0011-0011 | –1.5 | |

| : | : | — | |

| 253 | 1111-1101 | –102.5 | |

| 254 | 1111-1110 | –103 | Negative maximum |

| 255 | 1111-1111 | –∞ | Negative infinite (Mute) |

Ramp-up frequency and ramp-down frequency can be controlled by Page 0, Register 63, D(7:6) and D(3:2) as shown in Table 30. Also Ramp-up step and ramp-down step can be controlled by Page 0, Register 63 D(5:4) and D(1:0) as shown in Table 31.

Table 30. Ramp-Up or Down Frequency

| RAMP-UP SPEED | EVERY N fS | COMMENTS | RAMP-DOWN FREQUENCY | EVERY N fS | COMMENTS | |

|---|---|---|---|---|---|---|

| 00 | 1 | Default | 00 | 1 | Default | |

| 01 | 2 | 01 | 2 | |||

| 10 | 4 | 10 | 4 | |||

| 11 | Direct change | 11 | Direct change |

Table 31. Ramp-Up or Down Step

| RAMP-UP STEP | STEP dB | COMMENTS | RAMP-DOWN STEP | STEP dB | COMMENTS | |

|---|---|---|---|---|---|---|

| 00 | 4.0 | 00 | -4.0 | |||

| 01 | 2.0 | 01 | -2.0 | |||

| 10 | 1.0 | Default | 10 | -1.0 | Default | |

| 11 | 0.5 | 11 | -0.5 |

8.3.5.4.1 Emergency Ramp-Down

Digital volume emergency ramp-down by is provided for situations such as I2S clock error and power supply failure. Ramp-down speed is controlled by Page 0, Register 64, D(7:6). Ramp-down step can be controlled by Page 0 Register 64, D(5:4). Default is ramp-down by every fS cycle with –4-dB step.

8.3.5.5 Analog Gain Control

Analog gain control can be selected between 2-Vrms FS (0dB) or 1-Vrms FS (–6 dB). Gain is controlled through hardware by the AGNS pin, and through software (SPI/I2C), Page 1, Register 2, D4(L-ch) / D0(R-ch).

8.3.6 Reset and System Clock Functions

8.3.6.1 Clocking Overview

The PCM514x devices have flexible systems for clocking. Internally, the device requires a number of clocks, mostly at related clock rates to function correctly. All of these clocks can be derived from the serial audio interface in one form or another.

Figure 64. Audio Flow with Respective Clocks

Figure 64. Audio Flow with Respective Clocks

As shown in Figure 64 the data flows at the sample rate (fS). Once the data is brought into the serial audio interface, it gets processed, interpolated and modulated all the way to 128 × fS before arriving at the current segments for the final digital to analog conversion.

The clock tree is shown in Figure 65.

Figure 65. PCM514x Clock Distribution Tree

Figure 65. PCM514x Clock Distribution Tree

The serial audio interface typically has 4 connections: SCK (system master clock), BCK (bit clock), LRCK (left right word clock), and DIN (data). The device has an internal PLL that is used to take either SCK or BCK and create the higher rate clocks required by the interpolating processor and the DAC clock. This allows the device to operate with or without an external SCK.

In situations where the highest audio performance is required, it is suggested that the SCK is brought to the device, along with BCK and LRCK. The device should be configured so that the PLL is only providing a clock source to the miniDSP. By ensuring that the DACCK (DAC Clock) is being driven by the external SCK source, jitter evident in the PLL (in all PLLs) is kept out of the DAC, charge pump, and oversampling system.

Everything else should be a division of the incoming SCK. This is done by setting DAC CLK Source Mux (SDAC in Figure 65) to use SCK as a source, rather than the output of the SCK/PLL Mux. Code examples for this are available in SLASE12.

When the Auto Clock Configuration bit is set (Page 0/ Register 0x25), no additional clocks configuration is required. However, when setting custom PLL values and so forth, the target output rates should match those shown in the recommended PLL values of Table 132.

8.3.6.2 Clock Slave Mode With Master and System Clock (SCK) Input (4 Wire I2S)

The PCM514x requires a system clock to operate the digital interpolation filters and advanced segment DAC modulators. The system clock is applied at the SCK input and supports up to 50 MHz. The PCM514x system-clock detection circuit automatically senses the system-clock frequency. Common audio sampling frequencies in the bands of 8 kHz, 16 kHz, (32 kHz - 44.1 kHz - 48 kHz), (88.2kHz - 96kHz), (176.4 kHz - 192 kHz), and 384 kHz with ±4% tolerance are supported. Values in the parentheses are grouped when detected, (for example, 88.2 kHZ and 96 kHz are detected as double rate, and 32 kHz, 44.1 kHz and 48 kHz are detected as single rate.)

In the presence of a valid bit SCK, BCK and LRCK in software mode, the device will auto-configure the clock tree and PLL to drive the miniDSP as required.

The sampling frequency detector sets the clock for the digital filter, Delta Sigma Modulator (DSM) and the Negative Charge Pump (NCP) automatically. Table 32 shows examples of system clock frequencies for common audio sampling rates.

SCK rates that are not common to standard audio clocks, between 1 MHz and 50 MHz, are only supported in software mode by configuring various PLL and clock-divider registers. This programmability allows the device to become a clock master and drive the host serial port with LRCK and BCK, from a non-audio related clock (for example, using 12 MHz to generate 44.1 kHz [LRCK] and 2.8224 MHz [BCK]).

Table 32. System Master Clock Inputs for Audio Related Clocks

| SAMPLING FREQUENCY | SYSTEM CLOCK FREQUENCY (fSCK) (MHz) | |||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 64 fS | 128 fS | 192 fS | 256 fS | 384 fS | 512 fS | 768 fS | 1024 fS | 1152 fS | 1536 fS | 2048 fS | 3072 fS | |

| 8 kHz | –(1) | 1.024(2) | 1.536(2) | 2.048 | 3.072 | 4.096 | 6.144 | 8.192 | 9.216 | 12.288 | 16.384 | 24.576 |

| 16 kHz | –(1) | 2.048(2) | 3.072(2) | 4.096 | 6.144 | 8.192 | 12.288 | 16.384 | 18.432 | 24.576 | 36.864 | 49.152 |

| 32 kHz | –(1) | 4.096(2) | 6.144(2) | 8.192 | 12.288 | 16.384 | 24.576 | 32.768 | 36.864 | 49.152 | –(1) | –(1) |

| 44.1 kHz | –(1) | 5.6488(2) | 8.4672(2) | 11.2896 | 16.9344 | 22.5792 | 33.8688 | 45.1584 | –(1) | –(1) | –(1) | –(1) |

| 48 kHz | –(1) | 6.144(2) | 9.216(2) | 12.288 | 18.432 | 24.576 | 36.864 | 49.152 | –(1) | –(1) | –(1) | –(1) |

| 88.2 kHz | –(1) | 11.2896(2) | 16.9344 | 22.5792 | 33.8688 | 45.1584 | –(1) | –(1) | –(1) | –(1) | –(1) | –(1) |

| 96 kHz | –(1) | 12.288(2) | 18.432 | 24.576 | 36.864 | 49.152 | –(1) | –(1) | –(1) | –(1) | –(1) | –(1) |

| 176.4 kHz | –(1) | 22.579 | 33.8688 | 45.1584 | –(1) | –(1) | –(1) | –(1) | –(1) | –(1) | –(1) | –(1) |

| 192 kHz | –(1) | 24.576 | 36.864 | 49.152 | –(1) | –(1) | –(1) | –(1) | –(1) | –(1) | –(1) | –(1) |

| 384 kHz | 24.576 | 49.152 | –(1) | –(1) | –(1) | –(1) | –(1) | –(1) | –(1) | –(1) | –(1) | –(1) |

See Timing Requirements: PCM Audio Data for clock timing requirements.

8.3.6.3 Clock Slave Mode With BCK PLL to Generate Internal Clocks (3-Wire PCM)

The system clock PLL mode allows designers to use a simple 3-wire I2S audio source. The 3-wire source reduces the need for a high frequency SCK, making PCB layout easier, and reduces high frequency electromagnetic interference.

In hardwired mode, the internal PLL is disabled as soon as an external SCK is supplied.

In hardwired mode, the device starts up expecting an external SCK input, but if BCK and LRCK start correctly while SCK remains at ground level for 16 successive LRCK periods, then the internal PLL starts, automatically generating an internal SCK from the BCK reference. Specific BCK rates are required to generate an appropriate master clock. Table 33 describes the minimum and maximum BCK per LRCK for the integrated PLL to automatically generate an internal SCK.

In software mode, the user must set all the PLL registers and clock divider registers for referencing BCK. See Clock Generation Using the PLL for more information. Recommended values can be found in Table 132.

Table 33. BCK Rates (MHz) by LRCK Sample Rate for PCM514x PLL Operation

| SAMPLE F (kHz) | BCK (fS) | |

|---|---|---|

| 32 | 64 | |

| 8 | – | – |

| 16 | – | 1.024 |

| 32 | 1.024 | 2.048 |

| 44.1 | 1.4112 | 2.8224 |

| 48 | 1.536 | 3.072 |

| 96 | 3.072 | 6.144 |

| 192 | 6.144 | 12.288 |

| 384 | 12.288 | 24.576 |

8.3.6.4 Clock Generation Using the PLL

The PCM514x supports a wide range of options to generate the required clocks for the DAC section as well as interface and other control blocks as shown in Figure 65.

The clocks for the PLL require a source reference clock. This clock is sourced as the incoming BCK or SCK. In software mode, a GPIO can also be used.

The source reference clock for the PLL reference clock is selected by programming the SRCREF value on Page 0, Register 13, D(6:4). The PCM514x provides several programmable clock dividers to achieve a variety of sampling rates for the DAC and clocks for the NCP, OSR, and the miniDSP. OSRCK for OSR must be set at 16 fS frequency by DOSR on Page0, Register 30, D(6:0). See Figure 65.

If PLL functionality is not required, set the PLLEN value on Page 0, Register 4, D(0) to 0. In this situation, an external SCK is required.

Table 34. PLL Configuration Registers

| CLOCK MULTIPLEXER | FUNCTION | BITS |

|---|---|---|

| SRCREF | PLL reference | Page 0, Register 13, D(6:4) |

| DIVIDER | FUNCTION | BITS |

| DDSP | miniDSP clock divider | Page 0, Register 27, D(6:0) |

| DACCK | DAC clock divider | Page 0, Register 28, D(6:0) |

| CPCK | NCP clock divider | Page 0, Register 29, D(6:0) |

| OSRCK | OSR clock divider | Page 0, Register 30, D(6:0) |

| DBCK | External BCK Div | Page 0, Register 32, D(6:0) |

| DLRK | External LRCK Div | Page 0, Register 33, D(7:0) |

8.3.6.5 PLL Calculation

The PCM514x has an on-chip PLL with fractional multiplication to generate the clock frequency needed by the audio DAC, Negative Charge Pump, Modulator and Digital Signal Processing blocks. The programmability of the PLL allows operation from a wide variety of clocks that may be available in the system. The PLL input (PLLCKIN) supports clock frequencies from 1 MHz to 50 MHz and is register programmable to enable generation of required sampling rates with fine precision.

The PLL is enabled by default. The PLL can be turned on by writing to Page 0, Register 4, D(0). When the PLL is enabled, the PLL output clock PLLCK is given by Equation 3.

where

- R = 1, 2, 3,4, ... , 15, 16

- J = 4,5,6, . . . 63, and D = 0000, 0001, 0002, . . . 9999

- K = [J value].[D value]

- P = 1, 2, 3, ... 15

R, J, D, and P are programmable. J is the integer portion of K (the numbers to the left of the decimal point), while D is the fractional portion of K (the numbers to the right of the decimal point, assuming four digits of precision).

8.3.6.5.1 Examples:

- If K = 8.5, then J = 8, D = 5000

- If K = 7.12, then J = 7, D = 1200

- If K = 14.03, then J = 14, D = 0300

- If K = 6.0004, then J = 6, D = 0004

When the PLL is enabled and D = 0000, the following conditions must be satisfied:

- 1 MHz ≤ ( PLLCKIN / P ) ≤ 20 MHz

- 64 MHz ≤ (PLLCKIN x K x R / P ) ≤ 100 MHz (in VREF mode)

- 72 MHz ≤ (PLLCKIN x K x R / P ) ≤ 86 MHz (in VCOM mode)

- 1 ≤ J ≤ 63

When the PLL is enabled and D ≠ 0000, the following conditions must be satisfied:

- 6.667 MHz ≤ PLLCLKIN / P ≤ 20 MHz

- 64 MHz ≤ (PLLCKIN x K x R / P ) ≤ 100 MHz (in VREF mode)

- 72 MHz ≤ (PLLCK IN x K x R / P ) ≤ 86 MHz (in VCOM mode)

- 4 ≤ J ≤ 11

- R = 1

When the PLL is enabled,

- fS = (PLLCLKIN × K × R) / (2048 × P)

- The value of N is selected so that fS × N = PLLCLKIN x K x R / P is in the allowable range.

Example: MCLK = 12 MHz and fS = 44.1 kHz, (N=2048)

Select P = 1, R = 1, K = 7.5264, which results in J = 7, D = 5264

Example: MCLK = 12 MHz and fS = 48.0 kHz, (N=2048)

Select P = 1, R = 1, K = 8.192, which results in J = 8, D = 1920

Values are written to the registers in Table 35.

8.3.6.5.1.1 Recommended PLL Settings

Recommended values for the PLL can be found after the register descriptions in this data sheet. Different values are defined based on the device configuration for VREF or VCOM mode.

Other configurations are possible, at your own risk.

Below are details of the register locations, as well as the nomenclature for the table of registers found at the end of this document.

Table 35. PLL Registers

| DIVIDER | FUNCTION | BITS |

|---|---|---|

| PLLE | PLL enable | Page 0, Register 4, D(0) |

| PPDV | PLL P | Page 0, Register 20, D(3:0) |

| PJDV | PLL J | Page 0, Register 21, D(5:0) |

| PDDV | PLL D | Page 0, Register 22, D(5:0) |

| Page 0, Register 23, D(7:0) | ||

| PRDV | PLL R | Page 0, Register 24, D(3:0) |

Table 36. PLL Configuration Recommendations

| COLUMN | DESCRIPTION |

|---|---|

| fS (kHz) | Sampling frequency |

| RSCK | Ratio between sampling frequency and SCK frequency (SCK frequency = RSCK × sampling frequency) |

| SCK (MHz) | System master clock frequency at SCK input (pin 20) |

| PLL VCO (MHz) | PLL VCO frequency as PLLCK in Figure 65 |

| P | One of the PLL coefficients in Equation 3 |

| PLL REF (MHz) | Internal reference clock frequency which is produced by SCK / P |

| M = K * R | The final PLL multiplication factor computed from K and R as described in Equation 3 |

| K = J.D | One of the PLL coefficients in Equation 3 |

| R | One of the PLL coefficients in Equation 3 |

| PLL fS | Ratio between fS and PLL VCO frequency (PLL VCO / fS) |

| DSP fS | Ratio between miniDSP operating clock rate and fS (PLL fS / NMAC) |

| NMAC | The miniDSP clock divider value in Table 34 |

| DSP CLK (MHz) | The miniDSP operating frequency as DSPCK in Figure 65 |

| MOD fS | Ratio between DAC operating clock frequency and fS (PLL fS / NDAC) |

| MOD f (kHz) | DAC operating frequency as DACCK in Figure 65 |

| NDAC | DAC clock divider value in Table 34 |

| DOSR | OSR clock divider value in Table 34 for generating OSRCK in Figure 65. DOSR must be chosen so that MOD fS / DOSR = 16 for correct operation. |

| NCP | NCP (negative charge pump) clock divider value in Table 34 |

| CP f | Negative charge pump clock frequency (fS × MOD fS / NCP) |

| % Error | Percentage of error between PLL VCO / PLL fS and fS (mismatch error).

|

8.3.6.6 Clock Master Mode from Audio Rate Master Clock

In Master Mode, the device generates bit clock (BCK) and left-right clock (LRCK) and outputs them on the appropriate pins. To configure the device in this mode, first put the device into reset, then use registers BCKO and LRKO (Pg 0, Reg 9 0x09). Then reset the LRCK and BCK divider counters using bits RBCK and RLRK (Pg 0, Reg 12 0x0C). Finally, exit reset.

An example of this is given in register programming examples in the PCM5242 data sheet (SLASE12.)

Figure 66 shows a simplified serial port clock tree for the device in master mode.

Figure 66. Simplified Clock Tree for SCK Sourced Master Mode

Figure 66. Simplified Clock Tree for SCK Sourced Master Mode

In master mode, SCK is an input and BCK/LRCK are outputs. BCK and LRCK are integer divisions of SCK. Master mode with a non-audio rate master clock source will require external GPIOs to use the PLL in standalone mode.

The PLL will also need to be configured to ensure that the onchip miniDSP processor can be driven at its maximum clock rate.

Register changes that need to be done include switching the device into master mode, and setting the divider ratio.

Here is an example of using 24.576 MCLK as a master clock source and driving the BCK and LRCK with integer dividers to create 48 kHz.

In this mode, the DAC section of the device is also running from the PLL output. While the PLL inside the PCM514x is one that has been specified to achieve the stated performance, using the SCK CMOS Oscillator source will have less jitter.

To switch the DAC clocks (SDAC in the Figure 65) the following registers should be modified.

- Clock Tree Flex Mode (Page 253, Registers 0x3F and 0x40)

- DAC and OSR Source Clock Register (Page 0, Reg 14) – set to 0x30 (SCK input, and OSR is set to whatever the DAC source is)

- The DAC clock divider should be 16 FS.

- 16 × 48 kHz = 768 kHz

- 24.576 MHz (SCK in) / 768 kHz = 32

- Therefor, divide ratio for register DDAC (Page 0, Reg 28 0x1C) should be set to 32. The may the register is mapped gives 0x00 = 1, so 32 must be converted to 0x1F.

An example configuration can be found in the PCM5242 data sheet (SLASE12).

8.3.6.7 Clock Master from a Non-Audio Rate Master Clock

The classic example here is running a 12-MHz Master clock for a 48-kHz sampling system. Given the clock tree for the device (shown in Figure 65), a non-audio clock rate cannot be brought into the SCK to the PLL in master mode. Therefore, the PLL source must be configured to be a GPIO pin, and the output brought back into another GPIO pin.

Figure 67. Application Diagram for Using Non-Audio Clock Sources to Generate Audio Clocks

Figure 67. Application Diagram for Using Non-Audio Clock Sources to Generate Audio Clocks

The clock flow through the system is shown in Figure 67. The newly-generated SCK must be brought out of the device on a GPIO pin, then brought into the SCK pin for integer division to create BCK and LRCK outputs.

NOTE

Pullup resistors must be used on BCK and LRCK in this mode to ensure the device does not go into sleep mode.

A code example for configuring this mode is provided in the PCM5242 data sheet (SLASE12).

8.4 Device Functional Modes

8.4.1 Choosing a Control Mode

SPI Mode is selected by connecting MODE1 to DVDD. SPI Mode uses four signal lines and allows higher-speed full-duplex communication between the host and the PCM514x device.

I2C Mode is selected by connecting MODE1 to DGND and Mode2 to DVDD. I2C uses two signal lines for half-duplex communication, and is widely used in a variety of devices.

Hardware Control Mode is selected by connecting both MODE1 and MODE2 pins to DGND. Hardware control is useful in applications that do not require on-the-fly device-reconfiguration changes in operating features such as gain or filter latency selection.

See for a comparison of pin assignments for the 28-pin TSSOP.

8.4.1.1 Software Control

8.4.1.1.1 SPI Interface

The SPI interface is a 4-wire synchronous serial port which operates asynchronously to the serial audio interface and the system clock (SCK). The serial control interface is used to program and read the on-chip mode registers.

The control interface includes MISO (pin 24), MOSI (pin 11), MC (pin 12), and MS (pin 18). MISO (Master In Slave Out) is the serial data output, used to read back the values of the mode registers; MOSI (Master Out Slave In) is the serial data input, used to program the mode registers.

MC is the serial bit clock, used to shift data in and out of the control port by falling edge of MC, and MS is the mode control enable with LOW active, used to enable the internal mode register access. If feedback from the device is not required, the MISO pin can be assigned to GPIO1 by register control.

8.4.1.1.1.1 Register Read and Write Operation

All read/write operations for the serial control port use 16-bit data words. Figure 68 shows the control data word format. The most significant bit is the read/write bit. For write operations, the bit must be set to 0. For read operations, the bit must be set to 1. There are seven bits, labeled IDX[6:0], that hold the register index (or address) for the read and write operations. The least significant eight bits, D[7:0], contain the data to be written to, or the data that was read from, the register specified by IDX[6:0].

Figure 68 and Figure 69 show the functional timing diagram to write or read through the serial control port. MS is held at a logic-1 state until a register access. To start the register write or read cycle, set MS to logic 0. Sixteen clocks are then provided on MC, corresponding to the 16 bits of the control data word on MOSI and read-back data on MISO. After the eighth clock cycle has completed, the data from the indexed-mode control register appears on MISO during the read operation. After the sixteenth clock cycle has completed, the data is latched into the indexed-mode control register during the write operation. To write or read subsequent data, MS is set to logic 1 once (see tMHH in Figure 73).

Figure 68. Control Data Word Format; MDI

Figure 68. Control Data Word Format; MDI

NOTE

B8 is used for selection of Write or Read. Setting = 0 indicates a Write, while = 1 indicates a Read. Bits 15–9 are used for register address. Bits 7–0 are used for register data. Multiple-byte write or read (up to 8 bytes) is supported while MS is kept low. The address field becomes the initial address, automatically incrementing for each byte.

Figure 69. Serial Control Format; Write, Single Byte

Figure 69. Serial Control Format; Write, Single Byte

Figure 70. Serial Control Format; Write, Multiple Byte

Figure 70. Serial Control Format; Write, Multiple Byte

Figure 71. Serial Control Format; Read

Figure 71. Serial Control Format; Read

Figure 72. Serial Control Format; Read, Multiple Byte

Figure 72. Serial Control Format; Read, Multiple Byte

Figure 73. Control Interface Timing

Figure 73. Control Interface Timing

Table 37. Control Interface Timing

| MIN | MAX | UNIT | ||

|---|---|---|---|---|

| tMCY | MC Pulse Cycle Time | 100 | ns | |

| tMCL | MC Low Level Time | 40 | ns | |

| tMCH | MC High Level Time | 40 | ns | |

| tMHH | MS High Level Time | 20 | ns | |

| tMSS | MS ↓ Edge to MC ↑ Edge | 30 | ns | |

| tMSH | MS Hold Time(1) | 30 | ns | |

| tMDH | MDI Hold Time | 15 | ns | |

| tMDS | MDI Set-up Time | 15 | ns | |

| tMOS | MC Rise Edge to MDO Stable | 20 | ns | |

8.4.1.1.2 I2C Interface

The PCM514x supports the I2C serial bus and the data transmission protocol for standard and fast mode as a slave device.

In I2C mode, the control terminals are changed as follows.

Table 38. I2C Pins and Functions

| SIGNAL | PIN | I/O | DESCRIPTION |

|---|---|---|---|

| SDA | 11 | I/O | I2C data |

| SCL | 12 | I | I2C clock |

| ADR2 | 16 | I | I2C address 2 |

| ADR1 | 24 | I | I2C address 1 |

8.4.1.1.2.1 Slave Address

Table 39. I2C Slave Address

| MSB | LSB | ||||||

| 1 | 0 | 0 | 1 | 1 | ADR2 | ADR1 | R/ W |

The PCM514x has 7 bits for its own slave address. The first five bits (MSBs) of the slave address are factory preset to 10011 (0x9x). The next two bits of the address byte are the device select bits which can be user-defined by the ADR1 and ADR0 terminals. A maximum of four devices can be connected on the same bus at one time. This gives a range of 0x98, 0x9A, 0x9C and 0x9E. Each PCM514x responds when it receives its own slave address.

8.4.1.1.2.2 Register Address Auto-Increment Mode

Figure 74. Auto Increment Mode

Figure 74. Auto Increment Mode

Auto-increment mode allows multiple sequential register locations to be written to or read back in a single operation, and is especially useful for block write and read operations.

8.4.1.1.2.3 Packet Protocol

A master device must control packet protocol, which consists of start condition, slave address, read/write bit, data if write or acknowledge if read, and stop condition. The PCM514x supports only slave receivers and slave transmitters.

Figure 75. Packet Protocol

Figure 75. Packet Protocol

Table 40. Write Operation - Basic I2C Framework

| Transmitter | M | M | M | S | M | S | M | S | S | M | |

| Data Type | St | slave address | R/ | ACK | DATA | ACK | DATA | ACK | ACK | Sp |

Table 41. Read Operation - Basic I2C Framework

| Transmitter | M | M | M | S | S | M | S | M | M | M | |

| Data Type | St | slave address | R/ | ACK | DATA | ACK | DATA | ACK | NACK | Sp |

M = Master Device; S = Slave Device; St = Start Condition; Sp = Stop Condition

8.4.1.1.2.4 Write Register

A master can write to any PCM514x registers using single or multiple accesses. The master sends a PCM514x slave address with a write bit, a register address with auto-increment bit, and the data. If auto-increment is enabled, the address is that of the starting register, followed by the data to be transferred. When the data is received properly, the index register is incremented by 1 automatically. When the index register reaches 0x7F, the next value is 0x0. Table 42 shows the write operation.

Table 42. Write Operation

| Transmitter | M | M | M | S | M | S | M | S | M | S | S | M | ||

| Data Type | St | slave addr | W | ACK | inc | reg addr | ACK | write data 1 | ACK | write data 2 | ACK | ACK | Sp | |

M = Master Device; S = Slave Device; St = Start Condition; Sp = Stop Condition; W = Write; ACK = Acknowledge

8.4.1.1.2.5 Read Register

A master can read the PCM514x register. The value of the register address is stored in an indirect index register in advance. The master sends a PCM514x slave address with a read bit after storing the register address. Then the PCM514x transfers the data which the index register points to. When auto-increment is enabled, the index register is incremented by 1 automatically. When the index register reaches 0x7F, the next value is 0x0. Table 43 shows the read operation.

Table 43. Read Operation

| Transmitter | M | M | M | S | M | S | M | M | M | S | S | M | M | M | ||

| Data Type | St | slave addr | W | ACK | inc | reg addr | ACK | Sr | slave addr | R | ACK | data | ACK | NACK | Sp | |

M = Master Device; S = Slave Device; St = Start Condition; Sr = Repeated Start Condition; Sp = Stop Condition; W = Write; R = Read; NACK = Not acknowledge

8.4.1.1.2.6 Timing Characteristics

Figure 76. Register Access Timing

Figure 76. Register Access Timing

Table 44. I2C Bus Timing

| MIN | MAX | UNIT | |||

|---|---|---|---|---|---|

| fSCL | SCL clock frequency | Standard | 100 | kHz | |

| Fast | 400 | kHz | |||

| tBUF | Bus free time between a STOP and START condition | Standard | 4.7 | µs | |

| Fast | 1.3 | ||||

| tLOW | Low period of the SCL clock | Standard | 4.7 | µs | |

| Fast | 1.3 | ||||

| tHI | High period of the SCL clock | Standard | 4.0 | µs | |

| Fast | 600 | ns | |||

| tRS-SU | Setup time for (repeated)START condition | Standard | 4.7 | µs | |

| Fast | 600 | ns | |||

| tS-HD | Hold time for (repeated)START condition | Standard | 4.0 | µs | |

| tRS-HD | Fast | 600 | ns | ||

| tD-SU | Data setup time | Standard | 250 | ns | |

| Fast | 100 | ||||

| tD-HD | Data hold time | Standard | 0 | 900 | ns |

| Fast | 0 | 900 | |||

| tSCL-R | Rise time of SCL signal | Standard | 20 + 0.1CB | 1000 | ns |

| Fast | 20 + 0.1CB | 300 | |||

| tSCL-R1 | Rise time of SCL signal after a repeated START condition and after an acknowledge bit | Standard | 20 + 0.1CB | 1000 | ns |

| Fast | 20 + 0.1CB | 300 | |||

| tSCL-F | Fall time of SCL signal | Standard | 20 + 0.1CB | 1000 | ns |

| Fast | 20 + 0.1CB | 300 | |||

| tSDA-R | Rise time of SDA signal | Standard | 20 + 0.1CB | 1000 | ns |

| Fast | 20 + 0.1CB | 300 | |||

| tSDA-F | Fall time of SDA signal | Standard | 20 + 0.1CB | 1000 | ns |

| Fast | 20 + 0.1CB | 300 | |||

| tP-SU | Setup time for STOP condition | Standard | 4.0 | µs | |

| Fast | 600 | ns | |||

| CB | Capacitive load for SDA and SCL line | 400 | pF | ||

| tSP | Pulse width of spike suppressed | Fast | 50 | ns | |

| VNH | Noise margin at High level for each connected device (including hysteresis) | 0.2 × VDD | V | ||

8.4.2 VREF and VCOM Modes

See Choosing Between VREF and VCOM Modes for information on configuring these modes.

8.5 Programming

In software mode, the PCM514x can act as an I2S master, generating BCK and LRCK as outputs from the SCK input.

Table 45. I2S Master Mode Registers

| REGISTER | FUNCTION |

|---|---|

| Page0, Register 9, D(0), D(4), and D(5) | I2S Master mode select |

| Register 32, D(6:0) | BCK divider and LRCK divider |

| Register 33, D(7:0) |