ZHCS826C January 2012 – November 2023 TPS40170-Q1

PRODUCTION DATA

- 1

- 1 特性

- 2 应用

- 3 说明

- 4 Pin Configuration and Functions

- 5 Specifications

-

6 Detailed Description

- 6.1 Overview

- 6.2 Functional Block Diagram

- 6.3

Feature Description

- 6.3.1 LDO Linear Regulators and Enable

- 6.3.2 Input Undervoltage Lockout (UVLO)

- 6.3.3 Equations for Programming the Input UVLO

- 6.3.4 Overcurrent Protection and Short-Circuit Protection (OCP and SCP)

- 6.3.5 Oscillator and Voltage Feed-Forward

- 6.3.6 Feed-Forward Oscillator Timing Diagram

- 6.3.7 Soft-Start and Fault-Logic

- 6.3.8 Overtemperature Fault

- 6.3.9 Tracking

- 6.3.10 Adaptive Drivers

- 6.3.11 Start-Up Into Pre-Biased Output

- 6.3.12 31

- 6.3.13 Power Good (PGOOD)

- 6.3.14 PGND and AGND

- 6.3.15 Bootstrap Capacitor

- 6.3.16 Bypass and Filtering

- 6.4 Device Functional Modes

-

7 Application and Implementation

- 7.1 Application Information

- 7.2

Typical Application

- 7.2.1 Design Requirements

- 7.2.2

Detailed Design Procedure

- 7.2.2.1 Select A Switching Frequency

- 7.2.2.2 Inductor Selection (L1)

- 7.2.2.3 Output Capacitor Selection (C9)

- 7.2.2.4 Peak Current Rating of Inductor

- 7.2.2.5 Input Capacitor Selection (C1, C6)

- 7.2.2.6 MOSFET Switch Selection (Q1, Q2)

- 7.2.2.7 Timing Resistor (R7)

- 7.2.2.8 UVLO Programming Resistors (R2, R6)

- 7.2.2.9 Bootstrap Capacitor (C7)

- 7.2.2.10 VIN Bypass Capacitor (C18)

- 7.2.2.11 VBP Bypass Capacitor (C19)

- 7.2.2.12 SS Timing Capacitor (C15)

- 7.2.2.13 ILIM Resistor (R19, C17)

- 7.2.2.14 SCP Multiplier Selection (R5)

- 7.2.2.15 Feedback Divider (R10, R11)

- 7.2.2.16 Compensation: (R4, R13, C13, C14, C21)

- 7.2.3 Application Curves

- 7.3 Power Supply Recommendations

- 7.4 Layout

- 8 Device and Documentation Support

- 9 Revision History

- 10Mechanical, Packaging, and Orderable Information

6.3.11 Start-Up Into Pre-Biased Output

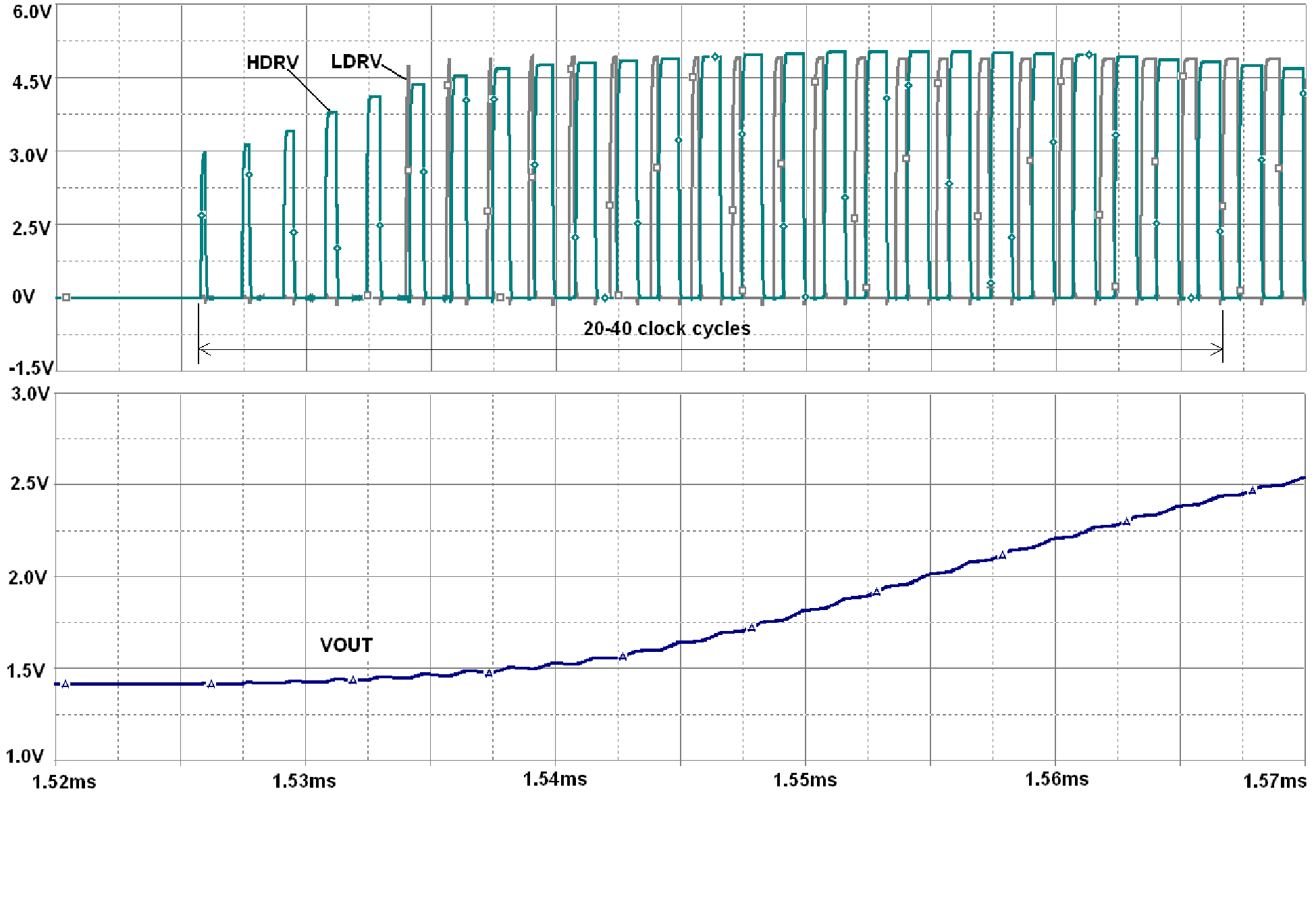

The TPS40170-Q1 device contains a circuit to prevent current from being pulled out of the output during startup, in case the output is pre-biased. When the soft-start commands a voltage higher than the pre-bias level (internal soft-start becomes greater than feedback voltage [VVFB]), the controller slowly activates synchronous rectification by starting the first LDRV pulses with a narrow on-time (see Figure 6-16), where:

- VIN = 5 V

- VOUT = 3.3 V

- VPRE = 1.4 V

- fSW = 300 kHz

- L = 0.6 µH

LDRV pulses then increments the on-time on a cycle-by-cycle basis until it coincides with the time dictated by (1 – D), where D is the duty cycle of the converter. This scheme prevents the initial sinking of the pre-bias output, and ensures that the output voltage (VOUT) starts and ramps up smoothly into regulation and the control loop is given time to transition from pre-biased startup to normal mode operation with minimal disturbance to the output voltage. The time from the start of switching until the low-side MOSFET is turned on for the full (1 – D) interval is between approximately 20 and 40 clock cycles.

Figure 6-16 Start-Up Switching Waveform During Pre-Biased Condition

Figure 6-16 Start-Up Switching Waveform During Pre-Biased Condition