ZHCSCY0 October 2014 TMS570LS0232

PRODUCT PREVIEW Information. Product in design phase of development. Subject to change or discontinuance without notice.

- 1器件概述

- 2修订历史记录

-

3器件封装和引脚功能

- 3.1 PZ QFP 封装引脚分配(100 引脚)

- 3.2

引脚配置和功能

- 3.2.1 高端定时器 (N2HET)

- 3.2.2 增强型正交编码器脉冲模块 (eQEP)

- 3.2.3 通用输入/输出 (GIO)

- 3.2.4 控制器局域网络接口模块 (DCAN1,DCAN2)

- 3.2.5 多缓冲串行外设接口 (MibSPI1)

- 3.2.6 标准串行外设接口 (SPI2)

- 3.2.7 本地互连网络控制器 (LIN)

- 3.2.8 多缓冲模数转换器 (MibADC)

- 3.2.9 系统模块

- 3.2.10 错误信令模块 (ESM)

- 3.2.11 主振荡器

- 3.2.12 测试/调试接口

- 3.2.13 闪存

- 3.2.14 内核电源

- 3.2.15 I/O 电源

- 3.2.16 内核和 I/O 电源接地基准

- 3.3 输出复用和控制

- 3.4 特定复用选项

- 4规范

- 5系统信息和电气技术规范

- 6外设信息和电气技术规范

- 7器件和文档支持

- 8机械、封装和可订购米6体育平台手机版_好二三四附录

7 器件和文档支持

7.1 器件支持

7.1.1 开发支持

米6体育平台手机版_好二三四 (TI) 为 Hercules™ 安全 MCU 系列米6体育平台手机版_好二三四提供了大量的开发工具,其中包括评估处理器性能、生成代码、开发算法执行的工具,以及完全集成和调试的软件和硬件模块。

下列米6体育平台手机版_好二三四支持基于 Hercules™ 应用的开发:

软件开发工具

- Code Composer Studio™ 集成开发环境 (IDE)

- C/C++ 编译器

- 代码生成工具

- 汇编器/连接器

- 周期精确模拟器

- 应用算法

- 示例应用代码

硬件开发工具

- 开发和评估板

- 基于 JTAG 的仿真器 - XDS100™v2、XDS200、 XDS560™ v2 仿真器

- 闪存编程工具

- 电源

- 文档和线缆

7.1.1.1 开始使用

这个部分给出了首次进行开发 TMS570 MCU 器件的步骤简介。 有关这些步骤的详细信息,请参阅以下内容:

- 《Hercules™ ARM® Cortex®-R4F 微控制器的初始化》(SPNA106)

7.1.2 器件命名规则

为了指明米6体育平台手机版_好二三四开发周期的阶段,TI 为所有器件的部件号分配了前缀。 每个商用系列米6体育平台手机版_好二三四都有这三个前缀中的一个:TMX,TMP 或 TMS。这些前缀代表了米6体育平台手机版_好二三四开发的发展阶段,即从工程原型 (TMX) 直到完全合格的生产器件 (TMS)。

-

TMX 试验器件不一定代表最终器件的电气规范标准。

-

TMP 最终的芯片模型符合器件的电气技术规范,但是未经完整的质量和可靠性验证。

-

TMS 完全合格的生产器件。

TMX 和 TMP 器件在供货时附带如下免责条款:

“开发的米6体育平台手机版_好二三四用于内部评估用途。”

TMS 器件已进行完全特性描述,并且器件的质量和可靠性已经完全论证。 TI 的标准保修证书适用。

预测显示原型器件(TMX 或者 TMP)的故障率大于标准生产器件。 由于它们的预计的最终使用故障率仍未定义,米6体育平台手机版_好二三四建议不要将这些器件用于任何生产系统。 只有合格的米6体育平台手机版_好二三四器件将被使用。

Figure 7-1给出了 TMS570LS0232 的编号和符号命名规则。

Figure 7-1 器件编号惯例

Figure 7-1 器件编号惯例

7.2 文档支持

7.3 社区资源

下列链接提供到 TI 社区资源的连接。 链接的内容由各个分销商“按照原样”提供。 这些内容并不构成 TI 技术规范和标准且不一定反映 TI 的观点;请见 TI 的使用条款。

-

TI E2E™ 在线社区 TI 工程师对工程师 (E2E) 社区。 此社区的创建目的是为了促进工程师之间协作。 在 e2e.ti.com 中,您可以咨询问题、共享知识、探索思路,在同领域工程师的帮助下解决问题。

-

米6体育平台手机版_好二三四 (TI) 嵌入式处理器维基网站 米6体育平台手机版_好二三四 (TI) 嵌入式处理器维基网站。 此网站的建立是为了帮助开发人员从米6体育平台手机版_好二三四 (TI) 的嵌入式处理器入门并且也为了促进与这些器件相关的硬件和软件的总体知识的创新和增长。

7.4 商标

Hercules, Code Composer Studio, XDS100, XDS560, E2E are trademarks of Texas Instruments.

ARM, Cortex are registered trademarks of ARM Limited (or its subsidiaries) in the EU and.

CoreSight is a trademark of ARM Limited.

7.5 静电放电警告

ESD 可能会损坏该集成电路。米6体育平台手机版_好二三四 (TI) 建议通过适当的预防措施处理所有集成电路。如果不遵守正确的处理措施和安装程序 , 可能会损坏集成电路。

ESD 的损坏小至导致微小的性能降级 , 大至整个器件故障。 精密的集成电路可能更容易受到损坏 , 这是因为非常细微的参数更改都可能会导致器件与其发布的规格不相符。

7.7 器件识别码寄存器

该器件识别码寄存器确定了器件的几个方面,包括芯片版本。 器件识别码寄存器的详细信息显示在Table 7-1中。 该器件的器件识别码寄存器值是:

- 版本 0 = 0x8048AD05

- 版本 A = 0x8048AD0D

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| CP-15 | 唯一 ID | 技术 | |||||||||||||

| R-1 | R-00000000100100 | R-0 | |||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| TECH | I/O 电压 | 外设奇偶校验 | 闪存 ECC | RAM ECC | 版本 | 1 | 0 | 1 | |||||||

| R-101 | R-0 | R-1 | R-10 | R-1 | R-00001 | R-1 | R-0 | R-1 | |||||||

| 图例:R/W = 读/写;R = 只读;-n = 复位后的值 |

Table 7-1 器件 ID 位分配寄存器字段说明

| 位 | 字段 | 值 | 说明 |

|---|---|---|---|

| 31 | CP15 | 表明协同处理器 15 的存在 | |

| 1 | CP15 存在 | ||

| 30-17 | 唯一 ID | 100100 |

芯片版本(修订版)位。 此位字段拥有一个针对专用器件配置(芯片)的唯一编号。 |

| 16-13 | TECH | 器件的生产工艺。 | |

| 0101 | F021 | ||

| 12 | I/O 电压 | 该器件的 I/O 电压。 | |

| 0 | I/O 是 3.3v | ||

| 11 | 外设奇偶校验 | 外设奇偶校验 | |

| 1 | 外设存储器的奇偶校验 | ||

| 10-9 | 闪存 ECC | 闪存 ECC | |

| 10 | 带 ECC 的程序存储器 | ||

| 8 | RAM ECC | 表示 RAM 内存 ECC 是否存在。 | |

| 1 | ECC 被执行 | ||

| 7-3 | 修订版本 | 0 | 该器件的修订版本。 |

| 2-0 | 系列 ID | 101 | 平台系列 ID 一直是 0b101 |

7.8 芯片识别寄存器

位于地址 0xFFFFFF7C 和 0xFFFFFF80 的两个芯片 ID 寄存器构成了一个 64 位芯片 ID,其中含有如Table 7-2 所示的信息。

Table 7-2 芯片 - ID 寄存器

| 项目 | 位编号 | 位位置 |

|---|---|---|

| 晶圆上的 X 坐标 | 12 | 0xFFFFFF7C[11:0] |

| 晶圆上的Y 坐标 | 12 | 0xFFFFFF7C[23:12] |

| 晶圆 # | 8 | 0xFFFFFF7C[31:24] |

| 批号 # | 24 | 0xFFFFFF80[23:0] |

| 被保留 | 8 | 0xFFFFFF80[31:24] |

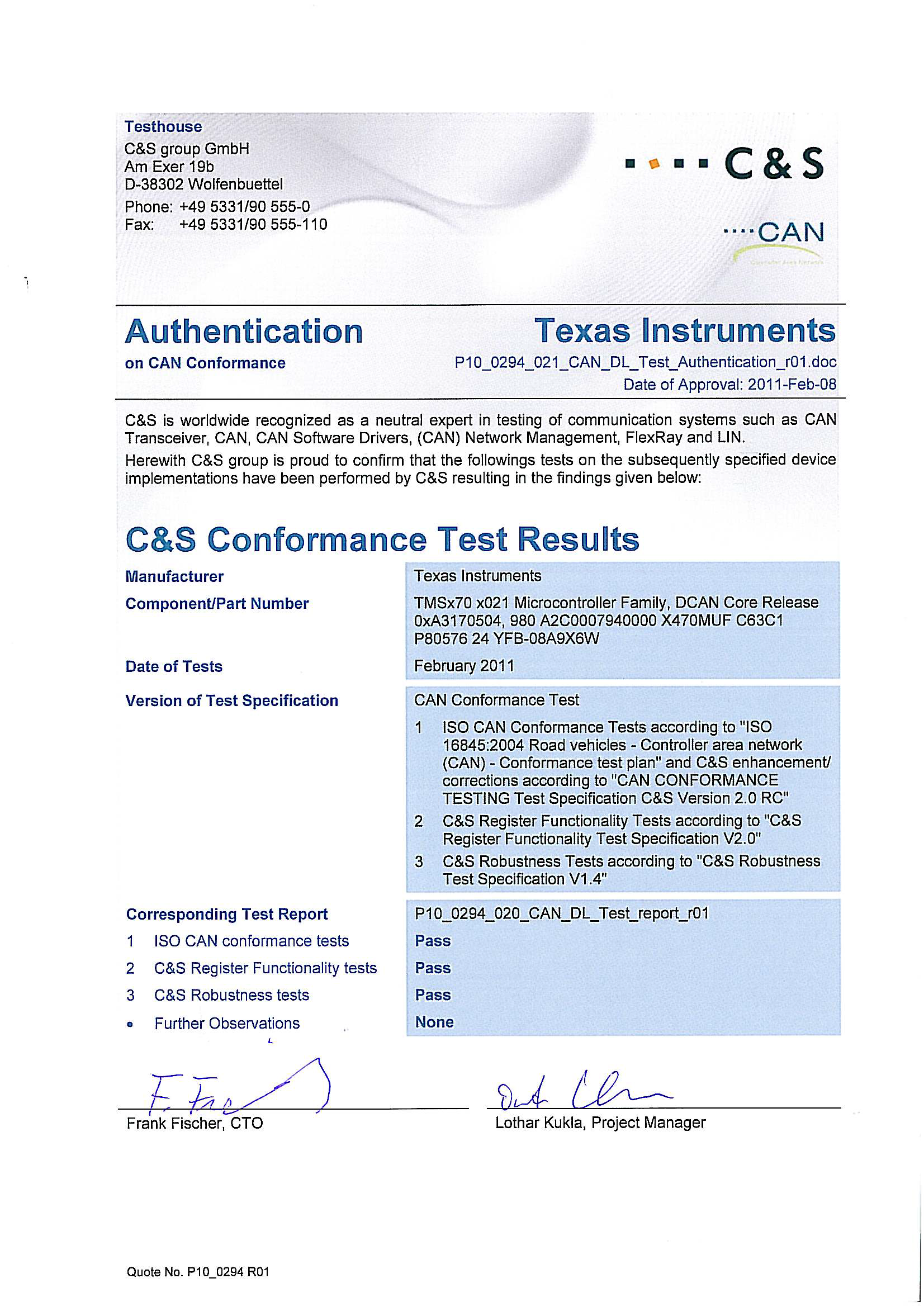

7.9 模块认证

以下通信模块已经被授予遵守标准的认证。

7.9.1 DCAN 认证

Figure 7-3 DCAN 认证

Figure 7-3 DCAN 认证

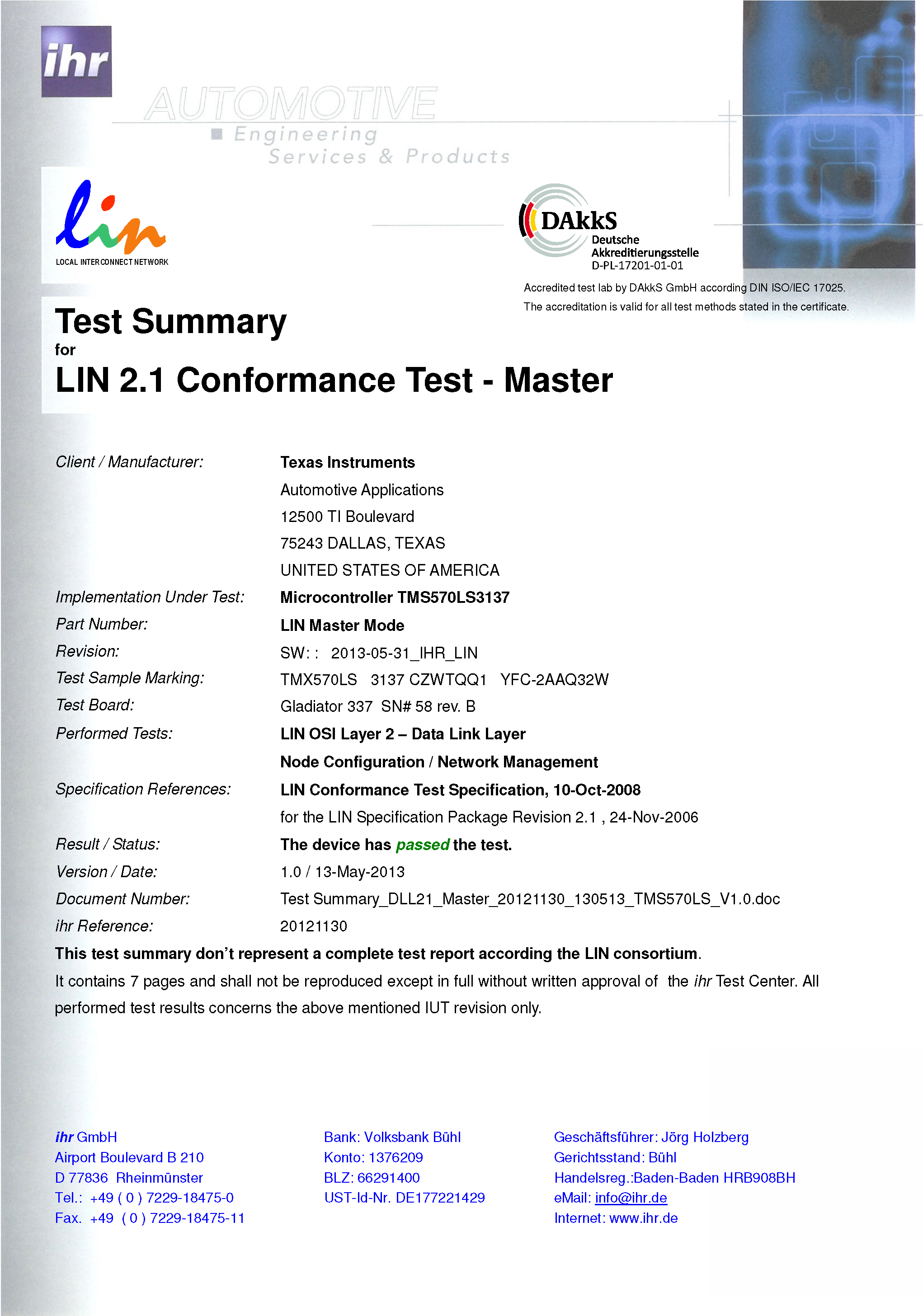

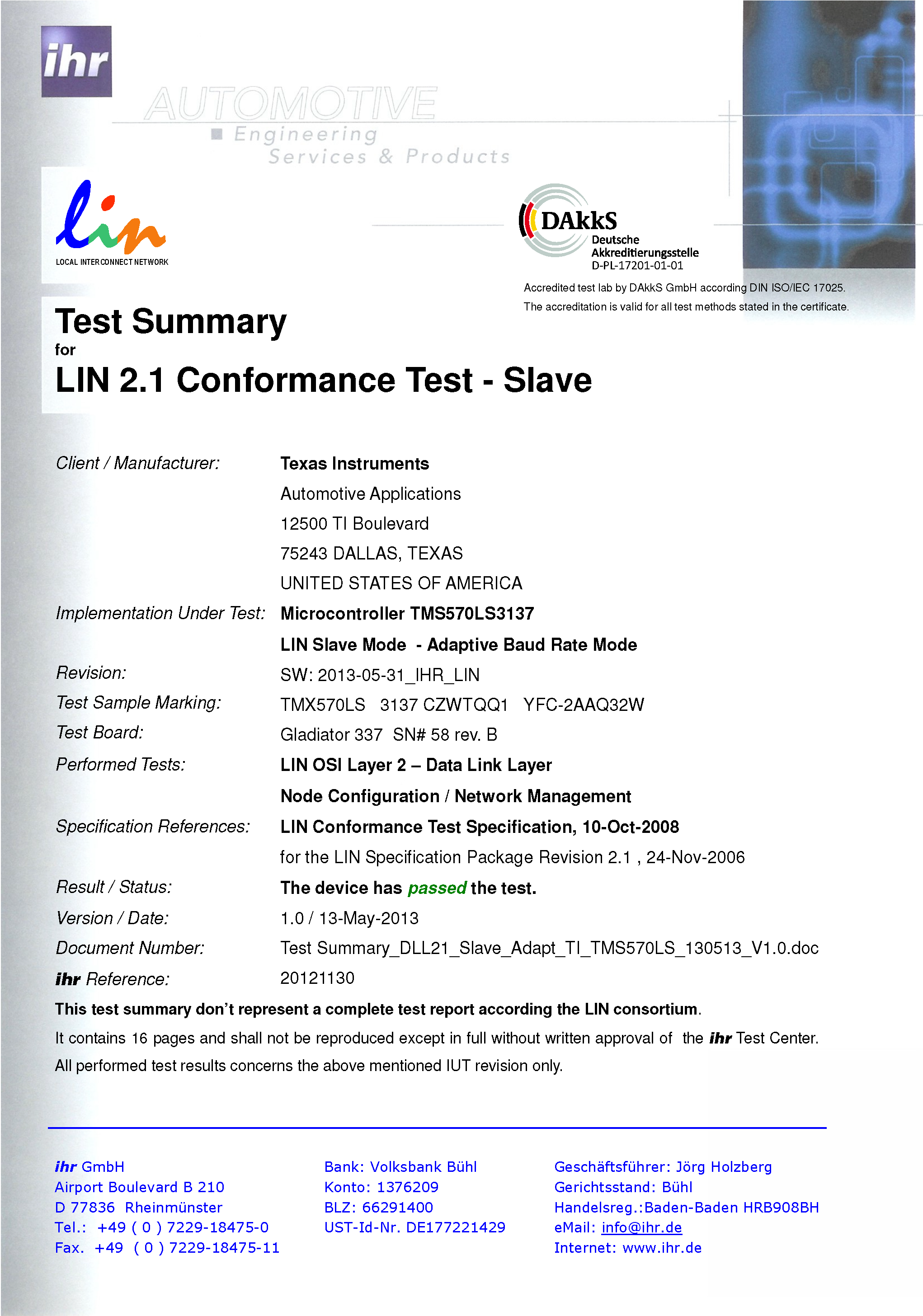

7.9.2 LIN 认证

7.9.2.1 LIN 主控模式

Figure 7-4 LIN 认证 - 主控模式

Figure 7-4 LIN 认证 - 主控模式

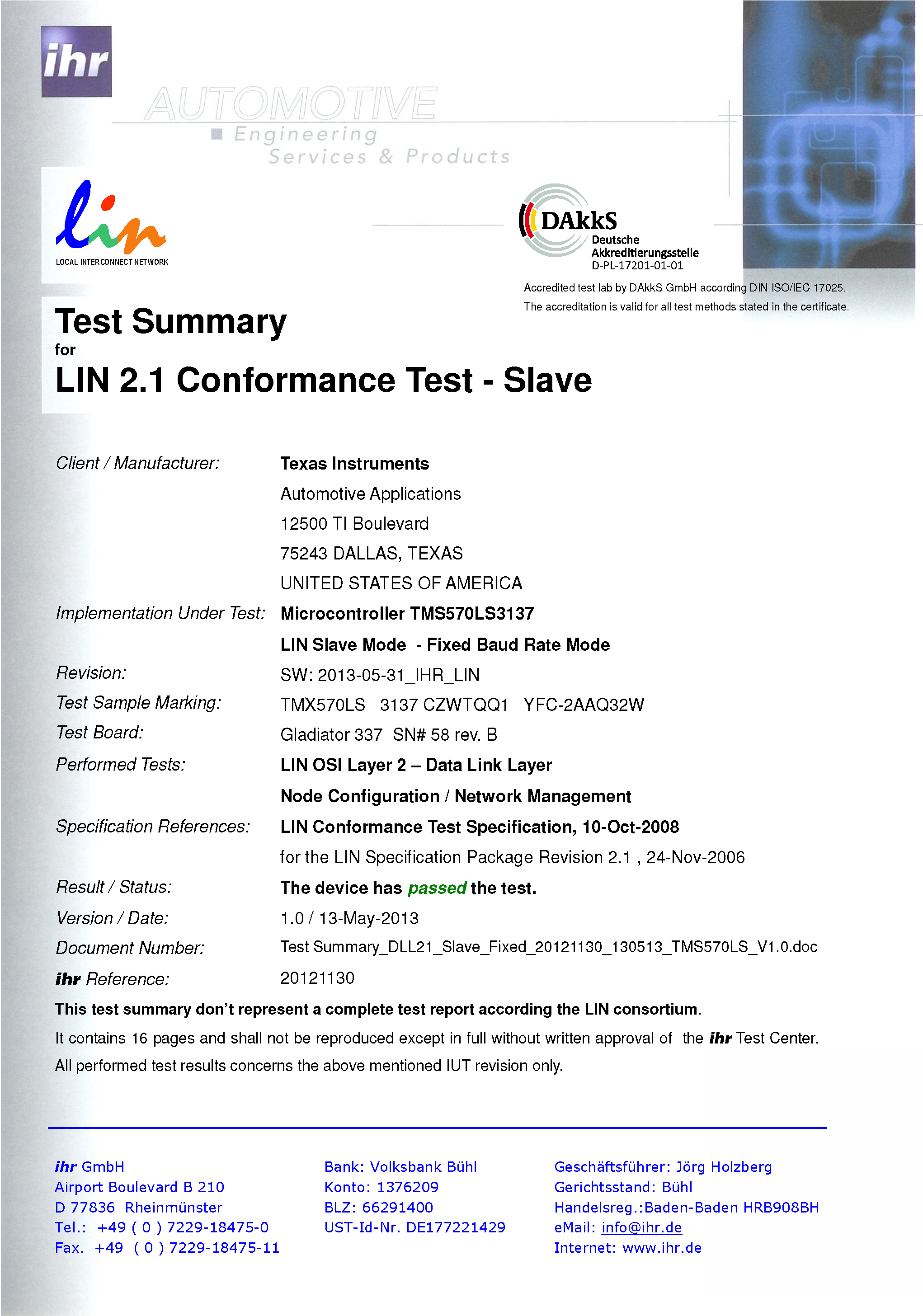

7.9.2.2 LIN 受控模式 - 固定波特率

Figure 7-5 LIN 认证 - 受控模式 - 固定波特率

Figure 7-5 LIN 认证 - 受控模式 - 固定波特率

7.9.2.3 LIN 受控模式 - 自适应波特率

Figure 7-6 LIN 认证 - 受控模式 - 自适应波特率

Figure 7-6 LIN 认证 - 受控模式 - 自适应波特率