ZHCSD61L July 2012 – May 2019 LP8556

PRODUCTION DATA.

- 1 特性

- 2 应用

- 3 说明

- 4 修订历史记录

- 5 Device Options

- 6 Pin Configuration and Functions

-

7 Specifications

- 7.1 Absolute Maximum Ratings

- 7.2 ESD Ratings

- 7.3 Recommended Operating Conditions

- 7.4 Thermal Information

- 7.5 Electrical Characteristics

- 7.6 Electrical Characteristics — Boost Converter

- 7.7 Electrical Characteristics — LED Driver

- 7.8 Electrical Characteristics — PWM Interface

- 7.9 Electrical Characteristics — Logic Interface

- 7.10 I2C Serial Bus Timing Parameters (SDA, SCL)

- 7.11 Typical Characteristics

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3

Feature Description

- 8.3.1 Boost Converter

- 8.3.2 Brightness Control

- 8.3.3 Fault Detection

- 8.4 Device Functional Modes

- 8.5 Programming

- 8.6

Register Maps

- 8.6.1 Register Bit Explanations

- 8.6.2

EPROM Bit Explanations

- 8.6.2.1 LP8556TM (DSBGA) Configurations and Pre-Configured EPROM Settings

- 8.6.2.2 LP8556TM (DSBGA) Configurations and Pre-configured EPROM Settings Continued

- 8.6.2.3 LP8556SQ (WQFN) Configurations and Pre-configured EPROM Settings

- 8.6.2.4 CFG98

- 8.6.2.5 CFG9E

- 8.6.2.6 CFG0

- 8.6.2.7 CFG1

- 8.6.2.8 CFG2

- 8.6.2.9 CFG3

- 8.6.2.10 CFG4

- 8.6.2.11 CFG5

- 8.6.2.12 CFG6

- 8.6.2.13 CFG7

- 8.6.2.14 CFG9

- 8.6.2.15 CFGA

- 8.6.2.16 CFGE

- 8.6.2.17 CFGF

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12器件和文档支持

- 13机械、封装和可订购信息

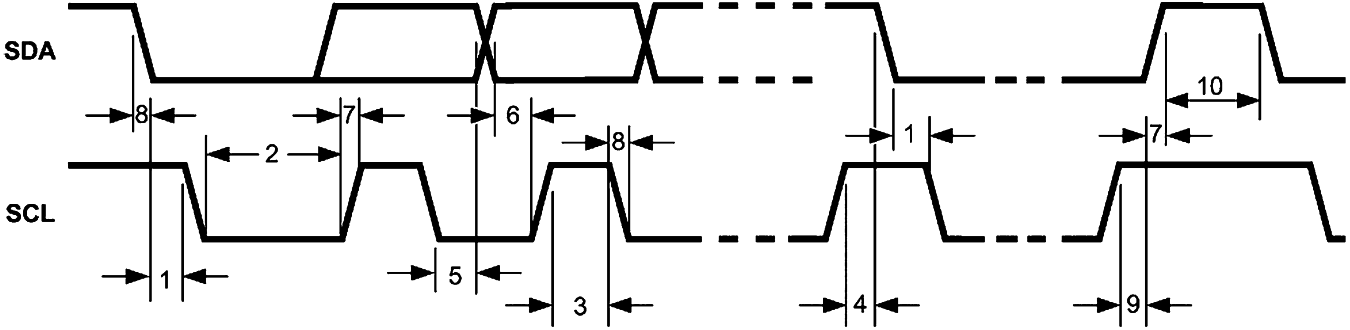

7.10 I2C Serial Bus Timing Parameters (SDA, SCL)(1)

| MIN | MAX | UNIT | ||

|---|---|---|---|---|

| ƒSCL | Clock frequency | 400 | kHz | |

| 1 | Hold time (repeated) START condition | 0.6 | µs | |

| 2 | Clock low time | 1.3 | µs | |

| 3 | Clock high time | 600 | ns | |

| 4 | Setup time for a repeated START condition | 600 | ns | |

| 5 | Data hold time | 50 | ns | |

| 6 | Data set-up time | 100 | ns | |

| 7 | Rise time of SDA and SCL | 20 + 0.1Cb | 300 | ns |

| 8 | Fall time of SDA and SCL | 15 + 0.1Cb | 300 | ns |

| 9 | Setup time for STOP condition | 600 | ns | |

| 10 | Bus-free time between a STOP and a START condition | 1.3 | µs | |

| Cb | Capacitive load parameter for each bus line load of 1 pF corresponds to 1 ns. | 10 | 200 | ns |

(1) Verified by design and not tested in production.

Figure 1. I2C-Compatible Timing

Figure 1. I2C-Compatible Timing