ZHCSIU6F September 2018 – June 2021 TPS2663

PRODUCTION DATA

- 1 特性

- 2 应用

- 3 说明

- 4 Revision History

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Parameter Measurement Information

-

9 Detailed Description

- 9.1 Overview

- 9.2 Functional Block Diagram

- 9.3

Feature Description

- 9.3.1 Hot Plug-In and In-Rush Current Control

- 9.3.2 PGOOD and PGTH

- 9.3.3 Undervoltage Lockout (UVLO)

- 9.3.4 Overvoltage Protection (OVP)

- 9.3.5 Input Reverse Polarity Protection (B_GATE, DRV)

- 9.3.6 Reverse Current Protection

- 9.3.7 Overload and Short Circuit Protection

- 9.3.8 Output Power Limiting, PLIM (TPS26632, TPS26633, TPS26635 and TPS26636 Only)

- 9.3.9 Current Monitoring Output (IMON)

- 9.3.10 FAULT Response ( FLT)

- 9.3.11 IN_SYS, IN, OUT and GND Pins

- 9.3.12 Thermal Shutdown

- 9.3.13 Low Current Shutdown Control (SHDN)

- 9.4 Device Functional Modes

-

10Application and Implementation

- 10.1 Application Information

- 10.2

Typical Application: Power Path Protection in a PLC System

- 10.2.1 Design Requirements

- 10.2.2 Detailed Design Procedure

- 10.2.3 Application Curves

- 10.3 System Examples

- 10.4 Do's and Don'ts

- 11Power Supply Recommendations

- 12Layout

- 13Device and Documentation Support

- 14Mechanical, Packaging, and Orderable Information

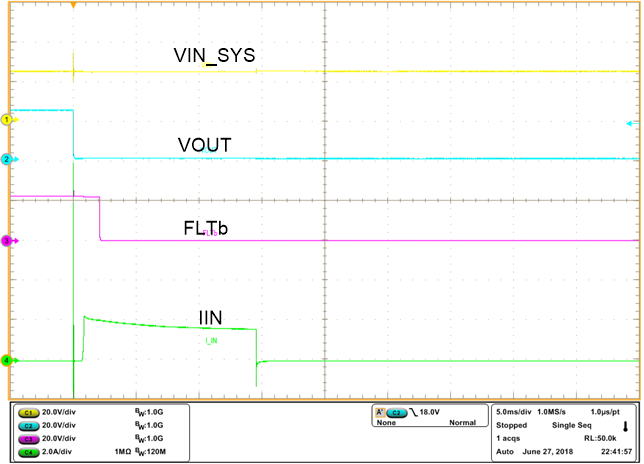

9.3.7.2 Short Circuit Protection

During a transient output short circuit event, the current through the device increases rapidly. As the current-limit amplifier cannot respond quickly to this event due to its limited bandwidth, the device incorporates a fast-trip comparator. The fast-trip comparator architecture is designed for fast turn OFF tFASTTRIP(dly) = 1 µs (typical) with I(SCP) = 45 A of the internal FET during an output short circuit event. The fast-trip threshold is internally set to I(FASTTRIP). The fasttrip circuit holds the internal FET off for only a few microseconds, after which the device turns back on slowly, allowing the current-limit loop to regulate the output current to I(OL). Then the device functions similar to the overload condition. Figure 8-14 illustrates output hot-short performance of the device.

| VIN_SYS = 24 V | RILIM = 9.09 kΩ | |

The fast-trip comparator architecture has a supply line noise immunity resulting in a robust performance in noisy environments. This is achieved by controlling the turn OFF time of the internal FET based on the overcurrent level, I(FASTTRIP) through the device. Higher the overcurrent, faster the turn OFF time, tFASTTRIP(dly). At overload current level in the range of IFASTTRIP < IOUT < ISCP the fast-trip comparator response is 3.2 μs (typical).