ZHCSPG5 December 2021 DAC11001B

PRODUCTION DATA

- 1 特性

- 2 应用

- 3 说明

- 4 Revision History

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Thermal Information

- 6.5 Electrical Characteristics

- 6.6 Timing Requirements: Write, 4.5 V ≤ DVDD ≤ 5.5 V

- 6.7 Timing Requirements: Write, 2.7 V ≤ DVDD < 4.5 V

- 6.8 Timing Requirements: Read and Daisy-Chain Write, 4.5 V ≤ DVDD ≤ 5.5 V

- 6.9 Timing Requirements: Read and Daisy-Chain Write, 2.7 V ≤ DVDD < 4.5 V

- 6.10 Timing Diagrams

- 6.11 Typical Characteristics

-

7 Detailed Description

- 7.1 Overview

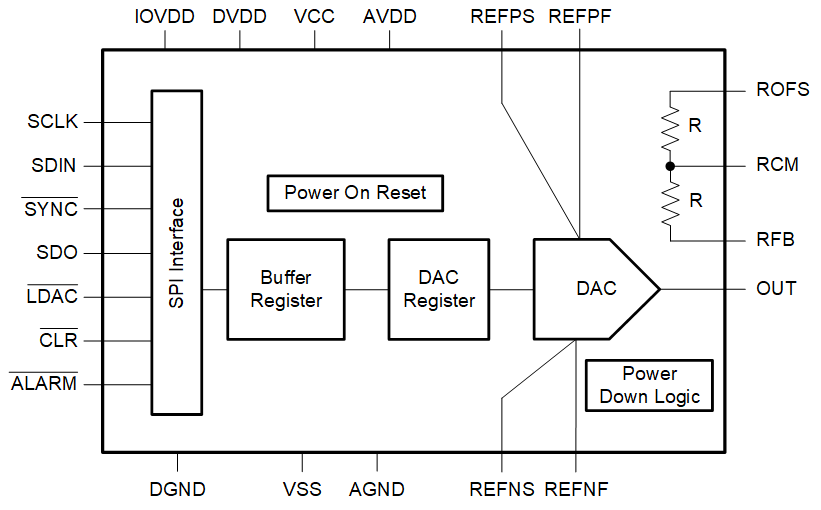

- 7.2 Functional Block Diagram

- 7.3 Feature Description

- 7.4 Device Functional Modes

- 7.5 Programming

- 7.6

Register Map

- 7.6.1 NOP Register (address = 00h) [reset = 0x000000h for bits [23:0]]

- 7.6.2 DAC-DATA Register (address = 01h) [reset = 0x000000h for bits [23:0]]

- 7.6.3 CONFIG1 Register (address = 02h) [reset = 004C80h for bits [23:0]]

- 7.6.4 DAC-CLEAR-DATA Register (address = 03h) [reset = 000000h for bits [23:0]]

- 7.6.5 TRIGGER Register (address = 04h) [reset = 000000h for bits [23:0]]

- 7.6.6 STATUS Register (address = 05h) [reset = 000000h for bits [23:0]]

- 7.6.7 CONFIG2 Register (address = 06h) [reset = 000040h for bits [23:0]]

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

3 说明

20 位 DAC11001B 是一款高精度、低噪声、电压输出、单通道数模转换器 (DAC)。DAC11001B 根据设计具有单调性,并可在所有输出范围内提供出色的线性度。

非缓冲电压输出可提供低噪声性能 (7nV/√Hz) 和快速稳定时间 (1µs),因此这款器件非常适合低噪声、快速控制环路和波形生成应用。DAC11001B 兼具增强型抗尖峰脉冲电路以及独立于代码的超低干扰 (1nV-s),可实现干净的波形斜坡和超低总谐波失真 (THD)。

DAC11001B 器件包含上电复位电路,因此 DAC 上电时使用寄存器中的已知值。使用外部基准,可以实现 VREFPF 到 VREFNF 的 DAC 输出,包括非对称输出范围。

DAC11001B 使用一个以高达 50MHz 的时钟速率运行的多功能 4 线制串行接口。

器件信息

| 器件型号 | 封装(1) | 封装尺寸(标称值) |

|---|---|---|

| DAC11001B | TQFP (48) | 7.00mm × 7.00mm |

(1) 要了解所有可用封装,请参见数据表末尾的封装选项附录。

功能方框图

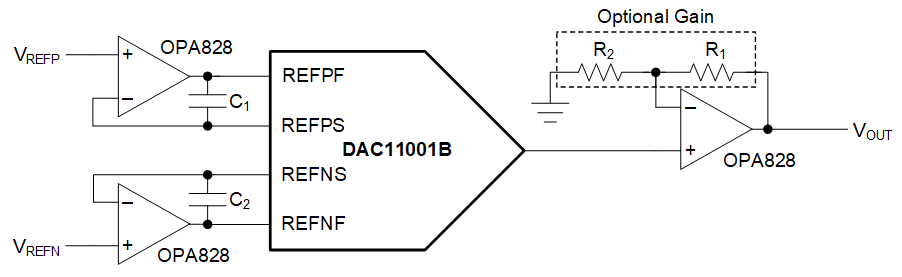

功能方框图 任意波形发生电路

任意波形发生电路