ZHCT389 February 2023 DLP6500FLQ , DLP650LNIR , DLP7000 , DLP7000UV , DLP9000X , DLP9000XUV , DLP9500 , DLP9500UV , DLPC410 , DLPC910

3.4 SPI 闪存布局连接

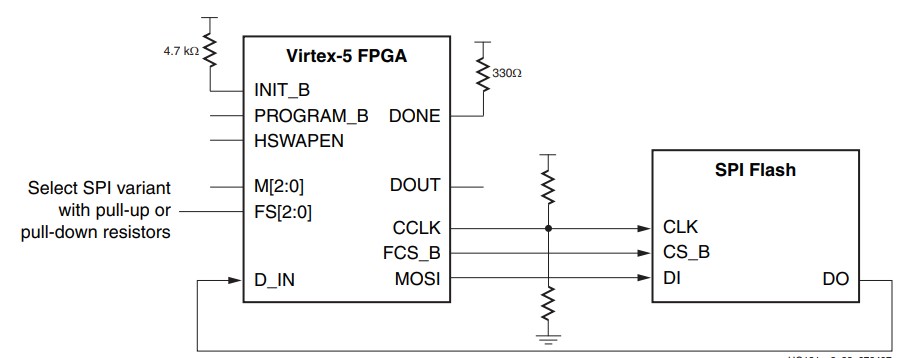

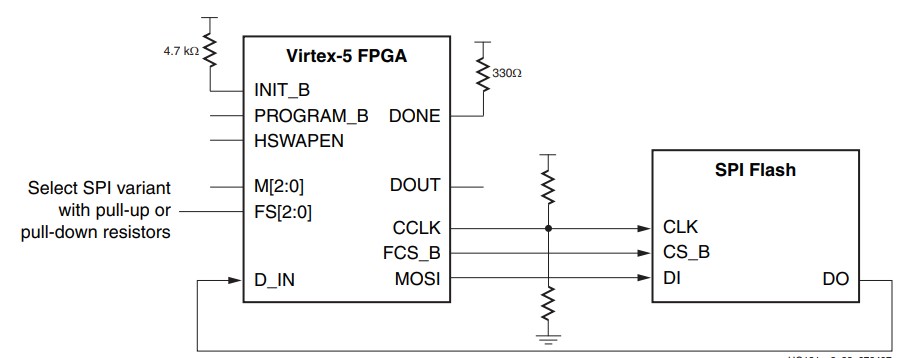

DLPC910 和 DLPC410 控制器必须使用下图所述的连接方式连接至 SPI 闪存

.

SPI 闪存写保护 (WP#) 应该被拉高以允许通过 Virtex 5 JTAG 接口进行编程。应将 SPI 闪存复位 (RESET#) 或保持 (HOLD#) 拉至高电平,以防止 SPI 闪存暂停与 DLPC410 和 DLPC910 控制器的串行通信。

有关 SPI 配置闪存如何连接到 DLPC410 控制器和 DLPC910 控制器的更多详细信息,请参阅 DLPLCRC910EVM 和 DLPLCRC410EVM 的原理图。

- FCS_B = DLPC910 控制器和 DLPC410 控制器的引脚 AA10

- MOSI = DLPC910 控制器和 DLPC410 控制器的引脚 AA9

- CCLK = DLPC910 控制器和 DLPC410 控制器的引脚 J10

- D_IN = DLPC910 控制器和 DLPC410 控制器的引脚 K11