ZHCT404A may 2020 – may 2020 LM61460-Q1

5 估算转换器的结温

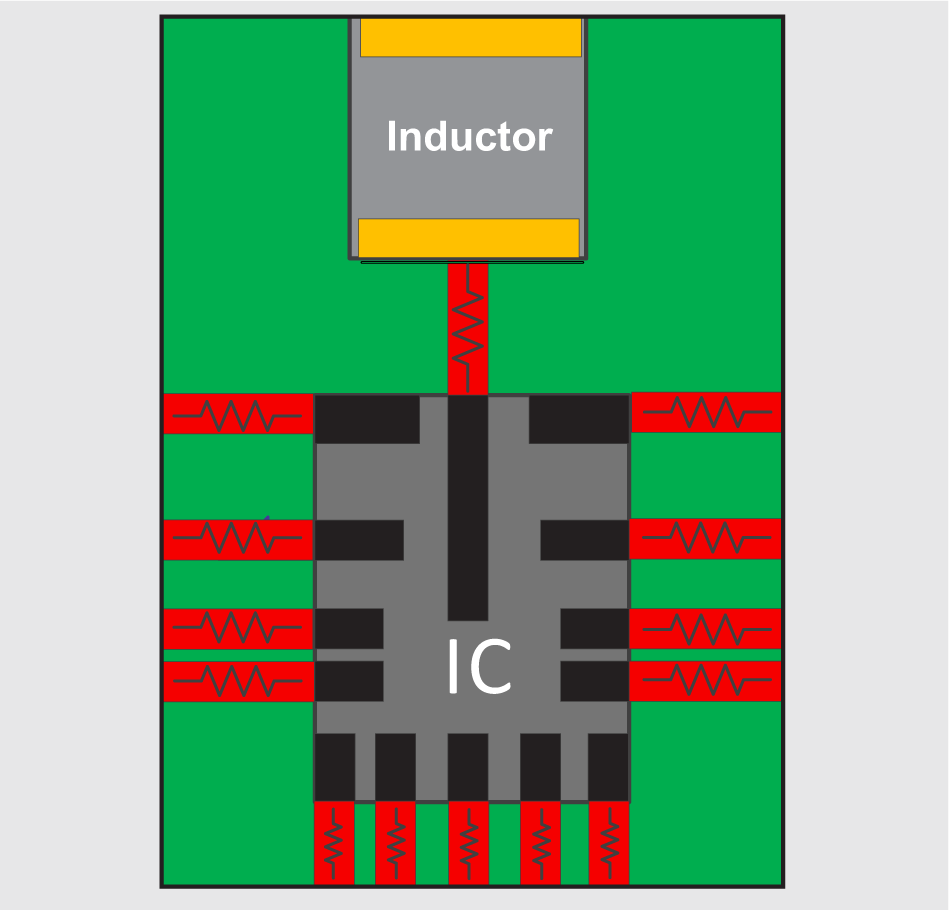

转换器的数据表中提供了电子器件工程联合委员会 (JEDEC) 标准板的仿真 RθJA。JEDEC 板通常具有非常小的引线,这对于导热性而言并不理想(图 6)。着陆垫到引线或铜平面连接可实现热传导。实际上,会连接到中间层的较大铜区域,从而使仿真 RθJA 显得过于保守。

要通过实验估算电路板的 RθJA,请注意给定功率条件下 IC 外壳温度的上升情况 (∆T)。一种更好的功率条件是降压转换器的输出电感器具有低损耗,但存在足以通过热像仪建立梯度以进行测量的功率损耗。即使安装正确,热电偶由于其散热倾向,通常也会对外壳顶部进行不准确的温度测量。根据测得的效率 η(在相同的环境温度下),公式 1 可以计算转换器和电路板 RθJA 中的功率损耗 (∆P),如下所示:

图 6 用于表征器件的 RθJA 的高热阻 JEDEC 板

图 6 用于表征器件的 RθJA 的高热阻 JEDEC 板虽然效率计算确实包括电感器损耗(这不会导致 IC 温度直接上升),但电感器和 IC 之间确实会发生热共享。转换器不是唯一的热源。对于具有较低损耗或较低偏置电流的电感器,RθJA 近似值变得更加准确。要进一步改进该估算,可能需要对功率级的体二极管进行正向偏置,以加热 IC,从而消除电感器的影响。然后,二极管的压降和偏置电流将用于功率损耗 (∆P)。

在计算中必须考虑转换器的 FET 温度系数。FET 的漏源导通电阻 [RDS(on)] 在设计的最高环境温度 (TA_max) 下将是最差的。FET RDS(on) 增大会导致效率在高环境温度下降低 (ηH)。公式 2 表示设计的最大额定环境温度下的转换器功率损耗 ∆PH:

∆PH =(1− ηH) × PIN (2)

公式 3 用于估算最高环境温度 TA_max 下的最坏情况结温

TJ = TA_max + RθJA × ∆PH (3)