ZHCT486 February 2024 UCC28C50

反激式转换器可在连续导通模式 (CCM) 或不连续导通模式 (DCM) 下运行。不过,对于许多低功耗、低电流应用而言,DCM 反激式转换器是一种结构更紧凑、成本更低的选择。以下是指导您完成此类设计的分步方法。

DCM 运行的特点是,在下一个开关周期开始之前,转换器的整流器电流会降至零。在开关之前将电流降至零,可以降低场效应晶体管 (FET) 功耗和整流器损耗,通常也会降低变压器尺寸要求。

相比之下,CCM 运行会在开关周期结束时保持整流器电流导通。我们在电源设计小贴士 76:反激式转换器设计注意事项和电源设计小贴士 77:设计 CCM 反激式转换器中介绍了反激式设计的利弊和 CCM 反激式转换器的功率级公式。CCM 运行非常适合中高功率应用,但如果您有一个可以使用 DCM 反激式转换器的低功率应用,请继续阅读。

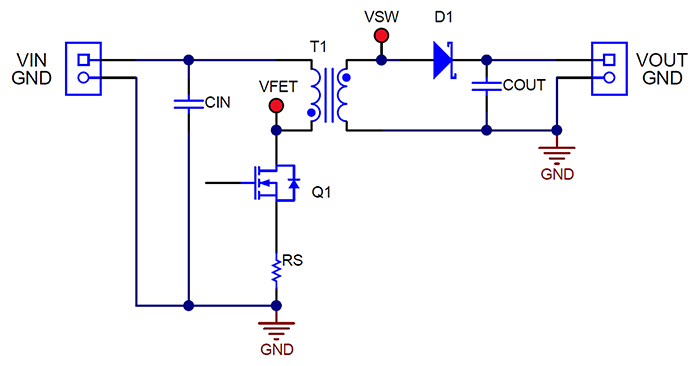

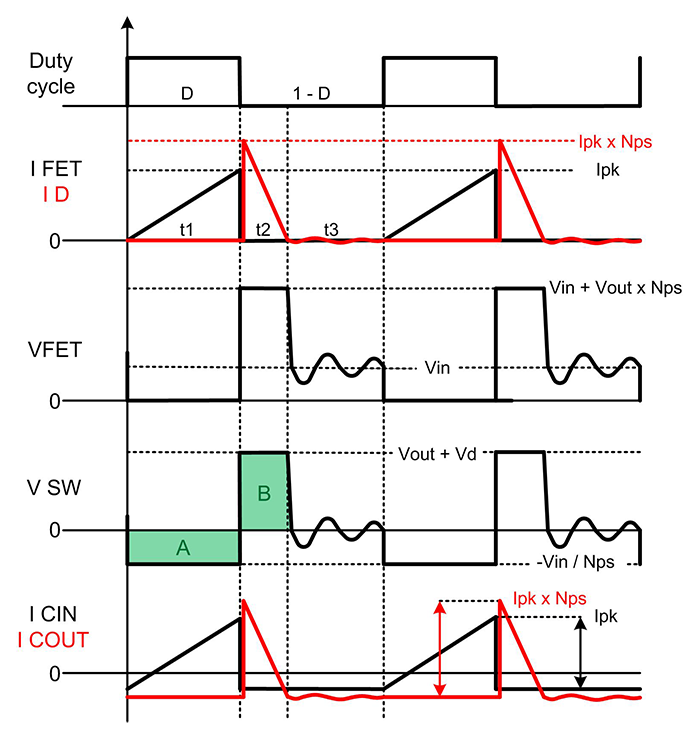

图 1 展示了反激式转换器的简化原理图,该转换器可在 DCM 或 CCM 模式下运行。此外,电路还能根据时序在不同模式之间切换。要保持在 DCM 模式下运行(这也是本文要评估的内容),关键元件的开关波形应具有图 2 所示的特性。

当 FET Q1 在占空比周期 D 内导通时,运行开始。T1 初级绕组中的电流始终从零开始,然后达到根据初级绕组电感、输入电压和导通时间 t1 设定的峰值。在此 FET 导通期间,二极管 D1 由于 T1 次级绕组极性而反向偏置,迫使在 t1 和 t3 期间由输出电容器 COUT 提供所有输出电流。

图 1 这款简化的反激式转换器可在 DCM 和 CCM 下运行。

图 1 这款简化的反激式转换器可在 DCM 和 CCM 下运行。当 Q1 在周期 1-D 内关断时,T1 的次级电压极性会反转,从而允许 D1 向负载传导电流并为 COUT 充电。在 t2 时间内,D1 中的电流从峰值线性下降至零。一旦 T1 的储存能量耗尽,在 t3 期间的剩余时间内只会出现残余振铃。产生这种振铃的主要原因是 T1 的磁化电感以及 Q1、D1 和 T1 的寄生电容。这在 t3 期间的 Q1 漏极电压(该漏极电压从 VIN 加上反射输出电压下降回 VIN)中很容易看出,因为一旦电流停止,T1 就无法支持电压。(注意:如果 t3 没有足够的死区时间,则可能会在 CCM 下运行。)CIN 和 COUT 中的电流与 Q1 和 D1 中的电流相同,但没有直流失调电压。

图 2 中的阴影区域 A 和 B 突出显示了变压器在 t1 和 t2 期间的伏微秒积,它们必须保持平衡才能防止饱和。区域“A”表示 (Vin/Nps) × t1,而“B”表示 (Vout + Vd) × t2,两者均以次级侧为基准。Np/Ns 是变压器初级/次级匝数比。

图 2 DCM 反激式转换器的关键电压和电流开关波形包括设计人员必须指定的几个关键参数。

图 2 DCM 反激式转换器的关键电压和电流开关波形包括设计人员必须指定的几个关键参数。表 1 详细说明了 DCM 相对于 CCM 的运行特性。DCM 的一个关键属性是,初级电感越低,占空比就越小,无论变压器的匝数比如何。此属性可用于限制设计的最大占空比。当您尝试使用特定的控制器,或保持在特定的导通或关断时间限制内时,这一点非常重要。较低的电感需要较低的平均储能(尽管峰值 FET 电流较高),这也往往使得变压器尺寸小于 CCM 设计所需的尺寸。

DCM 的另一个优点是,这种设计消除了标准整流器中的 D1 反向恢复损耗,因为电流在 t2 结束时为零。反向恢复损耗通常表现为 Q1 中的耗散增加,因此消除反向恢复损耗可降低开关晶体管上的应力。此方法的优势在输出电压较高的情况下变得越来越重要,因为整流器的反向恢复时间会随着额定电压较高的二极管的增加而延长。

| DCM 优势 | DCM 劣势 |

|---|---|

| 初级电感比 CCM 更低 | 峰值初级电流更高 |

| 电感设定最大占空比 | 峰值整流器电流更高 |

| 可以使用更小的变压器 | 输入电容更大 |

| 整流器反向恢复损耗为零 | 输出电容更大 |

| FET 导通损耗为零(或极小) | 可能会增加电磁干扰 |

| 控制环路中没有右半平面零点 | 占空比运行范围比 CCM 更宽 |

| 非常适合低输出功率 | 带宽变化增大 |

开发人员在开始设计时需要了解几个关键参数以及基本电气规格。首先选择开关频率 (fSW)、所需的最大工作占空比 (Dmax) 和估算的目标效率。然后,方程式 1 按如下方式计算导通时间 t1:

接下来,使用方程式 2 估算变压器的峰值初级电流 Ipk。对于方程式 2 中的 FET 导通电压 (Vds_on) 和电流检测电阻电压 (VRS),假设一些适合您设计的小压降(如 0.5V)。您可以稍后更新这些压降。

方程式 3会根据图 2 中的均衡区域 A 和 B 计算所需的变压器匝数比 Np/Ns:

其中 x 是 t3 所需的最短空闲时间(从 x = 0.2 开始)。

如果您想更改 Np/Ns,请调整 Dmax 并再次迭代。

接下来,使用方程式 4 和方程式 5 计算 Q1 (Vds_max) 和 D1 (VPIV_max) 的最大“平顶”电压:

由于这些元件通常会因变压器漏电感而产生振铃,因此根据经验,实际值应比方程式 4 和方程式 5 预测值高出 10% 至 30%。如果 Vds_max 高于预期,则减小 Dmax 会降低 Vds_max,但 VPIV_max 会增加。确定哪个元件电压更为关键,并在必要时再次迭代。

使用方程式 6 计算 t1_max,该值应接近于方程式 1 中的值:

使用方程式 7 计算所需的最大初级侧电感:

如果所选电感比方程式 7 中所示的更低,则根据需要进行迭代,以增大 x 并减小 Dmax,直到 Np/Ns 和 Lpri_max 等于所需值为止。

现在可以计算方程式 7 中的 Dmax:

并且可以分别使用方程式 9 和方程式 10 计算最大 Ipk 及其最大均方根 (RMS) 值:

根据所选控制器的电流检测输入最小电流限制阈值 Vcs(方程式 11)计算允许的最大电流检测电阻值:

使用方程式 11 中计算出的 Ipkmax 值和 RS 来验证方程式 2 中假设的 FET Vds 和检测电阻 VRS 的压降是否接近;如果明显不同,则再次迭代。

使用方程式 12 和方程式 13 计算 RS 的最大耗散功率,并根据方程式 10 计算 Q1 的导通损耗:

FET 开关损耗通常在 Vinmax 时最高,因此最好使用方程式 14 计算整个 VIN 范围内的 Q1开关损耗:

其中 Qdrv 是 FET 总栅极电荷,Idrv 是预期的峰值栅极驱动电流。

方程式 15 和方程式 16 计算 FET 非线性 Coss 电容充电和放电产生的总功率损耗。方程式 15 中的被积函数应与实际 FET 的 Coss 数据表中 0V 至实际工作电压 Vds 之间的曲线密切吻合。在高压应用中或使用超低 RDS(on) FET(具有较大 Coss 值)时,Coss 损耗通常非常大。

可通过对方程式 13、方程式 14 和方程式 16 的结果求和来近似计算总 FET 损耗。

方程式 17 表明该设计中的二极管损耗将大大降低。务必选择一个额定次级峰值电流的二极管,该电流通常远大于 IOUT。

输出电容通常选择为方程式 18 或方程式 19 中的较大者,根据纹波电压和等效串联电阻(方程式 18)或负载瞬态响应(方程式 19)计算电容:

其中 ∆IOUT 是输出负载电流的变化,∆VOUT 是允许的输出电压偏移,fBW 是估算的转换器带宽。

方程式 20 计算输出电容器均方根电流为:

方程式 23、方程式 24 和方程式 25 总结了三个关键波形时间间隔及其关系:

如果需要额外的次级绕组,方程式 26 可轻松计算额外的绕组 Ns2:

其中 VOUT1 和 Ns1 是稳压输出电压。

变压器初级均方根电流与方程式 10 中的 FET 均方根电流相同;变压器次级均方根电流如方程式 27 所示。变压器磁芯必须能够处理 Ipk 而不会饱和。您还应考虑磁芯损耗,但这超出了本文的讨论范围。

从提供的步骤中可以看出,DCM 反激式设计是一个迭代过程。最初的一些假设(如开关频率、电感或匝数比)可能会根据后来的计算(如功率耗散)而改变。但要不断尝试,尽可能频繁地执行设计步骤,以实现所需的设计参数。如果您愿意付出努力,优化的 DCM 反激式设计可以提供低功耗、紧凑型和低成本的解决方案,以满足电源转换器的需求。