ZHCT850 September 2024 ADC32RF55 , DAC39RF12

2 什么是跳频?

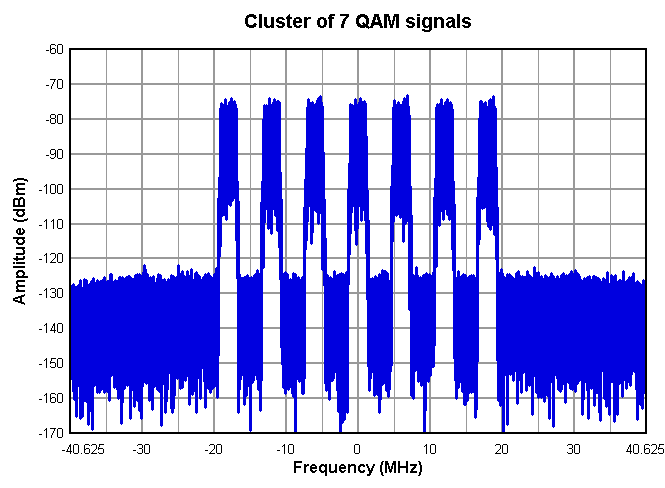

在现代通信系统(如 Wi-Fi® 6 和 7 或正交振幅调制 (QAM) 编码信号)中,频谱本质上是多频带,也就是说射频 (RF) 域在每个频带内包含多个通道。例如,Wi-Fi 6 和 7 在同一频段内的多个通道上运行,以便更大程度地动态提高带宽和数据吞吐量,而 QAM 则涉及将数据编码为单个通道内的不同相位偏移和振幅级别。图 1 显示了包含 7 个 QAM 通道的示例频带。

图 1 频域中的多音调信号。

图 1 频域中的多音调信号。直接射频采样模数转换器 (ADC) 和数模转换器 (DAC) 结合了许多数字特性。实现直接射频采样的最重要特性之一是 ADC 中的数字下变频器 (DDC) 和 DAC 中的数字上变频器 (DUC)。

在 ADC 中,DDC 由三个主要元件组成:NCO、数字混频器和抽取器块。NCO 在传统接收器信号链中用作本地振荡器的数字版器件,与输入信号混合,在基带(奈奎斯特区 1)中提供信号以及不需要的图像。抽取器块通过有限脉冲响应 (FIR) 抽取滤波器滤除图像,然后通过下采样降低信号带宽。抽取器块与中频 (IF) 滤波器具有等效的数字效果。

在 DAC 中,DUC 包含一个内插器、一个 NCO 和一个数字混频器。与 ADC 中不同,内插器对低带宽输入信号进行向上采样,然后通过 FIR 滤波器传递以抑制图像。在内插器级之后,输出信号馈送到数字混频器,与 NCO 混合,从而使 DAC 能够在具有较低输入信号带宽的宽奈奎斯特区上运行。

在射频采样转换器的给定输入上激活的 DDC 数量,决定了转换器是在单频带输出下运行还是多频带输出下运行。本文将重点介绍跳频的 ADC 内容。

图 2 展示了米6体育平台手机版_好二三四 (TI) ADC32RF55 的 DDC 示例。该器件是一款射频采样 ADC,能够以 3GSPS 的速率进行双通道、四频带运行。

图 2 ADC32RF55 的功能方框图(每个通道四个 DDC)。

图 2 ADC32RF55 的功能方框图(每个通道四个 DDC)。通常,所需的频带可能会发生变化:同一个射频采样转换器只需调整 NCO 频率即可匹配新的频段,而无需为每个频段切换完全不同的信号链。这是现代射频采样转换器的一项主要优势。将 NCO 从一个频率更改为另一个频率的行为称为跳频。

NCO 不直接生成模拟频率,而是以高分辨率生成所需频率的数字表示。每个 NCO 接收一个数字字(通常为 48 位或更高)。与 NCO 相位累加器组合使用时,该数字字可以表示适合数字混合级的信号。在对 NCO 编程时,对应于所需 IF 的数字表示形式是编程的内容,而不是实际频率。NCO 频率范围通常在 –Fs/2 和 Fs/2 之间,其中 Fs 表示转换器的采样频率。负频率字用于偶数奈奎斯特区的信号,而正频率字用于奇数奈奎斯特区的信号。

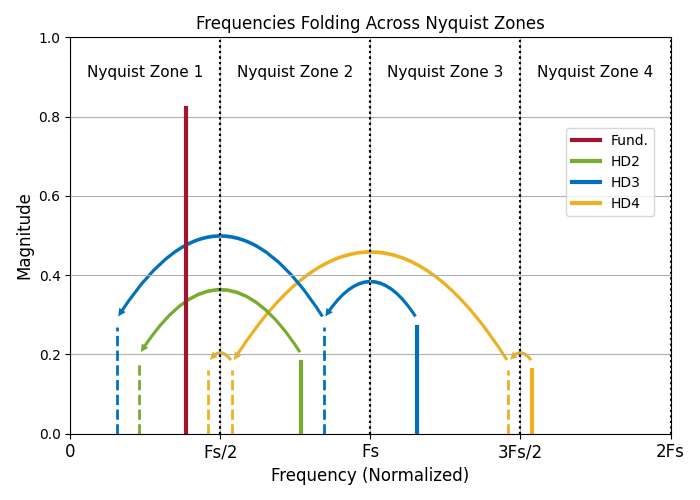

要确定高阶 NCO 频率在基带中的位置,首要任务是在目标频率与采样率之间执行模数运算,以消除 Fs 的任意倍数。现在,目标 NCO 频率介于 0Hz 和转换器采样率 Fs 之间。

如果 NCO 频率小于奈奎斯特频率 (Fs/2),则目标 NCO 频率将转换为奇数奈奎斯特区,如方程式 1所示:

如果计算出的 NCO 频率高于奈奎斯特频率,则该频率将位于偶数奈奎斯特区,如方程式 2 所示:

图 3显示了基频信号 (Fund) 及其二阶、三阶和四阶谐波(HD2、HD3 和 HD4)如何折回第一奈奎斯特区,尽管实际频率分量位于更高阶的奈奎斯特区。

图 3 谐波穿过高阶奈奎斯特区折叠到奈奎斯特区 1。

图 3 谐波穿过高阶奈奎斯特区折叠到奈奎斯特区 1。与传统 ADC 相比,射频采样 ADC 的一个优势是无需更改硬件即可切换频段。这种固有的灵活性使射频采样 ADC 能够快速适应新的频带,而无需增加硬件元件,从而简化了系统设计,并降低了成本。然而,这一发展不是一蹴而就的。在射频采样 ADC 的早期设计中,每个 NCO 和后续 DDC 只提供了一个 NCO 字选项。因此,跳转到另一个频率需要多次寄存器写入操作。

新 NCO 字必须通过串行外设接口 (SPI) 写入,然后再写入另一个寄存器,以便将新 NCO 字推入 DDC 块,使其实际生效。跳频所需的时间受多个因素影响,包括 NCO 字的长度和 SPI 事务速度。ADC 的寄存器大小通常限制为 8 位,因此总共需要七次寄存器写入才能更新 48 位 NCO:六次寄存器写入用于 NCO 字本身,另一次寄存器写入用于更新 DDC。

考虑到每个 SPI 事务的开销(通常是每个寄存器写入 16 位地址),事务时间将变为三倍。假设 SPI 数据流的不间断,当串行时钟信号 (SCLK) 速率为 20MHz 时,方程式 3 计算的跳频时间如下: