ZHCU734A January 2017 – March 2020

3.2.3.4.1 Overview

The software for this lab is mostly identical to lab three, but additional phase shedding and synchronous rectification threshold logic has been added in this lab. There are no variables that need to be adjusted in the Expressions Window. The DC load is used to step through loads from 1A-15A, recording input voltage and current, as well as output voltage and current at each step. From these observations the efficiency can be computed.

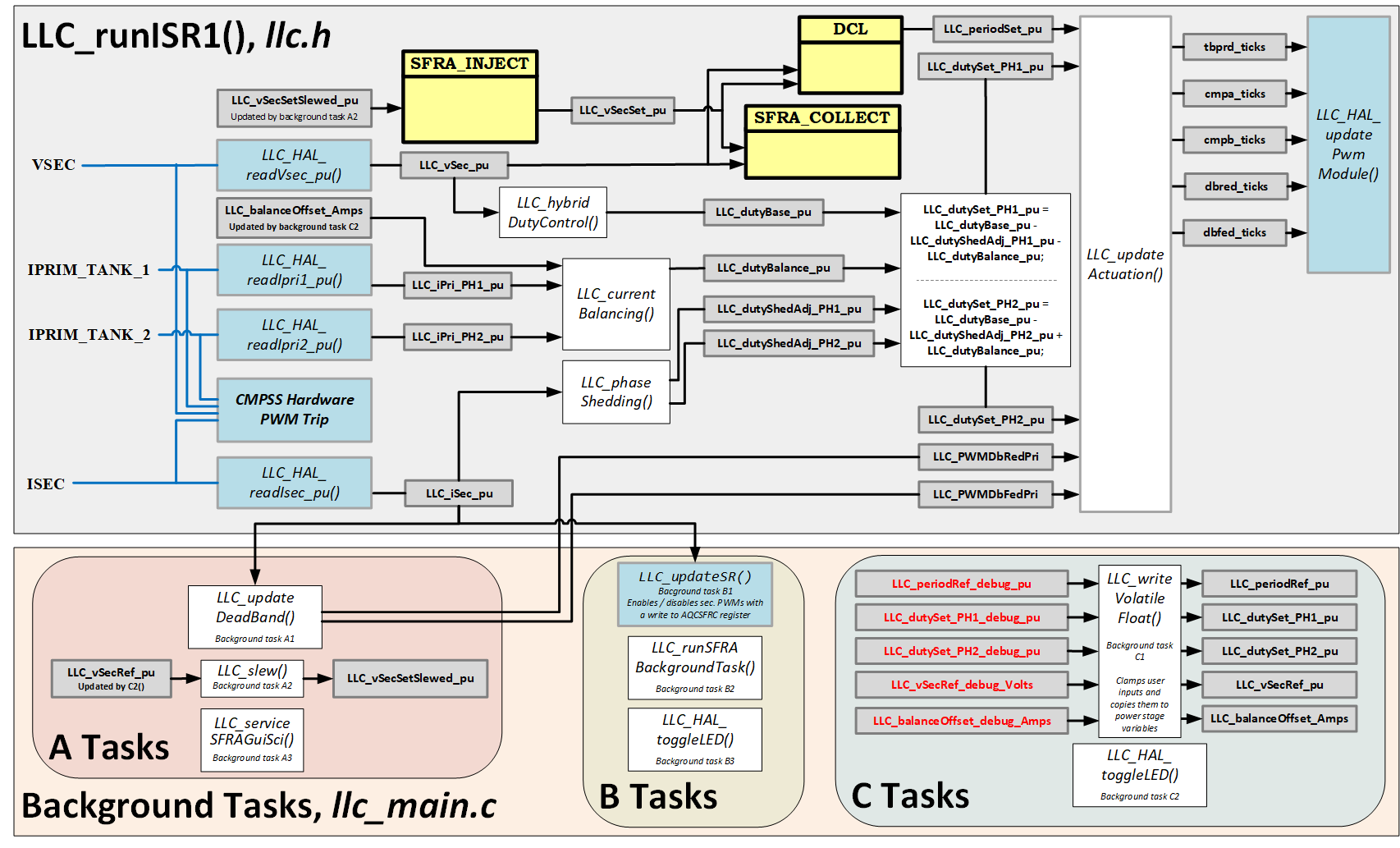

The software block diagram is shown in Figure 34