ZHCU760 March 2023

2.3.2.4 相位噪声优化

模拟信号链性能取决于时钟的相位噪声和抖动性能,这会影响数据转换器的 SNR、ENOB 和 SFDR。因此,应优化时钟的相位噪声以实现最低抖动。

可使用 PLLatinum™ 仿真工具对 LMX2615-SP 优化型环路滤波器进行编程,尽可能地降低相位噪声。在此设计中,环路滤波器与 LMX2615-SP EVM 元件保持相同。

表 2-2 LMX2615-SP 设计参数

| 参数 | 值 |

|---|---|

| VCO 增益 | 132 MHz/V |

环路带宽 | 285 kHz |

相位裕度 | 65 度 |

C1_LF | 390nF |

C2_LF | 68nF |

C3_LF | 进行中 |

C4_LF | 1.8nF |

R2 | 68Ω |

R3_LF | 0Ω |

R4_LF | 18Ω |

电荷泵增益 | 15mA |

相位检测器频率 | 200MHz |

VCO 频率 | 为 15GHz 精心设计,但适用于整个频率范围 |

ADC SNR 性能会因外部时钟抖动和内部 ADC 孔径抖动而降低。ADC 的 SNR 受总抖动限制,计算公式如下:

方程式 1.

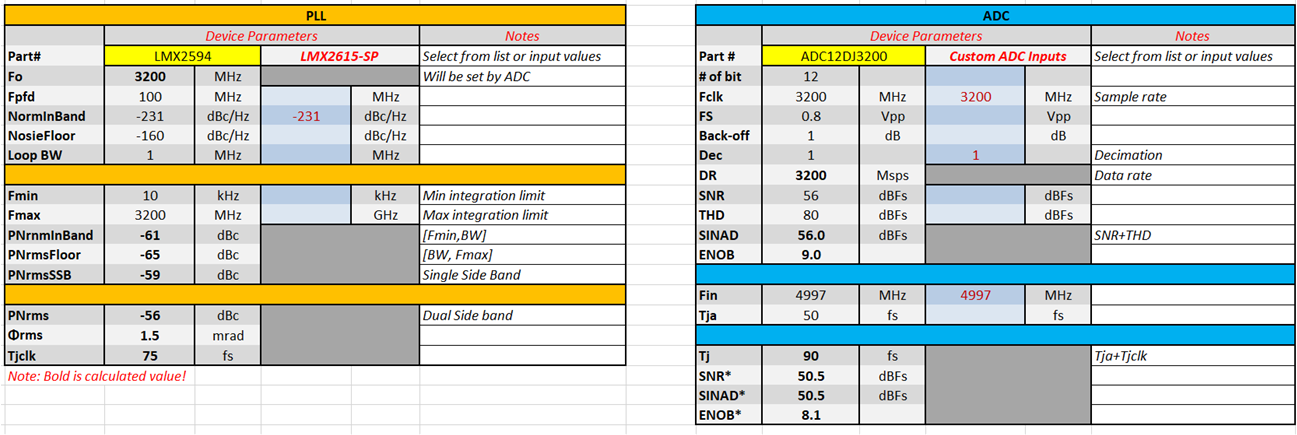

为了计算 ADC12DJ3200-SP 在时钟性能方面的 SNR 性能,TI 提供了一款工具,其中包含 ADC 的抖动和 SNR 计算器 (JITTER-SNR-CALC)。图 2-7 是包含计算结果的屏幕截图:

图 2-7 抖动至 SNR 工具屏幕截图

图 2-7 抖动至 SNR 工具屏幕截图

图 2-8 SNR 与 TJ 间的关系

图 2-9 SNR 与 FIN 间的关系