ZHCU772 December 2021

- 说明

- 资源

- 特性

- 应用

- 5

- 1System Overview

- 2Hardware, Software, Testing Requirements, and Test Results

- 3Design and Documentation Support

- 4About the Author

- 5Acknowledgement

1.4.3 Power-Supply Selection

In this design, RF PLL LMX2820 is used as a frequency synthesizer for clocking the data converter. The LMX2820 requires lower clock jitter and therefore lower phase noise to generate the required higher sampling clocks. Phase noise is directly impacted by the power supply noise and ripple.

This design has included both the 3.3-V supply options from high efficiency, low noise and low-ripple synchronous buck converter (TPS62913) and high-accuracy low noise LDO (TPS7A5301). The LMX2820 phase-noise performance measured with both supply options and results shows very equivalent results. Hence, the LMX2820 is powered up with the TPS62913 in this design and all AFE7950 performance results are with the TPS62913 on clocking board.

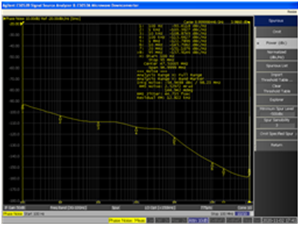

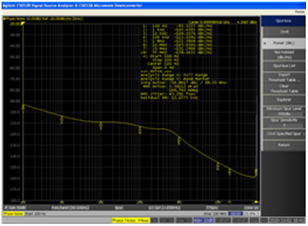

Figure 1-6 and Figure 1-7 show the phase noise and jitter performance of the LMX2820 at 9-GHz operating frequency with TPS62913 and TPS7A5301.

Figure 1-6 LMX2820 Phase Noise With

TPS7A5A01

Figure 1-6 LMX2820 Phase Noise With

TPS7A5A01 Figure 1-7 LMX2820 Phase Noise With

TPS62913

Figure 1-7 LMX2820 Phase Noise With

TPS62913