ZHCU772 December 2021

- 说明

- 资源

- 特性

- 应用

- 5

- 1System Overview

- 2Hardware, Software, Testing Requirements, and Test Results

- 3Design and Documentation Support

- 4About the Author

- 5Acknowledgement

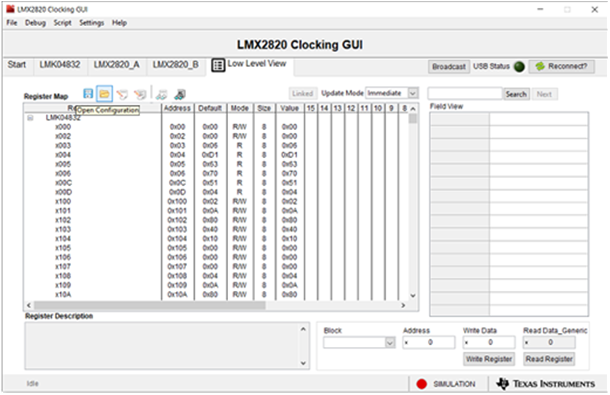

2.1.2.5 Clocking Board Programming Sequence

All devices in the clocking board are configured by loading the configuration files in the low-level view page.

- Load the LMK04832_2949.12M_184.32MREF_SYSREF_SYNC.cfg file to program onboard LMK04832 to generate FPGA REF clock and SYSREFs

- Load the LMX2820_A_B_8847.36M_184.32MREF_SYSREF_REPT_SYNC.cfg file to generate synchronized device clocks at 8847.36 MHz and SYSREF in repeater mode from LMX2820s

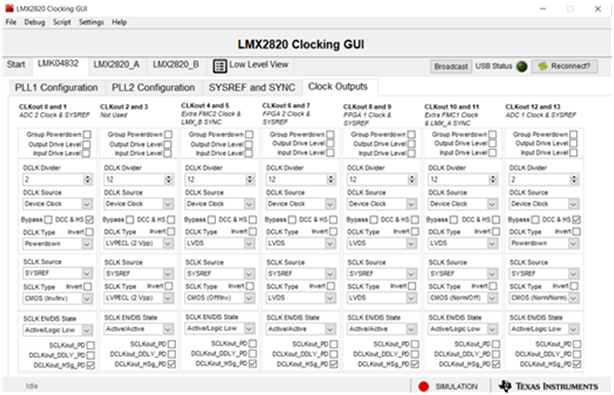

- Once all other boards are programmed, turn off the SYSREF to AFE7950EVM by setting Active/Logic Low for SDCLK1 and SDCLK13 from the clocking board

Figure 2-4 LMX2820 Clocking GUI

Figure 2-4 LMX2820 Clocking GUI Figure 2-5 LMX2820 Clocking GUI With

LMK04832 Tab

Figure 2-5 LMX2820 Clocking GUI With

LMK04832 Tab