ZHCU772 December 2021

- 说明

- 资源

- 特性

- 应用

- 5

- 1System Overview

- 2Hardware, Software, Testing Requirements, and Test Results

- 3Design and Documentation Support

- 4About the Author

- 5Acknowledgement

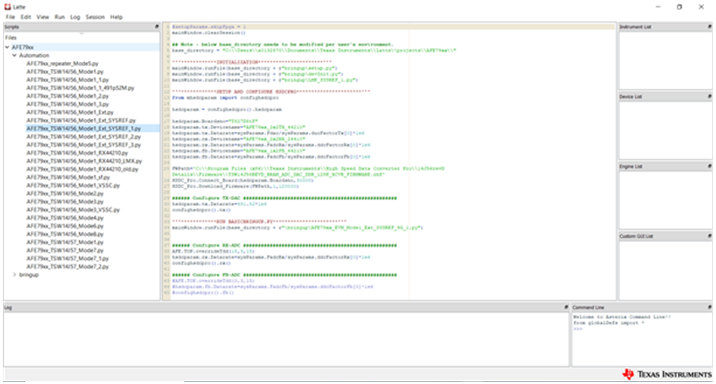

2.1.2.6 Latte SW and HSDC Pro Setup

Once the clocking board is programmed, open the Latte software and HSDC Pro software on the same test PC.

For a synchronization test, each AFE7950EVM and TSW14J56EVM pair must be connected to a separate PC running the Latte software and HSDC Pro software.

- Select the AFE79xx_TSW14J56_Mode1_Ext_SYSREF_1.py automation script and run (press F5) in Latte SW. The script will bypass the external SYSREF through the onboard LMK04828, configure AFE7950 device and configure the TSW14J56EVM. Also synchronize the both AFE7950 devices in different EVMs.

- After AFE EVM setup and HSDC Pro setup, run step 3 from Section 2.1.2.5

- For the synchronization test, use HSDC pro tools in trigger mode

Figure 2-6 AFE7950 GUI

Figure 2-6 AFE7950 GUI