ZHCU798 January 2022

4.1.3.5 PCB 层堆叠相关建议

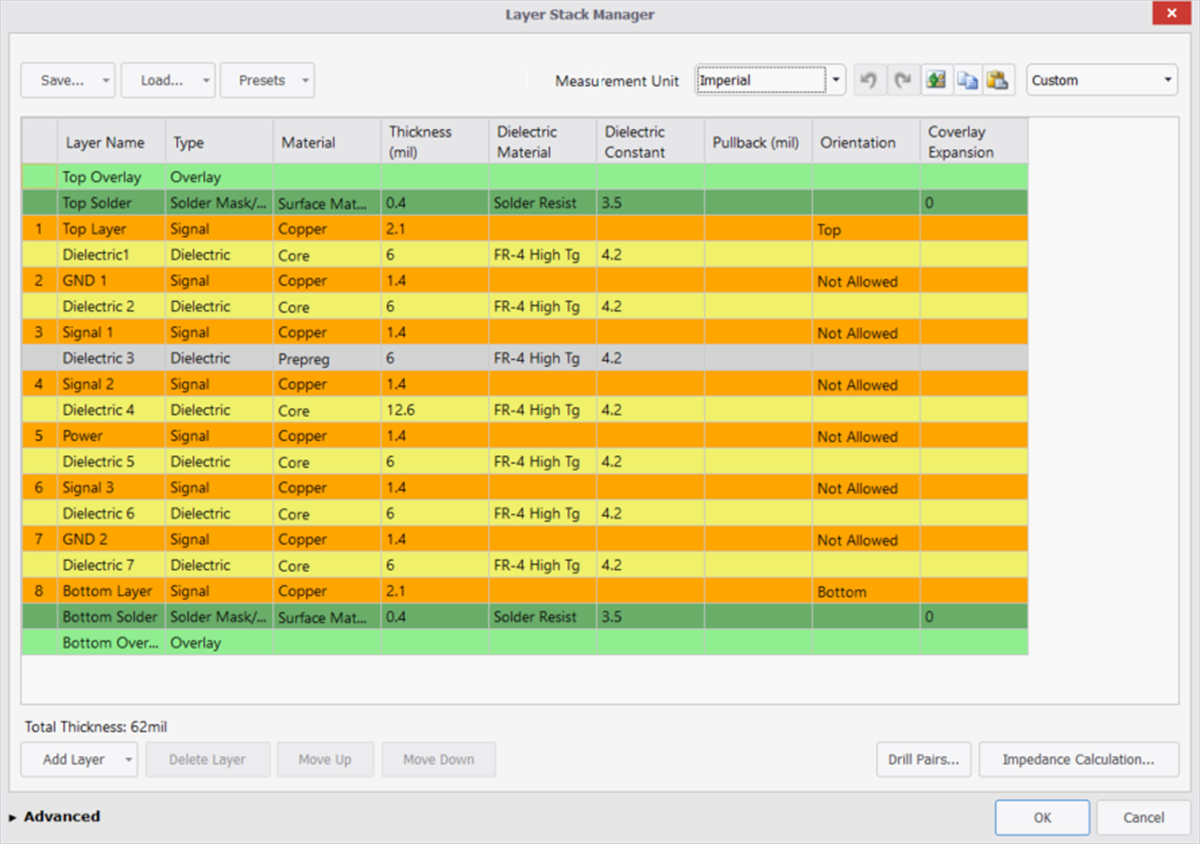

图 4-2 显示了用于 PMIC 和串行器板的 8 层堆叠。由于 PCB 的小尺寸要求引入的复杂布线要求,所以需要两个信号层,其中必须包含 PMIC、串行器和成像仪之间的 I2C、逻辑 IO、时钟和控制信号。选择分离外层是以确保特征阻抗为 50Ω ±10%

在此设计中,顶层和底层均放置高电流元件,因此堆叠中的第 2 层和第 7 层是专用接地层,以最大程度地缩短高电流返回路径。成像仪第 7 层同样包含单独的 AGND 层。

图 4-2 层堆叠

图 4-2 层堆叠