ZHCU807B March 2020 – July 2021

E 连接 Reference Pro

若要使用 Reference Pro,请更改 SE 或差分连接的配置,如 Topic Link LabelD 所示。

图 E-1 使用 Reference Pro 的 LMX2594EVM 设置

图 E-1 使用 Reference Pro 的 LMX2594EVM 设置LMK61PD0A2 具有多个专用于输出格式控制、输出频率控制和输出使能控制的控制引脚。这些控制引脚可通过 表 E-1 和 表 E-2 所示的跳线进行配置。

跳线 FS1、FS0、OS 和 OE 可用来配置相应的控制引脚,通过将中心引脚分别搭接在 VDD 位置(连接引脚 2 和 3)或在 GND 位置(连接引脚 1 和 2),使其处于高电平或低电平状态。从 VDD 位置到器件电源的连接或者从 GND 位置到接地层的连接由 1.5kΩ 电阻器实现。

表 E-1 LMK61PD0A2 的输出频率 (Reference Pro)

| FS1 | FS0 | 输出频率 (MHz) |

|---|---|---|

| 0 | 0 | 100 |

| 0 | NC | 312.5 |

| 0 | 1 | 125 |

| NC | 0 | 106.25 |

| NC | NC | 156.25 |

| NC | 1 | 212.5 |

| 1 | 0 | 62.5 |

表 E-2 LMK61PD0A2 的输出类型 (Reference Pro)

| 操作系统 | OE | 输出类型 |

|---|---|---|

| X | O | 禁用(PLL 功能) |

| 0 | 1 | LVPECL |

| NC | 1 | LVDS |

| 1 | 1 | HCSL |

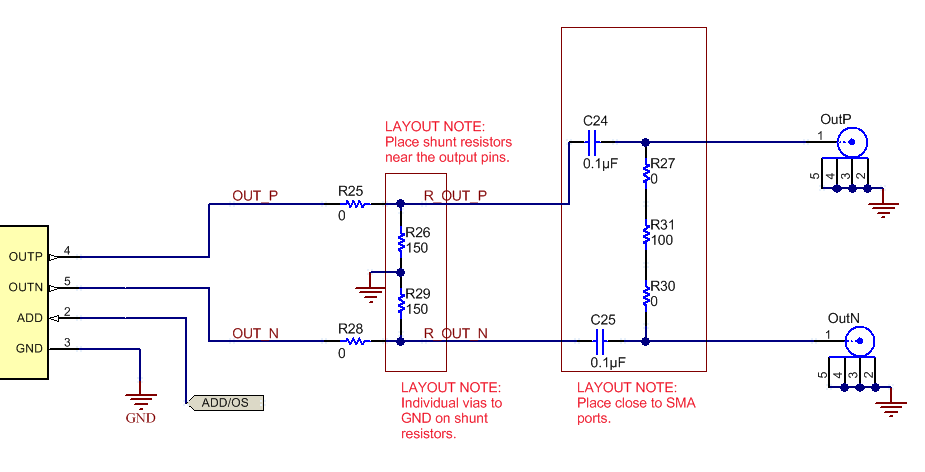

OS 引脚用于偏置内部驱动器并更改输出类型。必须将 表 E-3 所示的输出端接无源器件与 表 E-2 的输出类型进行匹配。

表 E-3 列出了每个配置的器件值。

表 E-3 输出端接方案

| 输出格式 | 耦合 | 组件 | 值 |

|---|---|---|---|

| LVPECL | AC (默认 EVM 配置) |

R25、R28 | 0Ω |

| R26、R29 | 150Ω | ||

| C24、C25 | 0.01µF | ||

| R27、R30、R31 | DNP | ||

| DC(1) | R25、R28、C24、C25 | 0Ω | |

| R26、R29、R27、R30、R31 | DNP | ||

| LVDS(2) | 交流 | R25、R28、R27、R30 | 0Ω |

| R31 | 100Ω | ||

| C24、C25 | 0.01µF | ||

| R26、R29 | DNP | ||

| DC | R25、R27、R28、R30、C24、C25 | 0Ω | |

| R31 | 100Ω | ||

| R26、R29 | DNP | ||

| HCSL | 交流 | R25、R28 | 0Ω |

| R26、R29 | 50Ω | ||

| C24、C25 | 0Ω | ||

| R27、R30、R31 | DNP | ||

| DC | R25、R28 | 0Ω | |

| R26、R29 | 50Ω | ||

| C24、C25 | 0.01µF | ||

| R27、R30、R31 | DNP |

(1) 50Ω 至 VCC – 接收器上需要 2V 端接。

(2) Reference Pro PCB 上具备 100Ω 差分端接 (R31)。如果接收器上的差分端接可用,则可以移除 EVM 上的差分端接。

图 E-2 LMK61PD0A2 输出端接

图 E-2 LMK61PD0A2 输出端接