ZHCU877B May 2021 – October 2023

- 1

- 摘要

- 商标

- 1关键特性

- 2EVM 版本和组件型号

- 3重要使用说明

- 4系统说明

- 5已知问题

- 6法规遵从性

- 7修订历史记录

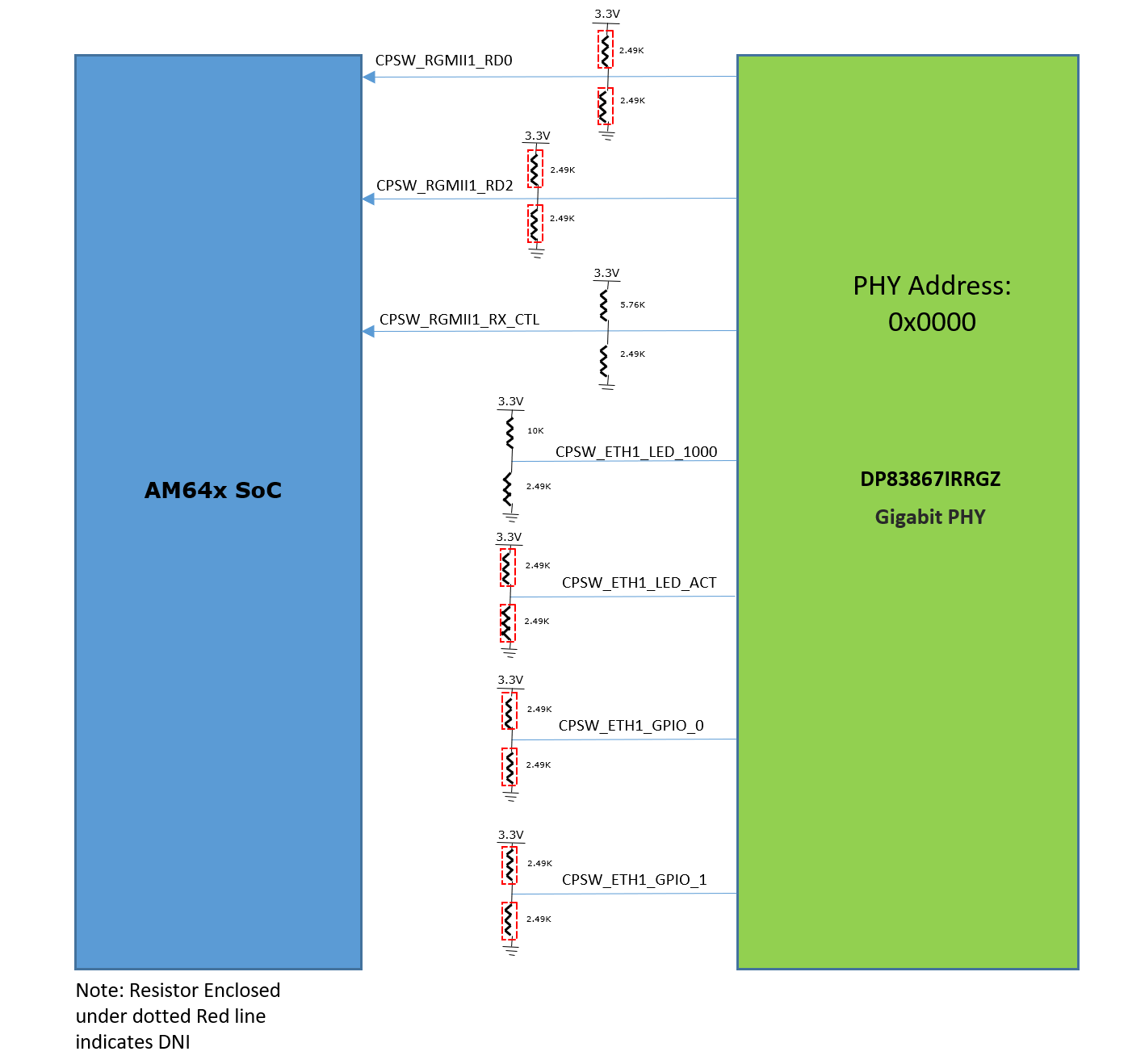

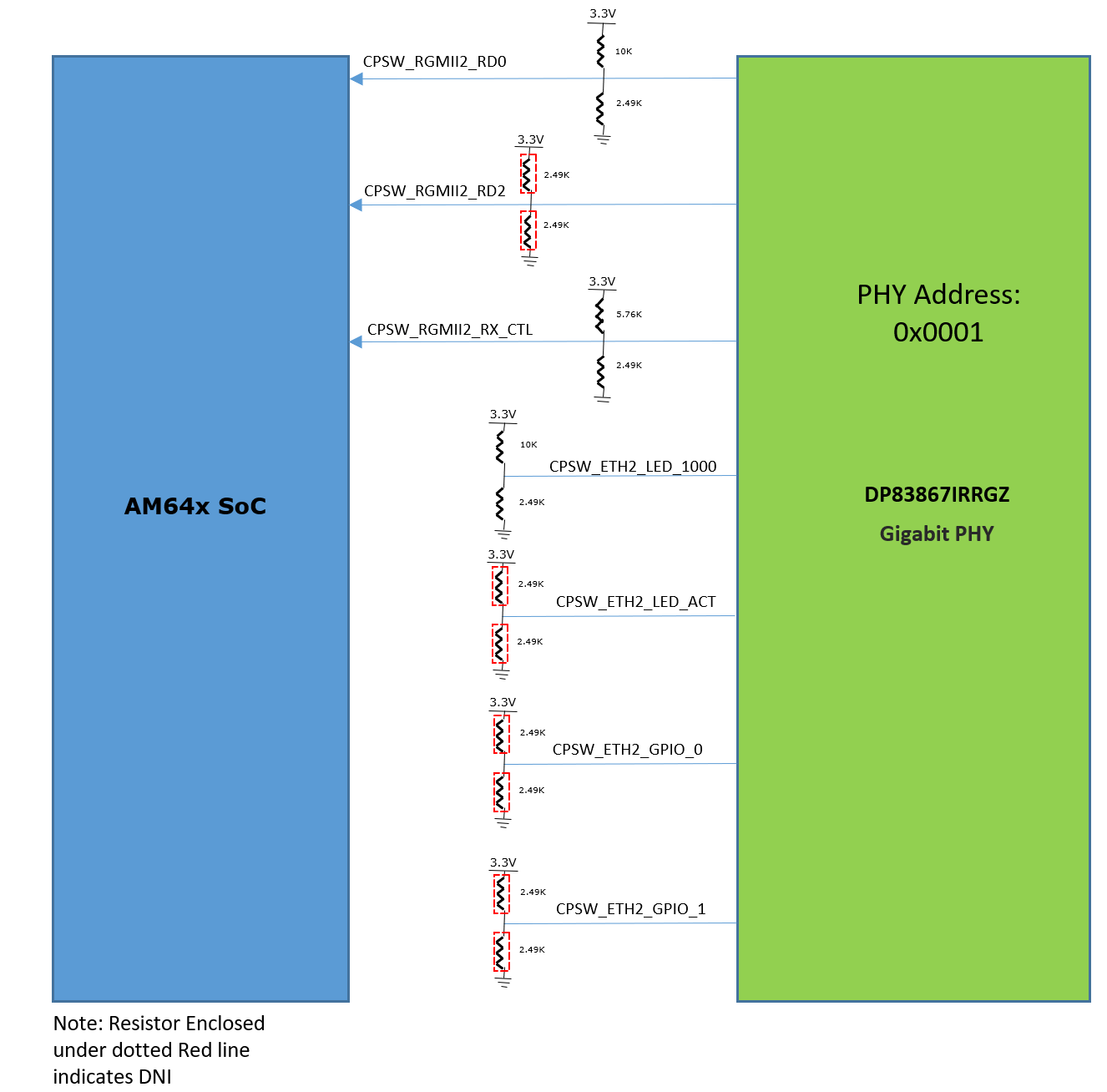

4.4.9.1 DP83867 PHY 默认配置

DP83867 PHY 使用四级电阻器 strap 配置,可生成四种不同的电压范围。电阻器连接到 RX 数据和控制引脚,它们通常由 PHY 驱动,是 AM64x 的输入。每种模式的电压范围如下所示。

模式 1 - 0V 至 0.3234V

模式 2 - 0.462V 到 0.6303V

模式 3 - 0.7425V 到 0.9372V

模式 4 - 2.2902V 到 2.904V

DP83867 器件包括内部下拉电阻器。选择外部拉电阻器的值,为 AM64x 的引脚提供尽可能接近接地或 3.3V 的电压。图 4-19 中显示了 Strap 配置。表 4-17 中提供了 strap 配置值

表 4-17 Strap 配置值

| 模式 | 目标电压 | 理想 Rhi (k Ω) |

理想 Rlo (k Ω) |

||

|---|---|---|---|---|---|

| Vmin(V) | Vtyp(V) | Vmax(V) | |||

| 1 | 0 | 0 | 0.098 * VDDIO | 断开 | 断开 |

| 2 | 0.140 * VDDIO | 0.165 * VDDIO | 0.191 * VDDIO | 10 | 2.49 |

| 3 | 0.225 * VDDIO | 0.255 * VDDIO | 0.284 * VDDIO | 5.76 | 2.49 |

| 4 | 0.694 * VDDIO | 0.763 * VDDIO | 0.886 * VDDIO | 2.49 | 断开 |

CPSW PHY-1 和 CPSW PHY-2 实现了地址 strap 配置,分别用于设置地址 -00000 (0h) 和 00001(01h)。默认情况下,由于 strap 配置引脚具有内部下拉电阻器,所有 strap 配置引脚均提供了上拉和下拉占用空间,除了 LED_0。LED_0 用于镜像启用,默认情况下设为模式 1,模式 4 不适用,模式 2、模式 3 选项不能满足要求。表 4-18 和表 4-19 中提供了 CPSW RGM I 1Ethernet PHY 和 CPSW RGMII1 以太网 PHY 的默认 strap 设置。

图 4-19 CPSW 以太网 PHY-1 Strap 设置

图 4-19 CPSW 以太网 PHY-1 Strap 设置 图 4-20 CPSW 以太网 PHY-2 Strap 设置

图 4-20 CPSW 以太网 PHY-2 Strap 设置表 4-18 CPSW RGMII-1 以太网 PHY 的默认 Strap 设置

| Strap 设置 | 引脚名称 | Strap 功能 | PRG1_PRU1、PRG1_PRU0 的模式 | PRG1 的 Strap 功能值 | 说明 |

|---|---|---|---|---|---|

| PHY 地址 | RX_D2 | PHY_AD3 | 1 | 0 | PHY 地址:0000 |

| PHY_AD2 | 1 | 0 | |||

|

RX_D0 |

PHY_AD1 | 1 | 0 | ||

| PHY_AD0 | 1 | 0 | |||

| 自动协商 | RX_DV/RX_CTRL | 自动协商 | 3 | 0 | 自动协商禁用 = 0 |

| 运行模式 | LED2 | RGMII 时钟偏差 TX[1] | 5 | 0 | RGMII TX 时钟偏差设为 0ns |

| RGMII 时钟偏差 TX[0] | 5 | 0 | |||

| LED_1 | RGMII 时钟偏差 TX[2] | 5 | 1 | ||

| ANEG_SEL | 1 | 0 | 通告能力 10/100/1000 | ||

| LED_0 | 镜像启用 | 1 | 0 | 镜像启用已禁用 | |

| GPIO_1 | RGMII 时钟偏差 RX[2] | 1 | 0 | RGMII RX 时钟偏差设为 2ns | |

| RGMII 时钟偏差 TX[1] | 1 | 0 | |||

| GPIO_0 | RGMII 时钟偏差 RX[0] | 1 | 0 |

表 4-19 CPSW RGMII-2 以太网 PHY 的默认 strap 设置

| Strap 设置 | 引脚名称 | Strap 功能 | PRG1_PRU1、PRG1_PRU0 的模式 | PRG0 和 PRG1 的 Strap 功能值 | 说明 |

|---|---|---|---|---|---|

| PHY 地址 | RX_D2 | PHY_AD3 | 1 | 0 | PHY 地址:0001 |

| PHY_AD2 | 1 | 0 | |||

|

RX_D0 |

PHY_AD1 | 2 | 0 | ||

| PHY_AD0 | 2 | 1 | |||

| 自动协商 | RX_DV/RX_CTRL | 自动协商 | 3 | 0 | 自动协商禁用 = 0 |

| 运行模式 | LED2 | RGMII 时钟偏差 TX[1] | 5 | 0 | RGMII TX 时钟偏差设为 0ns |

| RGMII 时钟偏差 TX[0] | 5 | 0 | |||

| LED_1 | RGMII 时钟偏差 TX[2] | 5 | 1 | ||

| ANEG_SEL | 1 | 0 | 通告能力 10/100/1000 | ||

| LED_0 | 镜像启用 | 1 | 0 | 镜像启用已禁用 | |

| GPIO_1 | RGMII 时钟偏差 RX[2] | 1 | 0 | RGMII RX 时钟偏差设为 2ns | |

| RGMII 时钟偏差 TX[1] | 1 | 0 | |||

| GPIO_0 | RGMII 时钟偏差 RX[0] | 1 | 0 |