ZHCU877B May 2021 – October 2023

- 1

- 摘要

- 商标

- 1关键特性

- 2EVM 版本和组件型号

- 3重要使用说明

- 4系统说明

- 5已知问题

- 6法规遵从性

- 7修订历史记录

4.4.5 JTAG

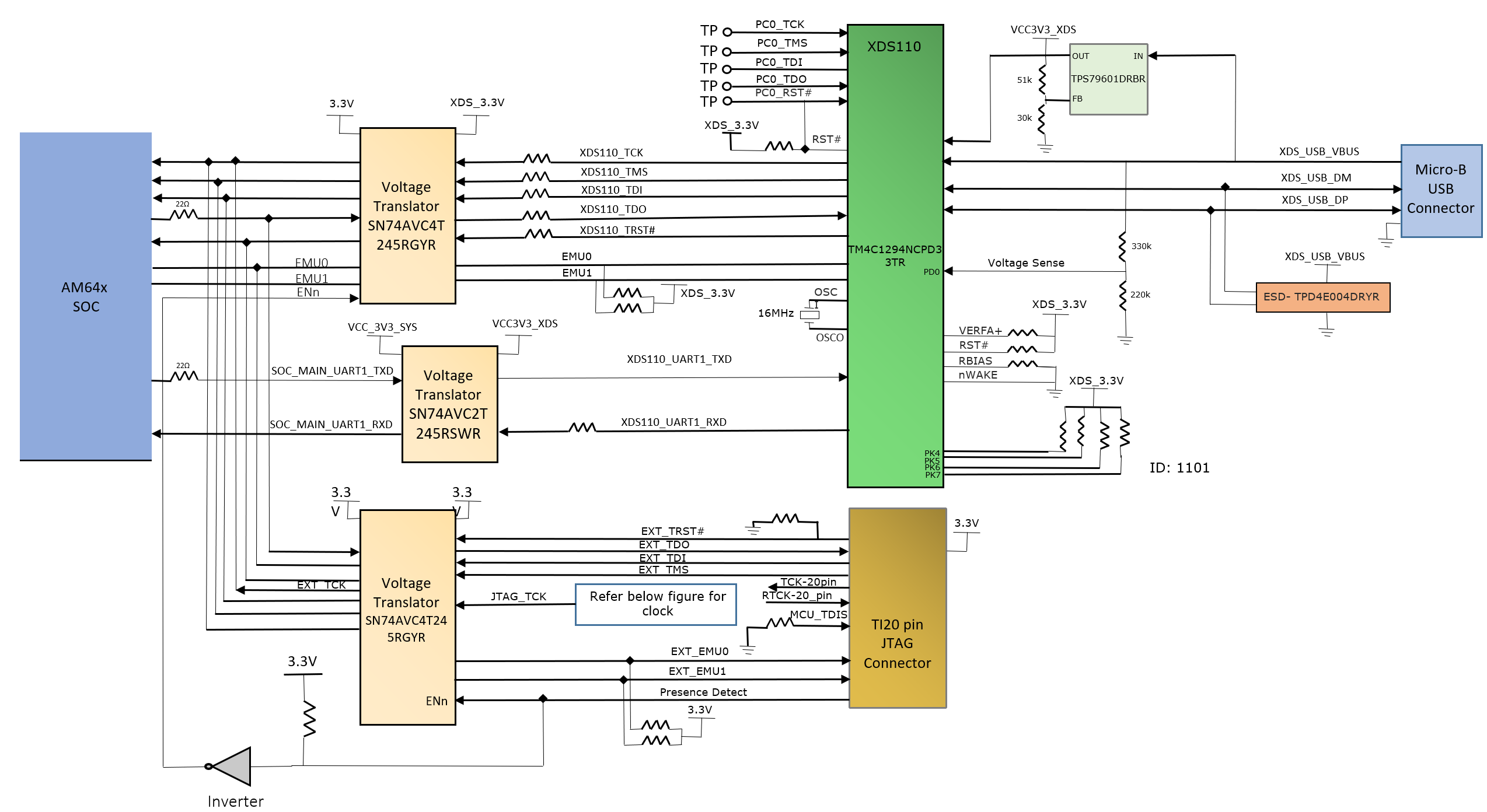

在 SKEVM 上,可以选择通过一个 20 引脚标准 JTAG cTI 接头 (J14) 提供一个 JTAG 接口。这样用户就可连接外部 JTAG 仿真器。使用电压转换缓冲器将 cTI 接头的 JTAG 信号与 EVM 的其余部分相隔离。XDS110 部分和 cTI 接头部分的电压转换器输出进行多路复用并连接到 SoC JTAG 接口。如果使用存在检测电路感知到了与 cTI 20 引脚 JTAG 连接器的连接,则多路复用将设为将 20 引脚信号路由到 AM64x,以代替板载仿真电路。

cTI 20 引脚 JTAG 连接器 J14 的引脚布局在表 4-13 中提供。为 USB 信号提供 ESD 保护(器件型号 TPD4E004),以便将 ESD 电流脉冲引向 VCC 或 GND。TPD4E004 可为高达 ±15kV 的人体放电模型 (HBM) ESD 脉冲(在 IEC 61000-4-2 中指定)提供保护,并提供 ±8kV 接触放电和 ±12kV 空气间隙放电。cTI 20 引脚连接器的引脚布局详情,请参阅表 4-13。

| 引脚编号 | 信号 | 引脚编号 | 信号 |

|---|---|---|---|

| 1 | JTAG_TMS | 11 | JTAG_cTI_TCK |

| 2 | JTAG_TRST# | 12 | DGND |

| 3 | JTAG_TDI | 13 | JTAG_EMU0 |

| 4 | JTAG_TDIS | 14 | JTAG_EMU1 |

| 5 | VCC_3V3_SYS | 15 | JTAG_EMU_RSTN |

| 6 | NC | 16 | DGND |

| 7 | JTAG_TDO | 17 | NC |

| 8 | SEL_XDS110_INV | 18 | NC |

| 9 | JTAG_cTI_RTCK | 19 | NC |

| 10 | DGND | 20 | DGND |

图 4-11 JTAG 接口

图 4-11 JTAG 接口SKEVM 板包括 XDS110 类板载仿真和一个测试自动化接头,以支持软件构建的 TI 内部测试。仿真器的连接使用 USB2.0 micro-B 连接器 (J12) 以及用作供电 USB 从器件的电路。来自连接器的 VBUS 电源用于为仿真电路供电,这样即使在断开 EVM 电源时,与仿真器的连接也不会断开。使用电压转换缓冲器将 XDS110 电路与 EVM 的其余部分相隔离。此外,XDS110 还可在同一 USB 端口为 USB 信号转换提供 UART。SoC MAIN 域(没有流控制)的 UART1 通过隔离器连接到 XDS110 UART 端口。