ZHCU923A October 2020 – February 2022

- 商标

- 1引言

- 2J7200 EVM 概述

- 3EVM 用户设置/配置

- 4J7200 EVM 硬件架构

- 5功能安全

- 6修订历史记录

4.10 QSGMII 以太网接口

J7200 SoC 的 SERDES0 SGMII1 信号通过 CP 板连接到四端口以太网板上的四路 SGMII PHY VSC8514XMK-11,两个具有集成磁性元件的堆叠 RJ45 连接器(器件型号为 LPJG17512AONL)用于外部通信。

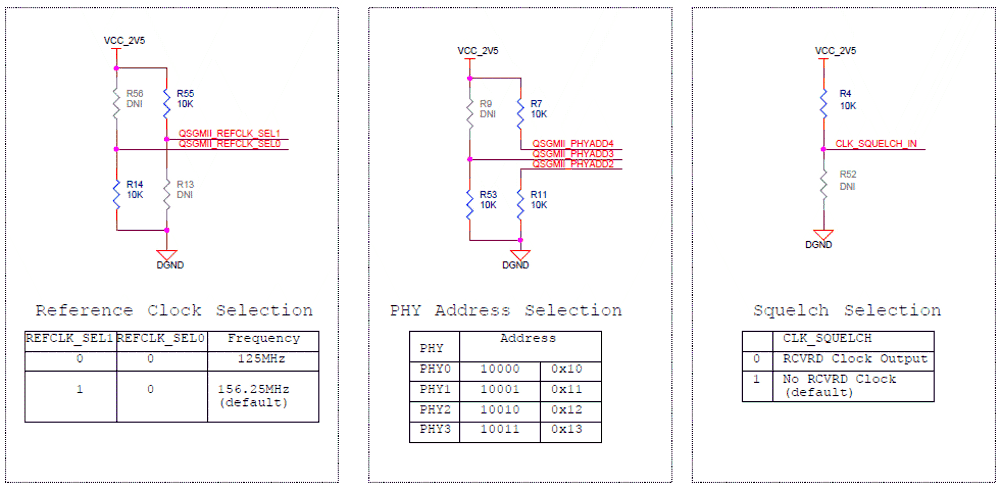

VC8514 器件包含三个外部 PHY 地址引脚 PHYADD [4:2],用于控制系统板上共享公共管理总线的多个 PHY 器件。这些引脚设置了 PHY 地址端口映射的最高有效位。每个端口地址的低两位来自端口的物理地址(0 到 3)和寄存器 20E1 第 9 位中 PHY 地址反转位的设置。

默认情况下,PHY 的参考时钟 156.25MHz 由 CP 板上的 SERDES 时钟发生器 (CDCI2) 生成。也可以选择使用四端口以太网板上的时钟发生器通过电阻器选项向 PHY 提供时钟。

| 时钟源 | 安装 | 拆除 |

|---|---|---|

| 来自 CP 板(默认) | R1,R2 | R3,R4 |

| 来自板载时钟发生器 | R3,R4 | R1,R2 |

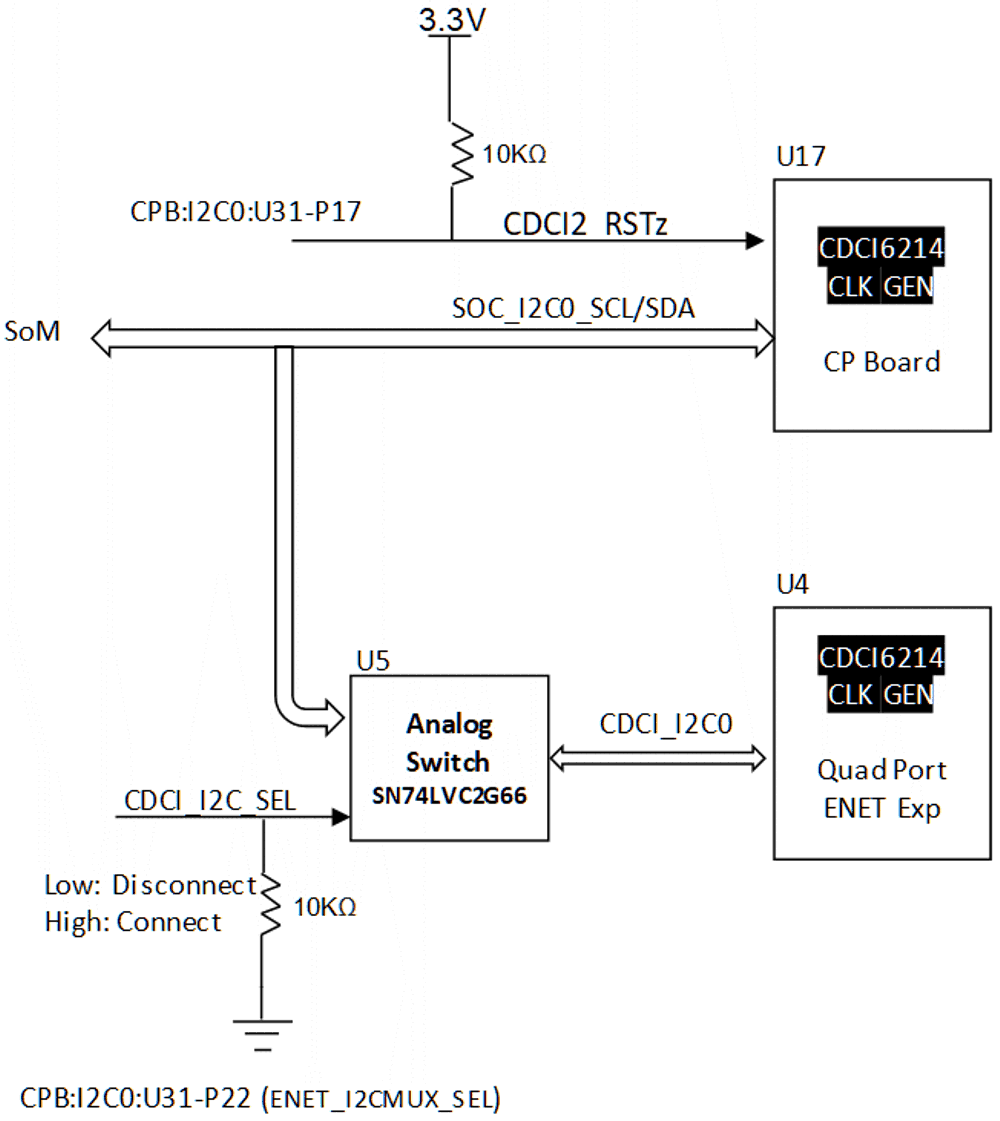

如果使用备用时钟源作为参考时钟,时钟生成的编程通过 SoC 的 I2C0 端口来完成。发送到板载时钟发生器的 I2C 信号通过一个有源开关进行连接,并通过将 CDCI_I2C_SEL 信号拉低来断开路径。由于板载时钟发生器和 CP 板时钟发生器具有相同的 I2C 从器件地址,对这些时钟发生器进行编程时需要特别注意。在对板载时钟发生器进行编程时,通用处理器板上的时钟发生器 (CDCI2) 需要处于复位状态。

图 4-18 四路 SGMII 板 I2C

图 4-18 四路 SGMII 板 I2C在 QSGMII 数据信号的各个驱动器端以串联方式添加了耦合电容器 (0.1μF)。

下面列出了地址和时钟配置:

PHY0:10000 0X10

PHY1:10001 0X11

PHY2:10010 0X12

PHY3:10011 0X13

图 4-19 显示了电阻器搭接选项。

图 4-19 QSGMII 以太网 PHY 设置

图 4-19 QSGMII 以太网 PHY 设置