ZHCU923A October 2020 – February 2022

- 商标

- 1引言

- 2J7200 EVM 概述

- 3EVM 用户设置/配置

- 4J7200 EVM 硬件架构

- 5功能安全

- 6修订历史记录

4.14.1 MCU CAN0

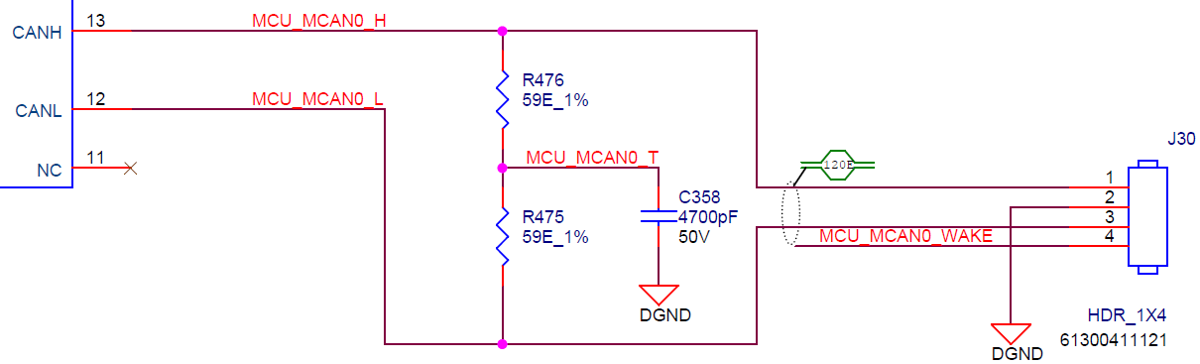

J7200 SoC 的 MCU CAN0 端口连接到支持唤醒功能的 CAN 收发器器件 TCAN1043-Q1。提供了一个用于用户探头选项的直插式 2 引脚接头 J29 (68002-202HLF)。

CAN 收发器的输出端接至一个 4 引脚接头 J30 (61300411121)。

信号 MCU_MCAN0_H 和 MCU_MCAN0_L 通过分裂终端路由为具有 120E 阻抗的差分信号。分裂终端可消除开始和结束消息传输时出现的总线共模电压波动,从而改善网络的电磁辐射性能。

图 4-31 MCU CAN0 接口

图 4-31 MCU CAN0 接口CAN 收发器的 VSYS_MCU_5V0 是使用升压转换器 TPS61240DRV 通过将 VSYS_3V3 用作转换器的输入电源生成的。

STB 信号是低电平有效信号,默认情况下使用集成下拉电阻器保持低电平。

通过通用处理器板左下角的按钮 SW12 来提供 CAN 接口的硬件 WAKEn 输入。不过,默认情况下 MCU_CAN0 唤醒功能(电阻器组装)被禁用。仅支持来自主域的 CAN 唤醒。