ZHCU932A December 2021 – April 2022 DLP2021-Q1

4.1.6 闪存块

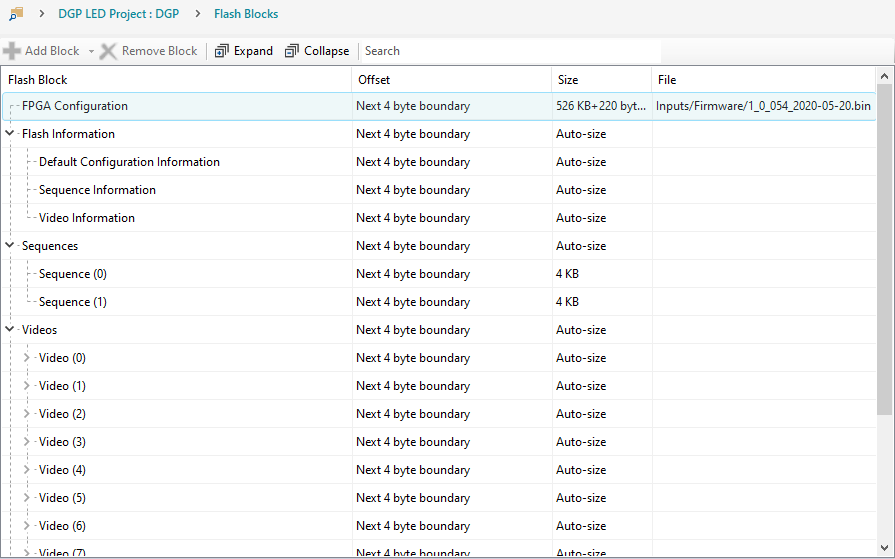

DGP 系统的闪存分为五个主要块:闪存二进制文件的创建完全由 DLP Composer 负责。适用于 Xilinx XA7S15-1CPGA196Q Spartan®-7 FPGA 的 FPGA 配置已被编译并包含在米6体育平台手机版_好二三四 (TI) 提供的示例项目中。

图 4-6 DLP Composer - 闪存块

图 4-6 DLP Composer - 闪存块| 数据 | 地址 | 长度 |

|---|---|---|

|

FPGA 配置 |

0x0 |

0x838DC |

|

闪存信息 |

0x83900 |

变量 |

|

默认配置 (Defconfig) |

变量 |

变量 |

|

序列 1 |

变量 |

0x1000 |

|

序列 2 |

变量 |

0x1000 |

|

序列... |

变量 |

0x1000 |

|

序列 n |

变量 |

0x1000 |

|

视频/图像 1 |

变量 |

变量 |

|

视频/图像 2 |

变量 |

变量 |

|

视频/图像... |

变量 |

变量 |

|

视频/图像 n |

变量 |

变量 |

FPGA 配置

FPGA 配置块始终位于地址 0x0 处,固定大小始终为 0x838DC 字节。该大小从 Xilinx XA7S15 规格中得出,用于最大配置长度。有关其他信息,请参阅 (https://www.xilinx.com/support/documentation/user_guides/ug470_7Series_Config.pdf) 。

闪存信息

闪存信息块提供关于闪存内容的元数据,用于帮助外部 MCU 或软件工具了解闪存内容。例如,闪存信息块定义了视频在闪存内的位置,以便 MCU(例如 EVM 上的 MSP430G2553-Q1)能够动态地加载这些视频。闪存信息块被分为如表 4-2 中所示的四个主要部分。可提供序列数等信息,以便软件可以导航闪存块并确定目标数据的正确偏移。信息块中的序列数和视频条目是可变的,但每个条目的大小固定。

| 偏移(十六进制) | 0 | 1 | 2 | 3 |

|---|---|---|---|---|

|

00 |

主要 |

次要 |

补丁 | |

|

04 |

“D” |

“E” |

“F” |

“C” |

|

08 |

块地址 | |||

|

0C |

计数(寄存器写入次数) | |||

|

10 |

“S” |

“E” |

“Q” |

“L” |

|

14 |

大小(序列块) | |||

|

18 |

计数(序列数) | |||

|

1C |

序列 0 地址 | |||

|

20 |

序列 0 红色占空比 |

序列 0 绿色占空比 | ||

|

24 |

序列 0 蓝色占空比 |

序列 0 帧速率 | ||

|

28 |

序列 1 地址 | |||

|

2C |

序列 1 红色占空比 |

序列 1 红色占空比 | ||

|

30 |

序列 1 蓝色占空比 |

序列 1 蓝色占空比 | ||

|

34 |

序列...地址 | |||

|

38 |

序列...红色占空比 |

序列...红色占空比 | ||

|

3C |

序列...蓝色占空比 |

序列...蓝色占空比 | ||

|

变量 |

“V” |

“I” |

“D” |

“E” |

|

变量 |

大小(视频块) | |||

|

变量 |

计数(视频数量) | |||

|

变量 |

视频 0 地址 | |||

|

变量 |

视频 0 帧速率 |

视频 0 帧计数 | ||

|

变量 |

视频 1 地址 | |||

|

变量 |

视频 1 帧速率 |

视频 1 帧速率 | ||

|

变量 |

视频...地址 | |||

|

变量 |

视频...帧速率 |

视频...帧速率 | ||

序列

序列是由 DLP Composer 根据所选占空比生成的。每个序列条目在闪存中保存 4kB 的空间。

视频

视频和静态图像内容是 DLP Composer 中动态地面投影项目的输入。Composer 接收并扩展内容,将其转换为一系列 DMD 原生的位平面格式,然后使用行程编码 (RLE) 进行压缩,以便将其存储在闪存中。当需显示视频和静态图像时,FPGA 将解压缩每个位平面,并按顺序和序列指定的时序显示。

默认配置

默认配置块是每个 FPGA 寄存器的数值集合。该信息在 FPGA 配置完成后由 FPGA 加载。这些值会取代 DLP2021-Q1 FPGA 用户指南 中所述的上电默认值。可在 Default Register Configuration 页面上使用 DLP Composer 来设置默认配置值。