ZHCU972D March 2022 – September 2023 AM2631 , AM2631-Q1 , AM2632 , AM2632-Q1 , AM2634 , AM2634-Q1

A E2 设计变更

AM263x 控制卡针对 E2 版本的电路板具有多处设计变更。这些变更列出如下:

- 将 QSPI 闪存 D2 和 D3 信号的上拉电阻器移除。

- 数据线 D2 和 D3 上的上拉电阻器与 QSPI 闪存本身的片上电阻器是冗余的。

- 修复了网表错误并重新路由 I2C2_SDA 和 I2C2_SCL 以便正常运行。

- E1 版本控制卡的 I2C2_SCL 信号连接到球 B7,I2C2_SDA 连接到 C7。在 E2 控制卡中实现信号的正确路由,其中 I2C2_SDA 连接到 B7、I2C2_SCL 连接到 C7 。表 A-1 I2C2 信号路由

信号 E1 引脚布线 E2 引脚布线 I2C2_SDA C7 B7 I2C2_SCL B7 C7

- E1 版本控制卡的 I2C2_SCL 信号连接到球 B7,I2C2_SDA 连接到 C7。在 E2 控制卡中实现信号的正确路由,其中 I2C2_SDA 连接到 B7、I2C2_SCL 连接到 C7 。

- 以太网 PHY 默认模式从基本模式更改为增强模式。

- 由于 PHY MODESELECT 引脚上具有下拉电阻器,E1 中的以太网 PHY (DP83826ERHBT) 默认模式为基本模式。E2 采用卡拉电阻器替换下拉电阻器,如此默认模式为增强模式。增强模式允许 PHY 支持实时以太网应用。

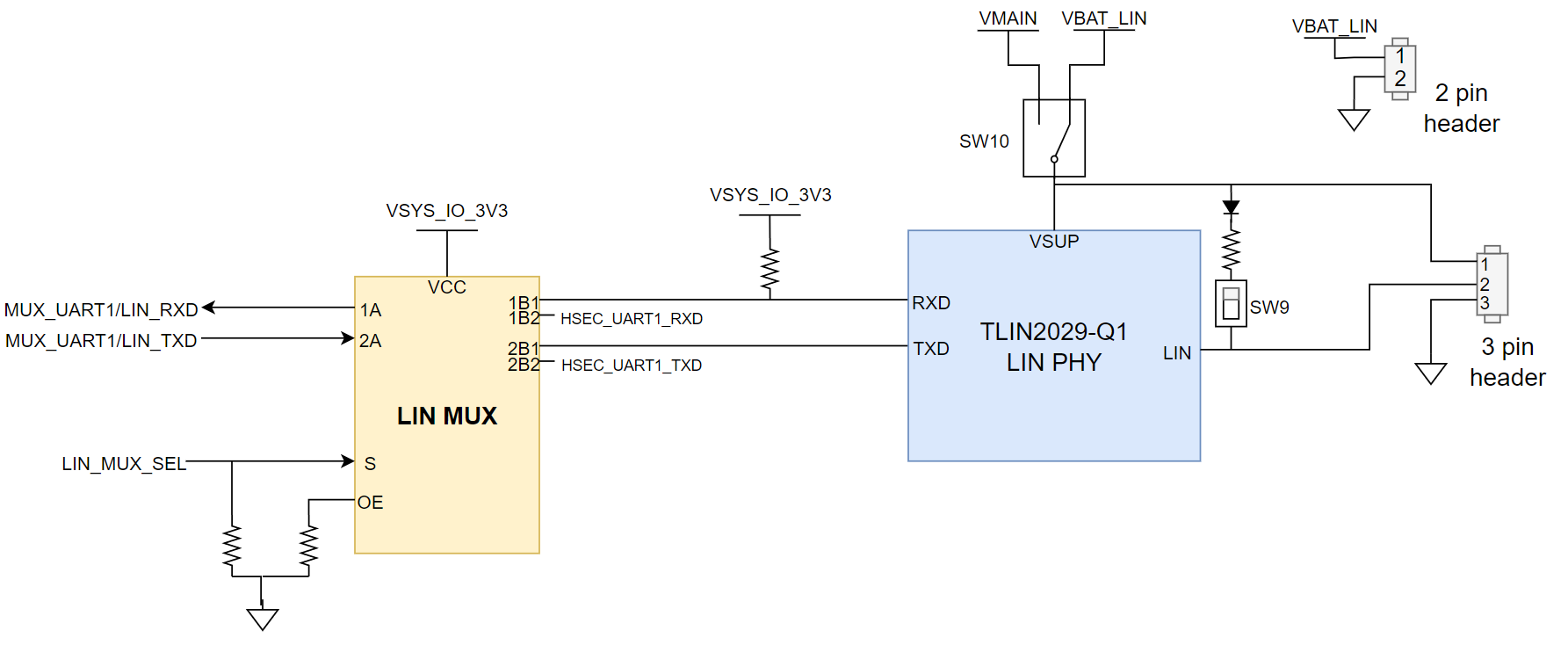

- 增加板载 LIN PHY (TLIN2029-Q1)。

- 为了支持 LIN PHY,增加了 1:2 多路复用器 (U70),这样 LIN1_RXD 和 LIN1_TXD 就可以与 PHY 连接,而不会丢失 UART1_RXD 和 UART1_TXD 的信号路径。

- 增加两个附加接头以支持 LIN PHY 的电压 (J33) 和输出 (J32) 表 A-2 LIN 多路复用器选择表

选择线路 条件 功能 低电平 选择 LIN A->B1 端口 高电平 选择 HSEC UART A->B2 端口  图 A-1 LIN PHY

图 A-1 LIN PHY

- 增加了其他串联端接电阻器。

- 在隔离缓冲器 (U49) 的输出处为 XDS110 TMS 和 TCK 信号放置了 33Ω 电阻器。在隔离缓冲器 (U53) 的 OUTA 上为 XDS110 TDI 信号放置了一个 33Ω 电阻器。

- 在三个隔离缓冲器的输出上放置了串联端接电阻器,以便更好地控制边沿过冲/下冲。 表 A-3 E2 端接电阻器位置表

隔离缓冲器输出引脚 信号名称 串联端接电阻器值 U45.2 UART0_RXD 33Ω U49.6 XDS110_TCK_ISO 33Ω U49.7 XDS110_TMS_ISO 33Ω U53.2 XDS110_TDI_ISO 33Ω

- 更新了 DC-DC 转换器解决方案元件。

- 负责生成 3.3V 电压轨和 1.2V 电压轨的 DC-DC 降压转换器均替换为 TSP62913RPUR 降压转换器。 表 A-4 E2 降压转换器表

DC-DC转换 E1 降压转换器 E2 降压转换器 5V -> 3.3V TPS54334DRCT TPS62913RPUR 3.3V -> 1.2V TPS62826DMQR TPS62913RPUR

- 负责生成 3.3V 电压轨和 1.2V 电压轨的 DC-DC 降压转换器均替换为 TSP62913RPUR 降压转换器。

- 更新了无源元件。

- C136 和 C1861 从 1210 替换为 0805

- L3 和 L4 从 744316100 替换为 IHLP2020BZER1R0M01

- 更改了 HSEC ADC 连接。表 A-5 E2 HSEC 连接器映射

HSEC 引脚 E1 信号 E2 信号 1 NC NC 2 NC NC 3 TMS TMS 4 NC NC 5 TCK TCK 6 TDO TDO 7 GND GND 8 TDI TDI 9 DAC_OUT ADC0_AIN0/DAC_OUT 10 GND GND 11 ADC0_AIN0_P ADC0_AIN1/DAC_OUT 12 ADC0_AIN0_n ADC1_AIN0 13 GND GND 14 ADC0_AIN1_p ADC1_AIN1 15 ADC0_AIN1_n ADC0_AIN2 16 GND GND 17 ADC0_AIN2_p ADC0_AIN3 18 ADC0_AIN2_n ADC1_AIN2 19 GND GND 20 ADC1_AIN0_p ADC1_AIN3 21 ADC1_AIN0_n ADC0_AIN4 22 GND GND 23 ADC1_AIN1_p ADC0_AIN5 24 ADC1_AIN1_n ADC1_AIN4 25 ADC1_AIN2_p ADC4_AIN0/ADC_CAL0 26 ADC1_AIN2_n ADC1_AIN5 27 ADC2_AIN0_p ADC4_AIN1/ADC_CAL1 28 ADC2_AIN0_n ADC3_AIN0 29 GND GND 30 ADC2_AIN1_p ADC3_AIN1 31 ADC2_AIN1_n ADC2_AIN0 32 NC GND 33 ADC2_AIN2_p ADC2_AIN1 34 ADC2_AIN2_n ADC3_AIN2 35 GND GND 36 ADC3_AIN0_p ADC3_AIN3 37 ADC3_AIN0_n ADC2_AIN2 38 GND GND 39 ADC3_AIN1_p ADC2_AIN3 40 ADC3_AIN1_n ADC3_AIN4 41 NC NC 42 ADC3_AIN2_p ADC3_AIN5 43 ADC_VREFLO GND 44 NC NC 45 ADC_VREFhi ADC_VREFH 表 A-6 E1 ADC 通道信号ADC0 AIN0p AIN0n AIN1p AIN1n AIN2p AIN2n ADC1 AIN0p AIN0n AIN1p AIN1n AIN2p AIN2n ADC2 AIN0p AIN0n AIN1p AIN1n AIN2p AIN2n ADC3 AIN0p AIN0n AIN1p AIN1n AIN2p GND ADC4 GND GND GND GND GND GND 表 A-7 E2 ADC 通道信号ADC0 AIN0 AIN1 AIN2 AIN3 AIN4 AIN5 ADC1 AIN0 AIN1 AIN2 AIN3 AIN4 AIN5 ADC2 AIN0 AIN1 AIN2 AIN3 GND GND ADC3 AIN0 AIN1 AIN2 AIN3 AIN4 AIN5 ADC4 AIN0 AIN1 GND GND GND GND - 增加了两个 2:1 多路复用器以支持新的 HSEC ADC 连接。表 A-8 E2 HSEC 多路复用器表

MUX_SEL 信号 条件 函数 说明 ADC1_MUX_SEL SEL 信号高电平 S1A->D1 将 HSEC_ADC0_AIN0 路由到 AM263 S2A->D2 将 HSEC_ADC0_AIN1 路由到 AM263 SEL 信号低电平 S1B->D1 将 HSEC_DAC_OUT 路由到 AM263 S2B->D2 将 HSEC_DAC_OUT 路由到 AM263 ADC2_MUX_SEL SEL 信号高电平 S1A->D1 将 HSEC_ADC4_AIN0 路由到 AM263 S2A->D2 将 HSEC_ADC4_AIN1 路由到 AM263 SEL 信号低电平 S1B->D1 将 ADC_CAL0 路由到 AM263 S2B->D2 将 ADC_CAL0 路由到 AM263 - 更新了 ADC ESD 连接。表 A-9 E2 ESD 连接映射

E1 ESD 引脚 E1 信号 E2 ESD 引脚 E2 信号 U26.1 HSEC_ADC0_AIN0_P U35.1 HSEC_ADC0_AIN0/DAC_OUT U26.2 GND U35.2 GND U26.3 HSEC_ADC0_AIN0_N U35.3 HSEC_ADC0_AIN1/DAC_OUT U26.4 HSEC_ADC0_AIN1_N U35.4 HSEC_ADC4_AIN0/ADC_CAL0 U26.5 VDDA_IO_1V8 U35.5 VDDA_IO_3V3 U26.6 HSEC_ADC0_AIN1_P U35.6 HSEC_ADC4_AIN1/ADC_CAL1 U27.1 HSEC_ADC0_AIN2_P U36.1 HSEC_ADC1_AIN0 U27.2 GND U36.2 GND U27.3 HSEC_ADC0_AIN2_N U36.3 HSEC_ADC1_AIN1 U27.4 HSEC_ADC1_AIN0_N U36.4 HSEC_ADC0_AIN3 U27.5 VDDA_IO_1V8 U36.5 VDDA_IO_3V3 U27.6 HSEC_ADC1_AIN0_P U36.6 HSEC_ADC0_AIN2 U28.1 HSEC_ADC1_AIN1_P U37.1 HSEC_ADC2_AIN0 U28.2 GND U37.2 GND U28.3 HSEC_ADC1_AIN1_N U37.3 HSEC_ADC2_AIN1 U28.4 HSEC_ADC1_AIN2_N U37.4 HSEC_ADC0_AIN5 U28.5 VDDA_IO_1V8 U37.5 VDDA_IO_3V3 U28.6 HSEC_ADC1_AIN2_P U37.6 HSEC_ADC0_AIN4 U29.1 HSEC_ADC2_AIN0_P U38.1 HSEC_ADC3_AIN0 U29.2 GND U38.2 GND U29.3 HSEC_ADC2_AIN0_N U38.3 HSEC_ADC3_AIN1 U29.4 HSEC_ADC2_AIN1_N U38.4 HSEC_ADC3_AIN3 U29.5 VDDA_IO_1V8 U38.5 VDDA_IO_3V3 U29.6 HSEC_ADC2_AIN1_P U38.6 HSEC_ADC3_AIN2 U30.1 HSEC_ADC2_AIN2_P U39.1 HSEC_ADC3_AIN4 U30.2 GND U39.2 GND U30.3 HSEC_ADC2_AIN2_N U39.3 HSEC_ADC3_AIN5 U30.4 HSEC_ADC3_AIN0_N U39.4 HSEC_ADC2_AIN3 U30.5 VDDA_IO_1V8 U39.5 VDDA_IO_3V3 U30.6 HSEC_ADC3_AIN0_P U39.6 HSEC_ADC2_AIN2 U31.1 HSEC_ADC3_AIN1_P U40.1 HSEC_ADC1_AIN2 U31.2 GND U40.2 GND U31.3 HSEC_ADC3_AIN1_N U40.3 HSEC_ADC1_AIN3 U31.4 HSEC_ADC3_AIN2_P U40.4 HSEC_ADC1_AIN4 U31.5 VDDA_IO_1V8 U40.5 VDDA_IO_3V3 U31.6 NC U40.6 HSEC_ADC1_AIN5