ZHCUA92D May 2022 – September 2023

4.6.1 以太网 PHY #1 - CPSW RGMII/ICSSM

注: TRM 中提供的 PRU 内部引脚多路复用映射是 PRU 原始硬件定义的一部分。但是,由于 IP 和相关固件配置提供的灵活性,这未必是硬性要求。AM65x 的第一个 PRU 实施方案在初始 SoC 集成期间交换了 MII TX 引脚,并在后续 PRU 修订版中保留了该约定,以实现固件重用。要使用 SDK 固件,请使用 SYSCONFIG 生成的 PRU 引脚映射。

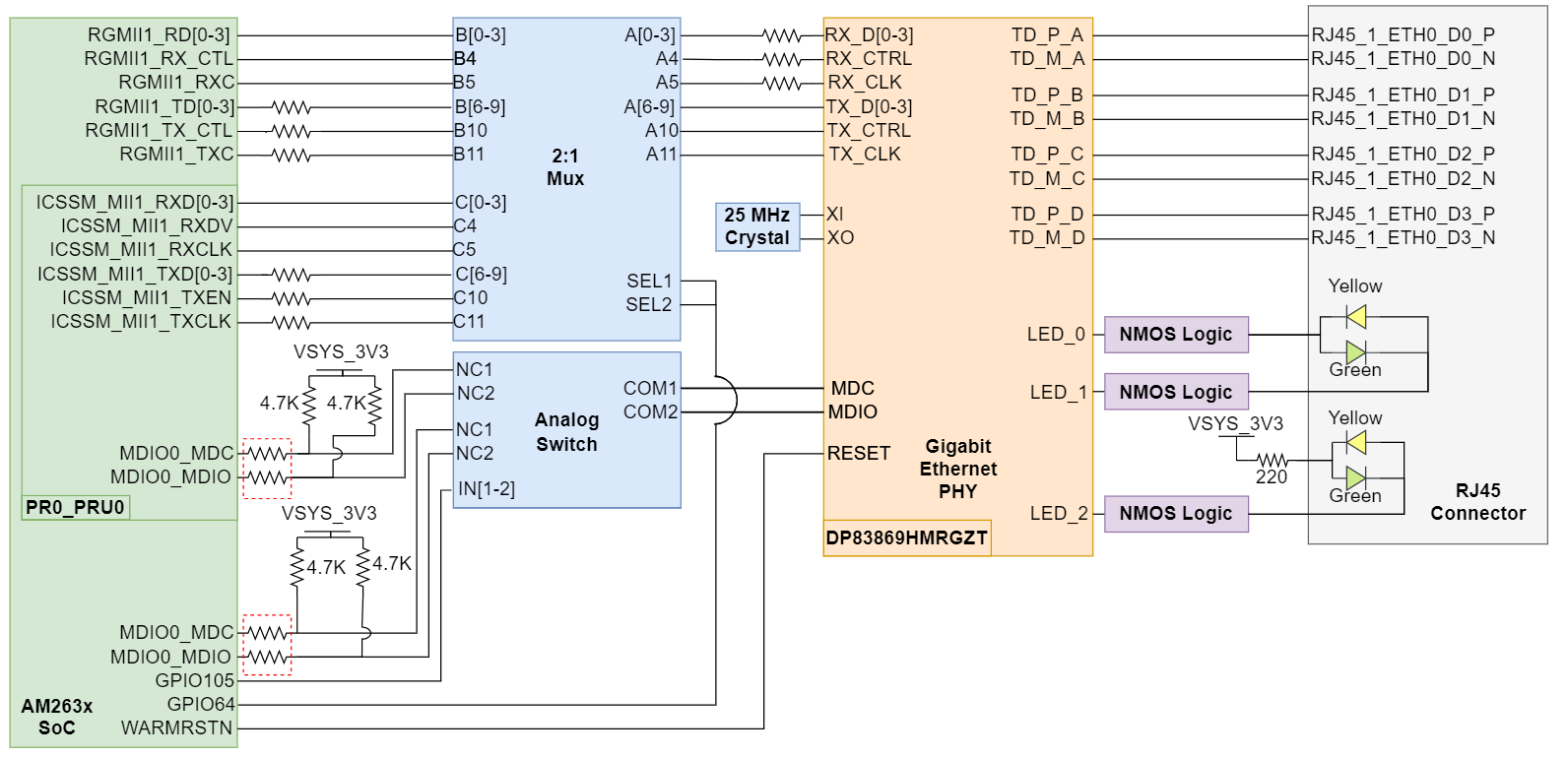

AM263x LaunchPad 采用一个 48 引脚以太网 PHY (DP83869HMRGZT),该 PHY 连接到 CPSW RGMII 或一个片上可编程实时单元和工业通信子系统 (PRU-ICSS)。2:1 多路复用器负责在 RGMII 或 PRU-ICSS 信号之间进行选择。该 PHY 配置为广播 1Gb 操作。该 PHY 的以太网数据信号端接至 RJ45 连接器。电路板使用 RJ45 连接器来提供以太网 10/100/1000Mbps 连接,并集成电磁元件和 LED 来提供链路和活动指示。

A. 用红色虚线框标出的串联终端电阻从 0Ω 更新为 33Ω,以提高 AM263x MCU MDIO 引脚和连接的 PHY 引脚之间的信号完整性。修改由 LaunchPad 顶部靠近 PORz 按钮的“M1”标签表示。

图 4-8 以太网 PHY #1该以太网 PHY 需要三个单独的电源。VDDIO 是系统生成的 3.3V 电源。另外还有专用的 LDO 作为以太网 PHY 的 1.1V 和 2.5V 电源。

靠近 SoC 的发送时钟和数据信号上存在串联终端电阻器。靠近以太网 PHY 的接收时钟和数据信号上存在串联终端电阻器。

从 SoC 到 PHY 的 MDC 和 MDIO 信号需要将 4.7KΩ 上拉电阻器连接到 3.3V 系统电源电压,才能正常工作。模拟开关 (TS5A23159DGSR) 负责在 CPSW MDIO/MDC 和 ICSSM MDIO/MDC 信号之间进行选择并将其中一个信号路由至以太网 PHY。

2:1 多路复用器和模拟开关都由负责在 CPSW RGMII 和 ICSSM 信号之间进行选择的 GPIO 信号控制。

表 4-2 以太网 PHY #1 CPSW/ICSSM 选择

| GPIO105 | 条件 | 多路复用器的功能 |

|---|---|---|

| 低电平 | 已选择 RGMII CPSW | 端口 A ↔ 端口 B |

| 高电平 | 已选择 ICSSM | 端口 A ↔ 端口 C |

该以太网 PHY 的复位输入由 WARMRESET AM263x SoC 输出信号控制。

以太网 PHY 将很多功能引脚用作配置 (strap) 选项,以便使器件工作在特定的模式下。

表 4-3 以太网 PHY #1 配置 (strap) 电阻器

| 功能引脚 | 默认模式 | LP 中的模式 | 功能 |

|---|---|---|---|

| RX_D0 | 0 | 3 | PHY 地址:0011 |

| RX_D1 | 0 | 0 | |

| JTAG_TDO/GPIO_1 | 0 | 0 | RGMII 至铜缆 |

| RX_D3 | 0 | 0 | |

| RX_D2 | 0 | 0 | |

| LED_0 | 0 | 0 | 自动协商,广播 1000/100/10,自动 MDI-X |

| RX_ER | 0 | 0 | |

| LED_2 | 0 | 0 | |

| RX_DV | 0 | 0 | 端口镜像已禁用 |

注: 每个配置 (strap) 引脚都具有一个 9KΩ 的内部下拉电阻

注: RX_D0 和 RX_D1 都采用 4 级配置 (strap) 电阻器模式方案。所有其他信号都采用 2 级配置 (strap) 电阻器模式。