ZHCUA92D May 2022 – September 2023

3.3 引导模式选择

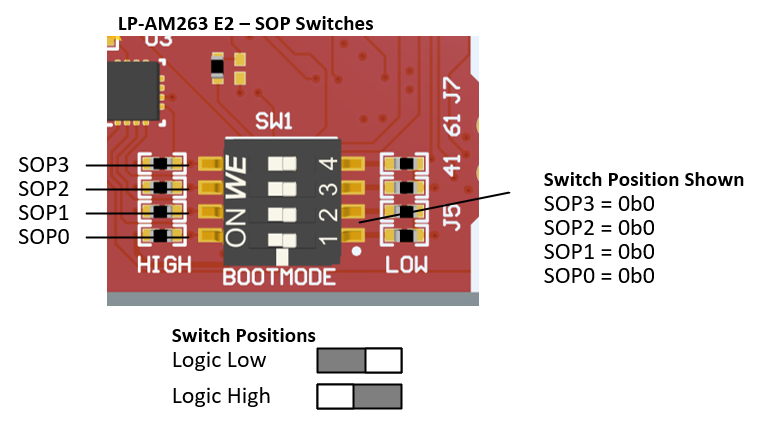

AM263x 的引导模式由 DIP 开关 (SW1) 或测试自动化接头选择。当PORz 切换时,测试自动化接头使用 I2C 扩展缓冲器来驱动引导模式。表 3-6 展示了支持的引导模式。表 3-5 展示了每种引导模式的 DIP 开关配置。

图 3-6 引导模式 DIP 开关位置

图 3-6 引导模式 DIP 开关位置表 3-5 引导模式选择

| 启动模式 | SPI0_D0_pad (SOP3) | SPI0_CLK_pad (SOP2) | QSPI_D1 (SOP1) | QSPI_D0 (SOP0) |

|---|---|---|---|---|

| QSPI (4S) - 四路读取模式 | 1 | 1 | 1 | 1 |

| UART | 1 | 1 | 1 | 0 |

| QSPI (1S) - 单路读取模式 | 1 | 1 | 0 | 1 |

| QSPI (4S) - 四路读取 UART 回退模式 | 1 | 0 | 1 | 1 |

| QSPI (1S) - 单路读取 UART 回退模式 | 1 | 0 | 1 | 0 |

| DevBoot | 0 | 1 | 0 | 0 |

| 不受支持的引导模式 | 上文未定义的所有其他组合 | |||

表 3-6 支持的引导模式

| 引导模式/外设 | 引导介质/主机 | 注释 |

|---|---|---|

| QSPI (4S) - 四路读取模式 | QSPI 闪存 | 在四路读取模式下从 QSPI 闪存下载并引导 SBL。先尝试初级 SBL,如果初级 SBL 加载失败,则接着尝试次级 SBL。 |

| UART | 外部主机 | 从 UART 下载并引导 SBL。器件预期从 UART 获得 SBL。器件支持 XMODEM 协议以便通过 UART 进行下载。 |

| QSPI (1S) - 单路读取模式 | QSPI 闪存 | 在单路读取模式下从 QSPI 闪存下载并引导 SBL。先尝试初级 SBL,如果初级 SBL 加载失败,则接着尝试次级 SBL。 |

| QSPI (4S) - 四路读取 UART 回退模式 | QSPI 闪存/外部主机 | 在四路读取模式下从 QSPI 闪存下载并引导 SBL。先尝试初级 SBL,如果初级 SBL 加载失败,则接着尝试次级 SBL。如果次级 SBL 也失败,则通过 UART 接口从外部主机引导。 |

| QSPI (1S) - 单路读取 UART 回退模式 | QSPI 闪存/外部主机 | 在单路读取模式下从 QSPI 闪存下载并引导 SBL。先尝试初级 SBL,如果初级 SBL 加载失败,则接着尝试次级 SBL。如果次级 SBL 也失败,则通过 UART 接口从外部主机引导。 |

| DevBoot | 不适用 | 无 SBL。仅用于开发目的。 |