ZHCUAE0 March 2021

2 功能

TSW14J58EVM 具有一个业界通用 FMC+ 连接器,可直接与 TI JESD204B ADC、DAC 和 AFE EVM 连接。FMC+ 载板连接器与 FMC 夹层连接器兼容。当与 ADC EVM 结合使用时,高速串行数据由 Xilinx® Kintex® UltraScale® + FPGA 进行采集、解串行化和格式化。然后,数据存储到外部 DDR4 存储器组中,使 TSW14J58 能够存储多达 1.536G 的 16 位数据样本。为了在主机 PC 上采集数据,FPGA 从存储器中读取数据,并通过高速 16 位并行接口进行传输。连接至并行转换器的板载高速 USB 3.0 可将 FPGA 接口与主机 PC 和 GUI 桥接在一起。

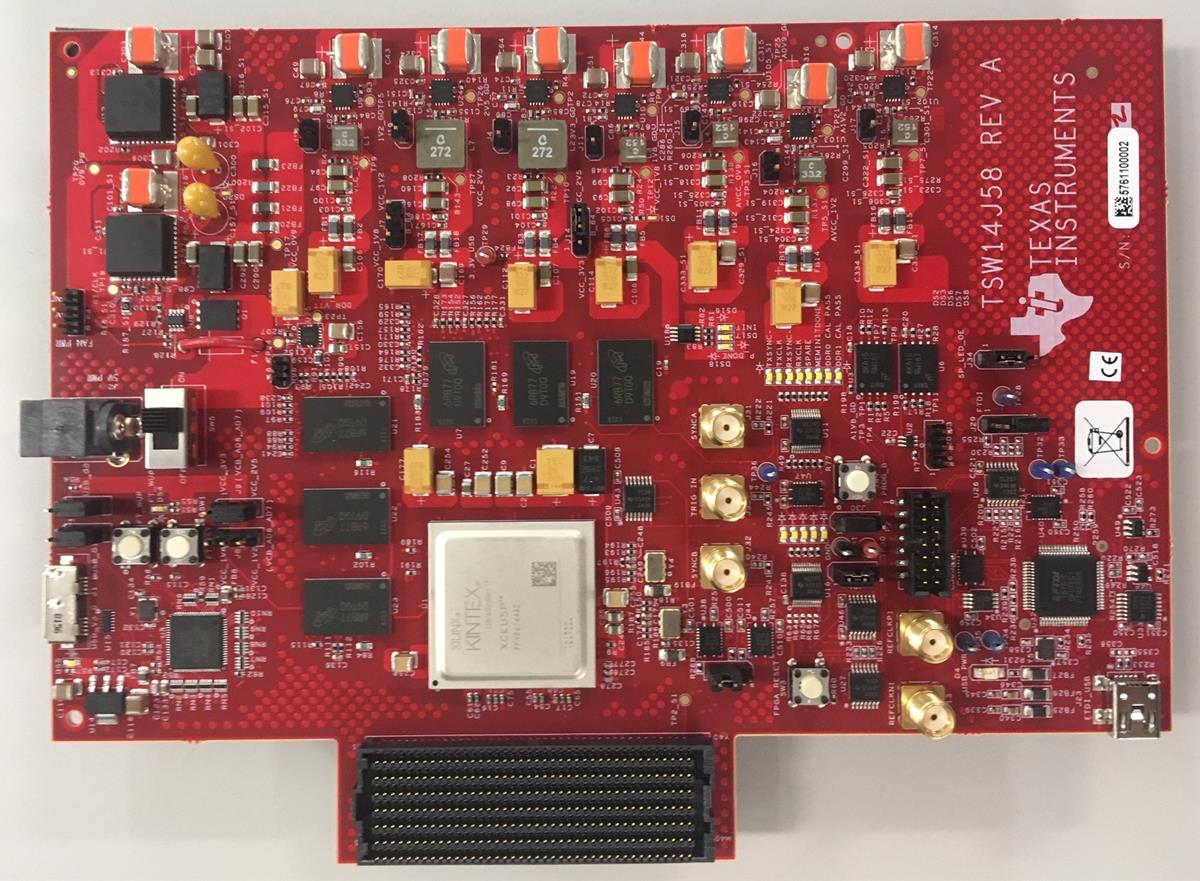

在图形发生器模式下,TSW14J58 为受测的 DAC EVM 生成所需的测试图形。这些图形通过 USB 接口从主机 PC 发送到 TSW14J58。FPGA 将接收到的数据存储到板载 DDR4 存储器模块中。然后,存储器中的数据由 FPGA 读取,并通过 FMC+ 接口连接器传输到 DAC EVM。该电路板包含一个 200MHz 振荡器,用于生成 DDR4 参考时钟和一个通用时钟。图 2-1 显示了 TI TSW14J58 评估模块。

图 2-1 TSW14J58EVM

图 2-1 TSW14J58EVMTSW14J58 的主要特性包括:

- 与 JESD204B 向后兼容(子级:0 1、2)

- 支持确定性延迟

- 串行通道速度高达 24.5Gbps

- 16 个路由收发器通道

- 24Gb DDR4 SDRAM(分成两组,每组 3 个独立的 256 × 16、4Gb SDRAM)。四分之一速率 DDR4 控制器,支持高达 1200MHz 操作

- 1.536G 的 16 位板载存储器样本

- 对于备用 FMC+ 信号支持 1.8V CMOS IO 标准

- 通用 200MHz 振荡器

- 板载 FTDI FT601Q-B USB 3.0 器件,用于与 FPGA 并行连接

- 板载 FTDI FT4232H USB 2.0 器件,用于 FPGA JTAG 接口(下载固件)和通用 I/O 接口(用于连接板载功能和 FMC+)

- 通过 FMC+ 端口或 SMA 提供的收发器参考时钟

- 由 TI HSDC PRO 软件支持

- 使用 Xilinx Vivado 开发工具开发的 FPGA 固件。

- JESD RX IP 内核,支持:

- 可通过 USB 和 JTAG 重新配置的 JESD 内核参数:L、M、K、F、HD、S 等等

- 可通过 USB 和 JTAG 访问的 ILA 配置数据

- 通过 USB 和 JTAG 启用或禁用通道对齐和字符替换

- JESD TX IP 内核,支持:

- 可通过 USB 和 JTAG 重新配置的 JESD 内核参数:L、M、K、F、HD、S 等等

- 可通过 USB 和 JTAG 访问的 ILA 配置数据

- 动态可重新配置的收发器数据速率。

- 串行通道工作范围为 1Gbps 至 24.5Gbps

- JESD RX IP 内核,支持:

图 2-2 显示了 TSW14J58 EVM 的方框图。

图 2-2 TSW14J58EVM 方框图

图 2-2 TSW14J58EVM 方框图