ZHCUAG3F August 2021 – January 2024 AM2431 , AM2432 , AM2434

4.5 时钟

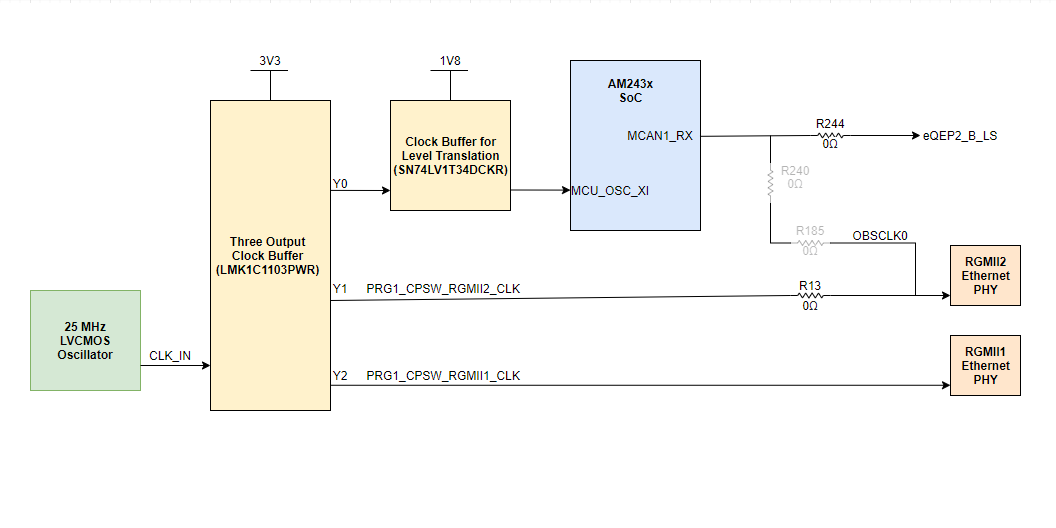

SoC 和两个以太网 PHY 的所有参考时钟都是由单个三路输出时钟缓冲器 (LMK1C1103PWR) 生成的,源自单个 25MHz LVCMOS 振荡器。单输出时钟缓冲器 (SN74LV1TT34DCKR) 用于将 3.3V 电平转换为 1.8V。SoC 的 OBSCLK0 输出通过安装 R240 和 R185 并同时隔离 R244 和 R13 来为 RGMII2 以太网 PHY 提供可选时钟。

XDS110 所需的参考时钟由一个 16MHz 晶振在本地生成。

图 4-6 时钟架构

图 4-6 时钟架构表 4-16 时钟频率表

| SI 编号 | 信号名称 | 参考文献 | 预期频率 |

|---|---|---|---|

| 1 | SOC_CLKIN | U11.4 | 25.000 MHz |

| 2 | SOC_CLKIN_BUFF | R46 | 25.000 MHz |

| 3 | PRG1_CPSW_RGMII1_CLK | R25 | 25.000 MHz |

| 4 | PRG1_CPSW_RGMII2_CLK | R50 | 25.000 MHz |

| 5 | OSC0 | Y1.3 | 16.000 MHz |

注: 只有在将电缆插入 micro-B USB 端口并为 micro-B USB 连接器供电后才会激活 16MHz 时钟。