ZHCUAG3F August 2021 – January 2024 AM2431 , AM2432 , AM2434

4.7 以太网接口

注: TRM 中提供的 PRU 内部引脚多路复用映射是 PRU 原始硬件定义的一部分。但是,由于 IP 和相关固件配置提供的灵活性,这未必是硬性要求。AM65x 的第一个 PRU 实施方案在初始 SoC 集成期间交换了 MII TX 引脚,并在后续 PRU 修订版中保留了该约定,以实现固件重用。要使用 SDK 固件,请使用 SYSCONFIG 生成的 PRU 引脚映射。

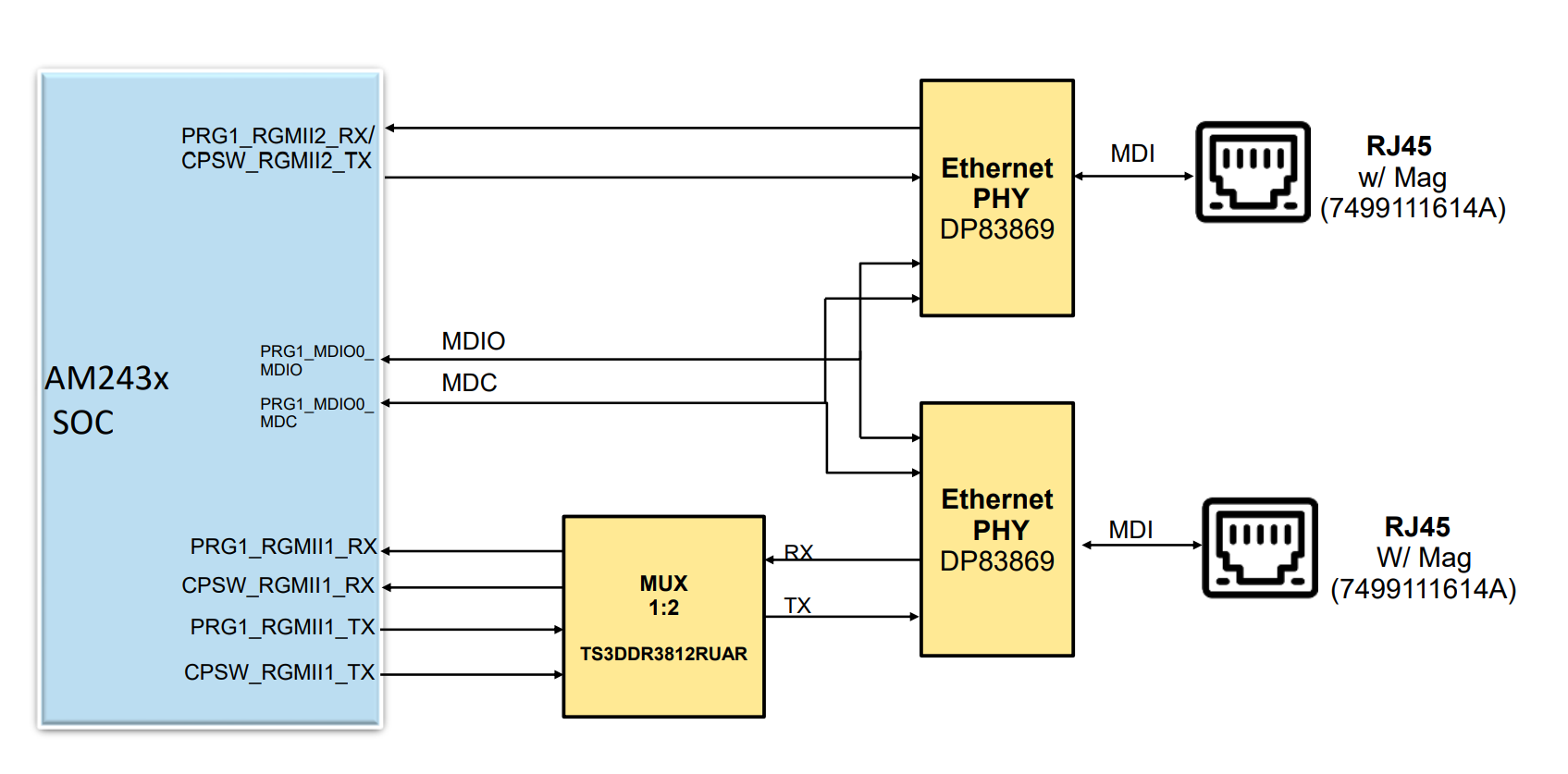

该 LaunchPad 支持两个以太网 PHY,这些 PHY 端接至具有集成磁性元件的 RJ45 连接器以用于外部通信。

图 4-9 以太网连接

图 4-9 以太网连接48 引脚 PHY (DP83869) 配置为可以广播千兆位操作,且其内部延迟设置为与 AM243x SoC 的内部延迟相适应。

第一个 PHY 连接到 SoC 的 PRG1/CPSW RGMII2 端口,这些端口在 SoC 中进行内部多路复用;此外,该 PHY 的 MDI 接口端接至具有集成磁性元件的 RJ45 连接器。

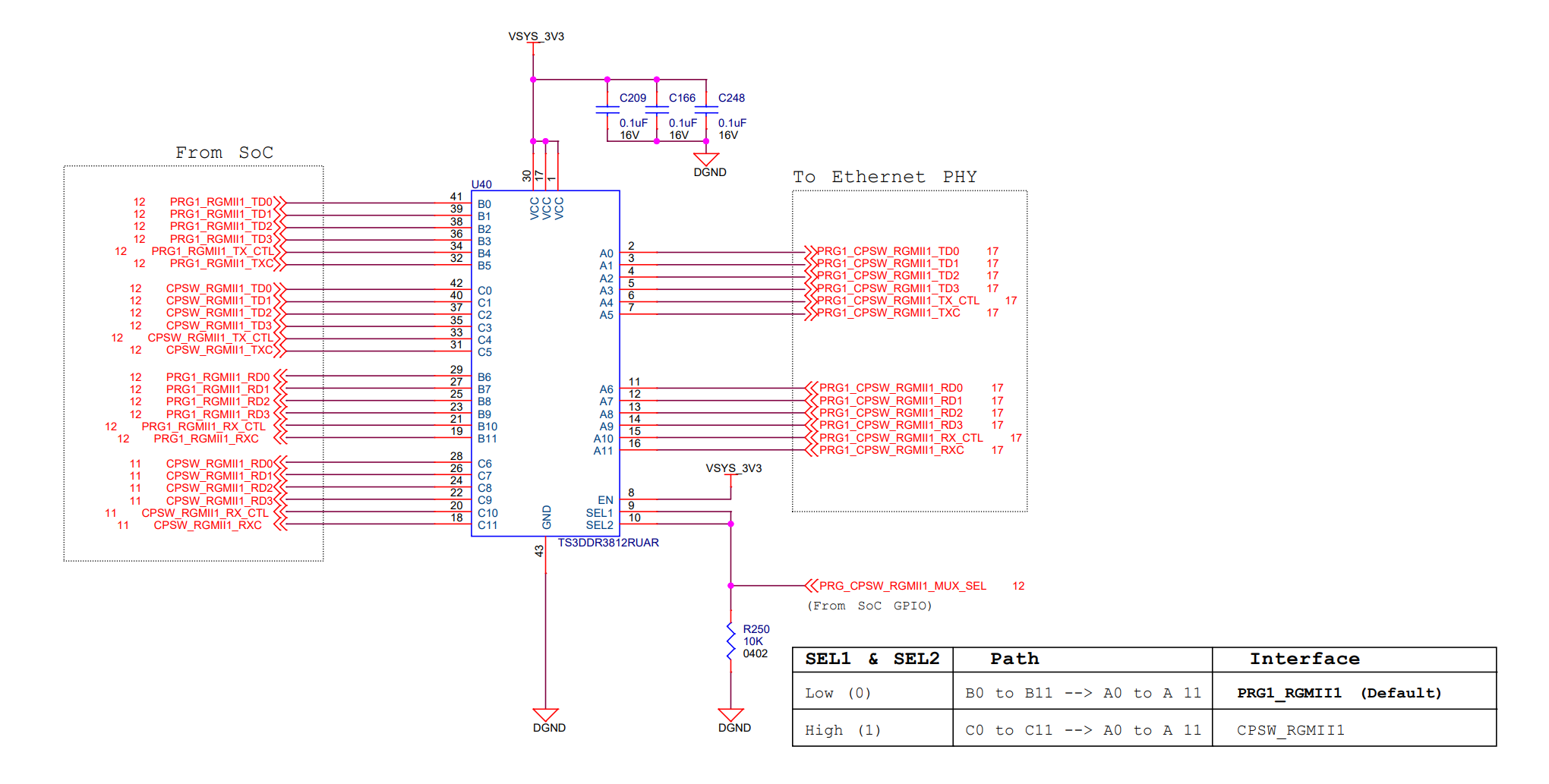

第二个 PHY 连接到 SoC 的 PRG1/CPSW RGMII1 端口,这些端口通过外部板载多路复用器进行多路复用,该多路复用器的选择线路由 SoC 的 GPIO (PRG_CPSW_RGMII1_MUX_SEL) 进行控制;此外该 PHY 的 MDI 接口也端接至具有集成磁性元件的 RJ45 连接器。采用 1:2 多路复用器 (TS3DDR3812RUAR) 在 PRG1 和 CPSW RGMII1 端口之间进行选择。

图 4-10 CPSW 或 PRG RGMII1 以太网数据多路复用器

图 4-10 CPSW 或 PRG RGMII1 以太网数据多路复用器针对这两个 PHY,为了在 PRG 和 CPSW 工作模式之间进行选择,必须从每个控制器中选择 MDIO 和 MDC 信号(这些信号在 SoC 内部进行多路复用)。

电路板上使用两个具有集成磁性元件和状态 LED 的 RJ45 连接器(Wurth 的 7499111614A)来实现以太网 10Mb/100Mb/1Gb 连接。