ZHCUAO8 December 2022

5.1.3.1 20GHz (FMCW) 射频 LO 同步

此参考设计基于 TI 的 AWR2243 雷达芯片。使用 20GHz LO 输入和输出路径,其中两个芯片会级联在一起并同步运行。这要求每个芯片的射频 LO 频率同步。AWR2243 合成器会在 19GHz 至 20.25GHz 范围内生成 LO,具体取决于编程的线性调频脉冲射频输出频率。

指定为主器件的 AWR2243 会生成一个公共本机振荡器 (LO) 信号(19GHz 至 20.25GHz),该信号将在整个级联系统中的所有发送器和接收器之间共享。

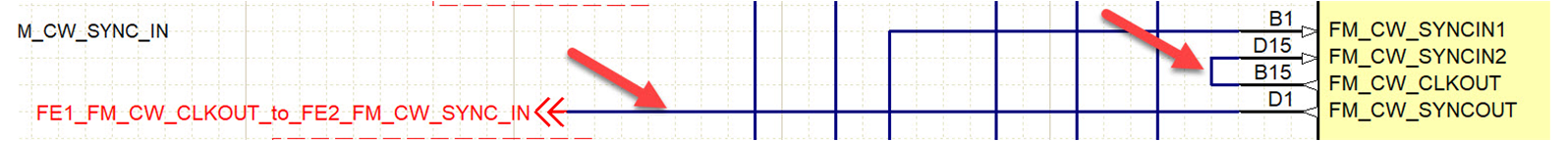

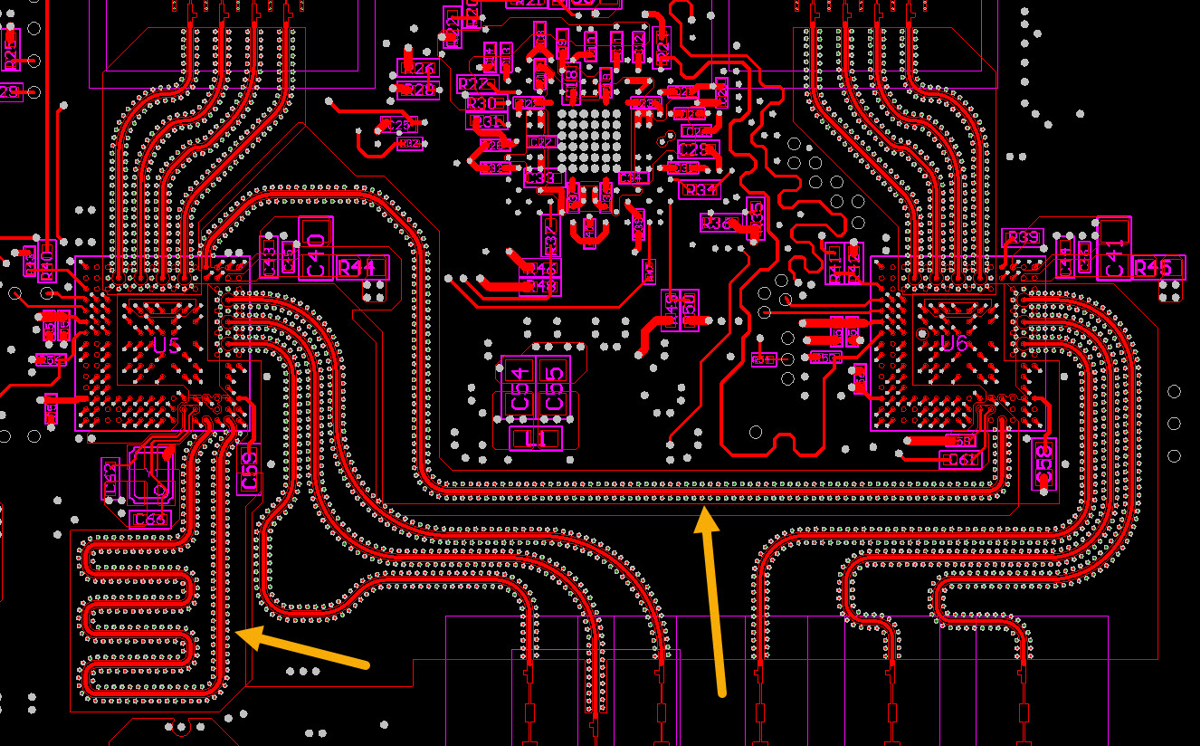

主器件 AWR2243 能够通过两个不同的延迟匹配放大器,在两个不同的输出引脚上提供共享的 LO 信号。FM_CW_CLKOUT 和 FM_CW_SYNCOUT 中的任何一个或全部都可以用作从主器件到辅助器件的 LO 源。为了避免这两个器件中使用的 LO 信号之间出现偏差,输入主器件的 LO 信号输入需要通过与主器件和辅助器件之间布线长度匹配的布线。如图 5-2 所示,一个 LO 信号输出会通过一条迹线在器件之间进行路由。然后,来自主器件的另一个输出 LO 信号使用长度相同的迹线环回到主器件上的 LO 信号输入。

图 5-1 LO 时钟信号

图 5-1 LO 时钟信号 图 5-2 LO 时钟路由

图 5-2 LO 时钟路由