ZHCUAT1A February 2022 – July 2022

6.3 使用输入页面

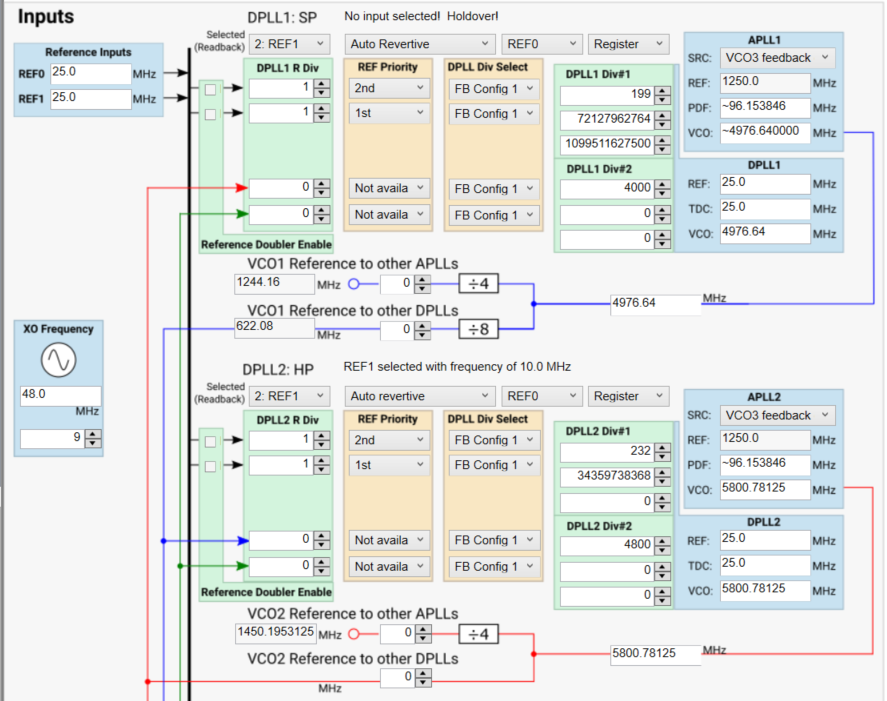

“Input”页面提供器件所有输入、APLL 频率和 DPLL 频率的概览视图。

运行开始页面第 7 步中的脚本来计算 DPLL 分频器和环路滤波器时,此页面显示设置 DPLL 频率的 DPLL 分频器值。此处显示的 DPLL 频率正是所需的确切频率。

每个 DPLL 支持两组 DPLL 分频器,可供选择。此时,该工具仅计算“FB Config 1”的分频器。要使用两个不同的反馈分频器,应按以下过程操作:

Div #1 的设置可复制到 Div #2,并选择供 DPLL Div Select 控件使用。

需要 Div #2 设置的基准应设置为“FB Config 2”。

可以运行第二次计算(重新运行脚本,即 DPLL 开始页面上的第 7 步),将使用“FB Config 1”的新值重新填充 Div #1 设置。

Div #2 设置将与第 1 步中最初复制的设置保持相同。

使用两个反馈分频器时,不要求 TDC 速率完全相同,只要求两个 DPLL 反馈配置的 TDC 速率差在 ±5% 以内即可。

图 6-9 APLL 或 DPLL 频率选择.

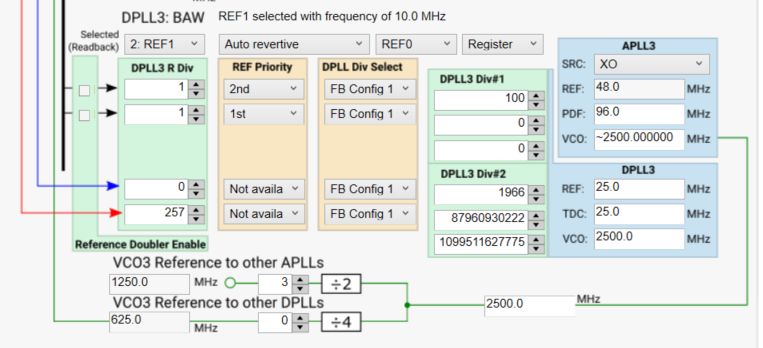

图 6-9 APLL 或 DPLL 频率选择.  图 6-10 PLL3 输入.

图 6-10 PLL3 输入.