ZHCUAV5A September 2022 – March 2023 TPSM33625

6 布局

TPSM33625EVM 和 TPSM3365FEVM 的顶部丝印(即 J4)不同,这是各层图(无布线)之间的唯一区别。

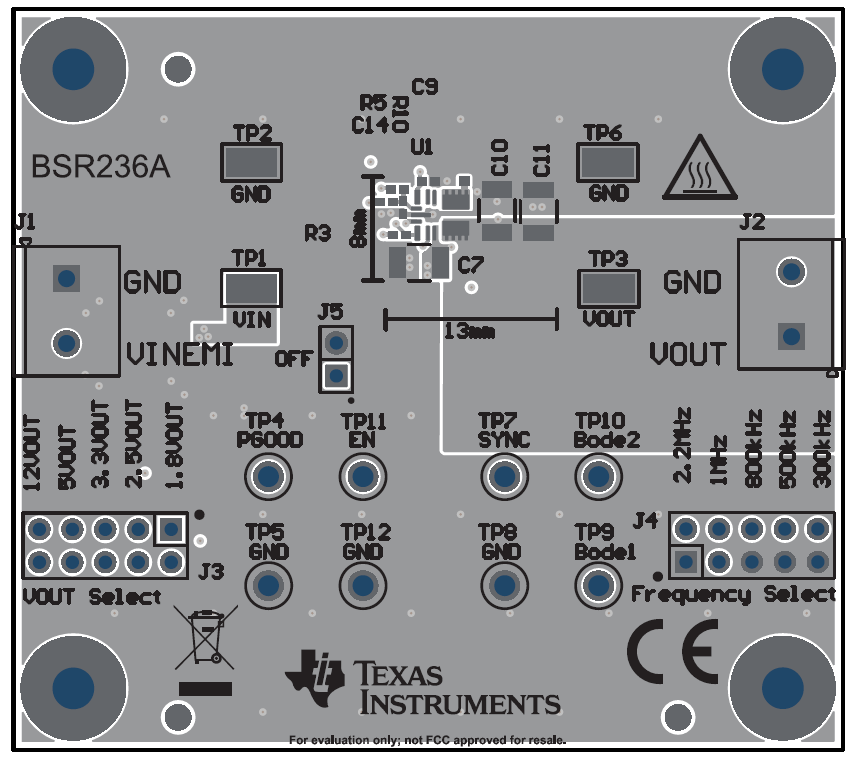

图 6-1 PCB 顶层 2D (TPSM33625EVM)

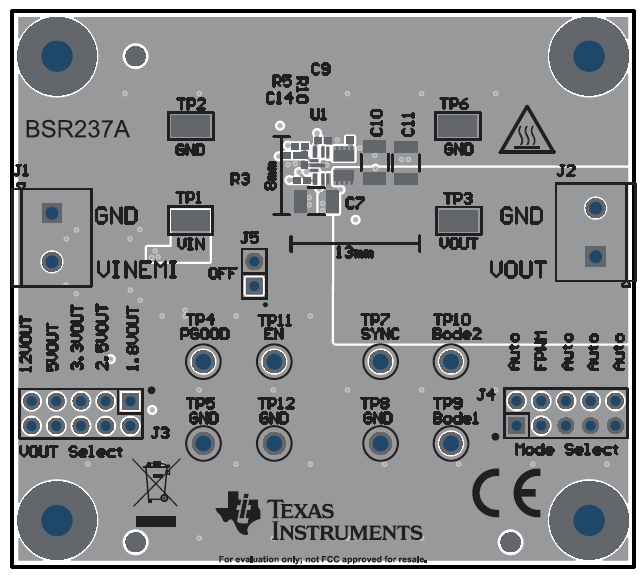

图 6-1 PCB 顶层 2D (TPSM33625EVM) 图 6-2 PCB 顶层 2D (TPSM33625FEVM)

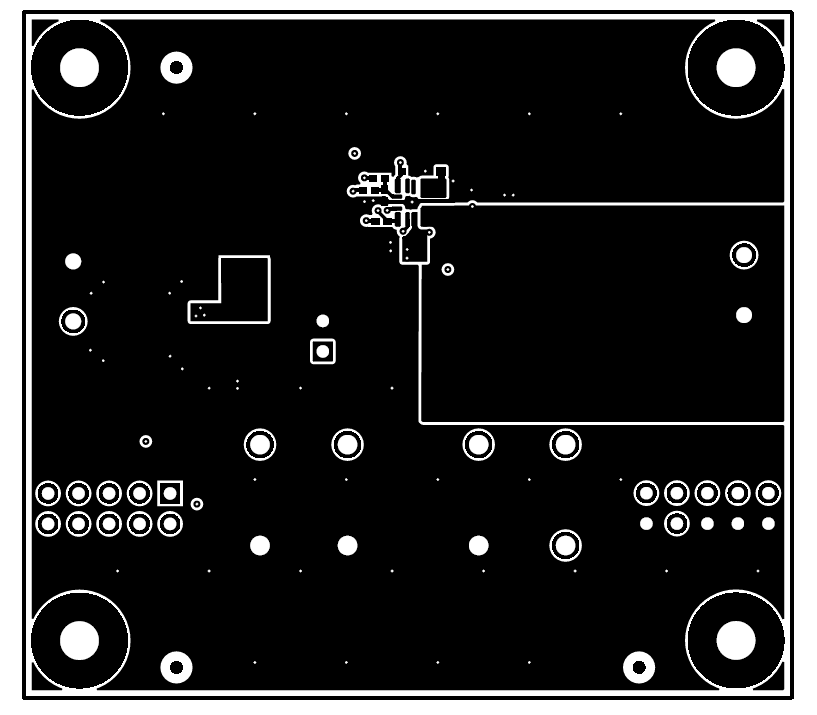

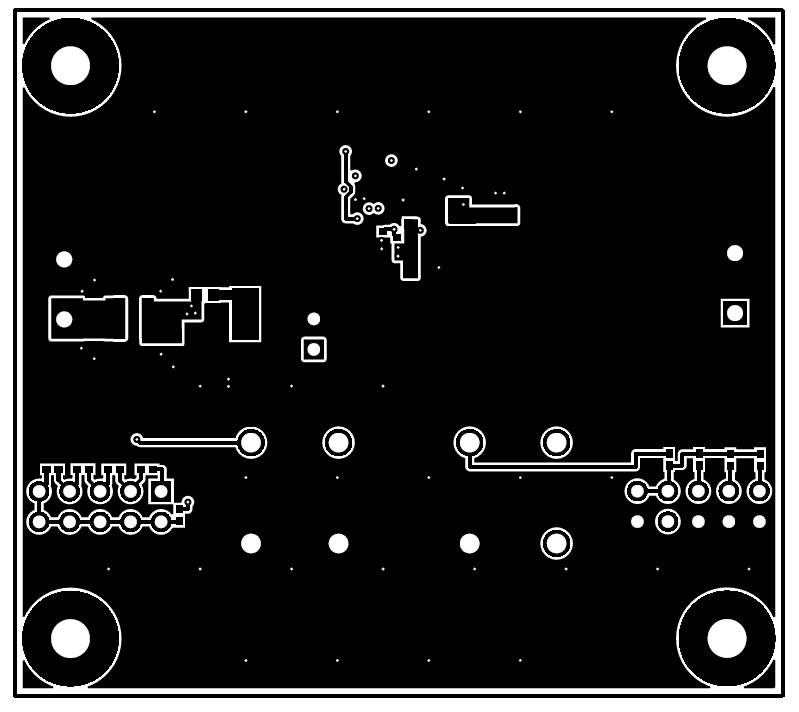

图 6-2 PCB 顶层 2D (TPSM33625FEVM) 图 6-3 PCB 底层 2D

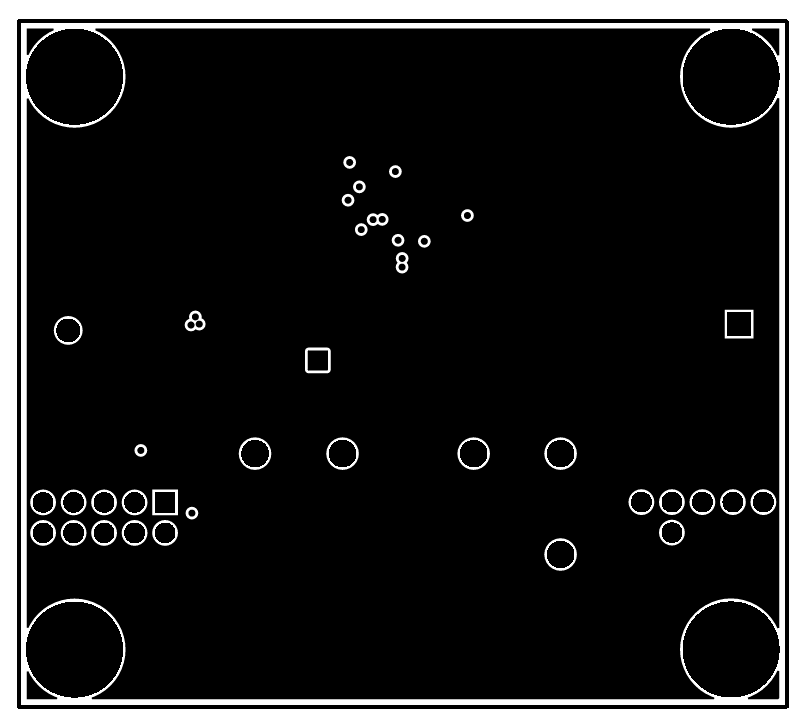

图 6-3 PCB 底层 2D 图 6-4 顶层

图 6-4 顶层保留用作实心接地层,用于实现低噪声和优化的热设计。

图 6-5 中间层 1

图 6-5 中间层 1主布线层

图 6-6 中间层 2

图 6-6 中间层 2保留用于放置 π 型滤波器和非关键无源器件(不包括输入电容器)。由于输入电容器提供较低的输入环路电感,因此将其放置在 PCB 底部。单层实现也符合要求。

图 6-7 底层

图 6-7 底层