ZHCUAW7C October 2016 – July 2024 DLP650LNIR , DLPC410

- 1

- 说明

- 特性

- 4

- 1评估模块概述

-

2硬件

- 2.1 主要元件

- 2.2

硬件概览和设置

- 2.2.1 入门

- 2.2.2

用户连接器和 I/O

- 2.2.2.1 J12 输入电源连接器

- 2.2.2.2 J18 输入电源连接器

- 2.2.2.3 J1 USB 连接器引脚分配

- 2.2.2.4 J3 USB GPIO

- 2.2.2.5 J6 GPIO_A 连接器

- 2.2.2.6 J8 DLPC410 Mictor 连接器

- 2.2.2.7 J9 USB/APPSFPGA Mictor 连接器

- 2.2.2.8 J13 DMD Flex 1 连接器

- 2.2.2.9 J14 DMD Flex 2 连接器

- 2.2.2.10 J15 - DDR2 SODIMM 连接器

- 2.2.2.11 J16、J17 EXP 连接器

- 2.2.2.12 H1 Xilinx FPGA JTAG 接头

- 2.2.3 配置跳线

- 2.2.4 开关

- 2.2.5 电源和状态 LED

- 2.2.6 测试点

- 3软件

- 4硬件设计文件

- 5其他信息

- 6相关文档

- 7修订历史记录

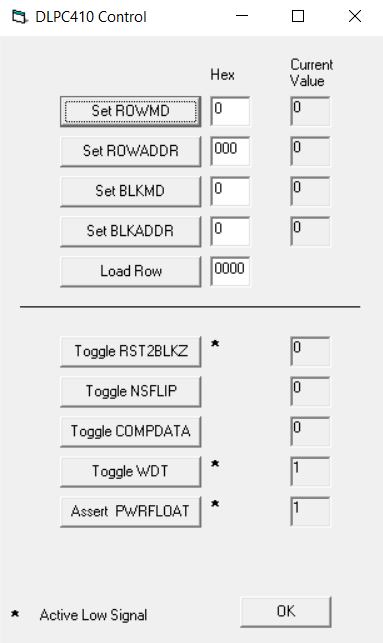

3.5 DLPC410 控制窗口

“DLPC410 Control”窗口通过“DMD/DLPC410 Control”菜单访问,并提供对 DLPC410 输入信号的直接控制。点击设置按钮时,不会生成脚本命令,而会立即对 DLPC410 施加控制。

该窗口的上部支持读取和设置用于向 DMD 写入数据的 DLPC410 信号。ROWMD(行模式)、ROWADDR(行地址)、BLKMD(块模式)和 BLKADDR(块地址)的当前值显示在“Current Value”列中。当在“Hex”列中以十六进制形式输入新的值并点击设置按钮时,值便会发送到 DLPC410。“Load Row”按钮会发送一行,其中包含输入的 4 位十六进制值的重复值。

该窗口的下部支持控制 DLPC410 输入信号,这些输入信号都是控制工作模式。点击按钮可切换信号的当前值。

注意:将 PWRFLOAT(功率浮点)置为有效将停止 DMD 镜像。恢复需要通过将 APPS_LOGIC_RST(硬件开关 SW2)置为有效或对 EVM 进行下电上电来复位 APPSFPGA,从而再次重新启动 D4100 系统。

有关 DLPC410 输入信号的详细信息,请参阅 DLPC410 数据表 (DLPS024)。

有关此“DMD/DLPC410 Control”菜单页面上各个按钮调用的 ActiveX 函数的详细信息,请参阅“DLP Discovery 4100 开发平台 API 编程人员指南”(DLPU039)。

图 3-29 DLPC410 控制窗口

图 3-29 DLPC410 控制窗口