ZHCUBE3A October 2023 – March 2024 DLPC964

- 1

- 说明

- 开始使用

- 特性

- 应用

- 6

- 1评估模块概述

-

2硬件

- 2.1 DLPLCRC964EVM 电源要求

- 2.2

DLPLCRC964EVM 连接

- 2.2.1 J1、J2 - HPC FMC 连接器(公头)

- 2.2.2 J3 - 输入电源

- 2.2.3 J4 - TestMux 连接器

- 2.2.4 J6、J8 - I2C 地址选择器

- 2.2.5 J7 - JTAG 边界扫描

- 2.2.6 J9 - Micro-B USB 连接器

- 2.2.7 J10 - I2C 连接器

- 2.2.8 J11 - 3.3V GPIO 连接器

- 2.2.9 J12 - 1.8V GPIO 连接器

- 2.2.10 J13、J14、J15、J16 - DMD EVM 板柔性电缆连接器

- 2.2.11 J17 - DMD_DMux 连接器

- 2.2.12 J18 - FanSink 连接器

- 2.2.13 开关

- 2.2.14 DLP LightCrafter DLPC964 LED

- 2.3 EVM 组装

- 2.4 快速入门

- 3软件

- 4硬件设计文件

- 5其他信息

- 6米6体育平台手机版_好二三四 (TI) 相关文档

- 7修订历史记录

3.1.4.4.5 图形设置 (Apps)

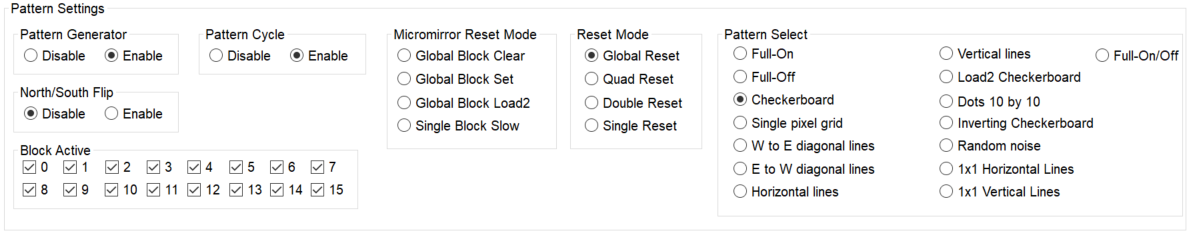

图 3-17 Apps FPGA 图形设置

图 3-17 Apps FPGA 图形设置- Pattern Generator - 如果启用,图形会显示在 DMD 上。如果禁用,DMD 上不会显示任何图形。

- Pattern Cycle - 如果启用,DMD 会循环使用前 8 个预定义的图形,每个图形显示 2 秒。如果禁用,系统会将选择的单个图形发送到 DMD。

- North/South Flip - 如果启用此设置,系统会垂直翻转 DMD 上显示的图形。

- Pattern Select

- Full-On - 全白背景,其中 DMD 上的所有微镜都将处于打开位置。

- Full-Off - 全黑背景,其中 DMD 上的所有微镜都将处于关闭位置。

- Checkerboard - 黑白棋盘(64 x 64 像素)。

- Single pixel grid - 边框处于开启状态,有助于显示 DMD 阵列的范围。

- W to E diagonal lines - 用于检查是否有行数据问题。

- E to W diagonal lines - 用于检查是否有行数据问题。

- Horizontal lines - 用于检查行加载是否有问题。

- Vertical lines - 用于检查数据总线是否有问题。

- Load2 Checkboard - 黑白棋盘图形(32 x 32 像素)。

- Dots 10 by 10 - 单个白色像素在 X 和 Y 方向上均匀间隔 10 个像素。

- Inverting Checkerboard - 棋盘图形的反转版本。

- Random Noise - 用于客户倾斜角测试的随机噪声图形。

- 1x1 Horizontal Lines(每隔一行黑/白交替)- 用于检查行加载是否有问题。

- 1x1 Vertical lines(每隔一列黑/白交替)- 用于检查数据总线是否有问题。

- Full-On/Off - 在全开和全关模式之间切换。

- Micromirror Reset Mode

- Global Block Clear - 该模式会显示 DLPC964 系统中如何使用清除块加载类型。清除加载类型不需要任何数据,因为该块会将所有微镜置于关闭状态 (0)。由于清除加载类型无需发送任何数据,因此无需发送命令有效信号,而仅发送 DMD 加载信号。MCP_Start 信号遵循与全局模式相同的图形。

- Global Block Set - 该模式会显示 DLPC964 系统中如何使用设置块加载类型。设置加载类型与清除加载类型的作用刚好相反,也不需要任何数据。设置加载类型会将所有微镜设置为开启状态 (1)。与清除加载类型一样,无需命令有效信号,只需 DMD 加载信号。MCP_Start 信号遵循与全局模式相同的图形。

- Global Block Load2 - 启用 Load2 操作会指示 DMD 将接收到的 1 行数据加载到 DMD 的 2 行中。DLPC964 Apps FPGA 在 Load2 操作期间的作用是,验证是否最多有 68 条线路通过 Aurora HSSI 通道发送。将 LOAD2 置为有效会使 DLPC964 控制器和连接的 DMD 针对所发送的每行数据加载 2 行,从而将图形加载时间缩短为完整 DMD 加载的一半。此功能不会缩短 MCP 时间。

- Single Block Slow - 慢速模式(或禁用快速模式)会使 DLPC964 Apps FPGA 仅通过单个 Aurora 64B/66B 通道(4 个 10Gbps 信道,而不是 12 个)发送数据。为此,必须在 1 个通道上按顺序发送块的每个段,而不是并行发送。这些数据段必须按以下顺序发送:D (0x3) C (0x2) B (0x1) A (0x0)。一旦四个段都发送完毕,即可发出 MCP_Start 信号。MCP_Start 信号的行为与单模式中的行为相同。

- Block Active - DLP991U DMD 中有 16 个块 [0-15]。在 GUI 内选中的块将决定要复位哪些块并将新数据加载到 DMD。