ZHCUBE8 September 2023 AFE7769D

4 启动步骤

以下部分从启动的角度分步介绍了参考设计的设置,以及整个过程的相关屏幕截图。

步骤:

- 首先,为 Agilex eSOM7 TI 载板上电,然后为 TI AFE7769DEVM 上电。

- 打开 Teraterm,点击“Serial”,然后点击“OK”。

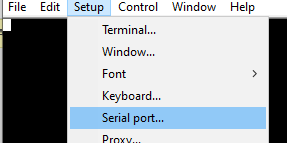

- 依次点击“Setup > Serial port”,请参阅图 4-1。

图 4-1 打开 Teraterm 中的串行端口窗口

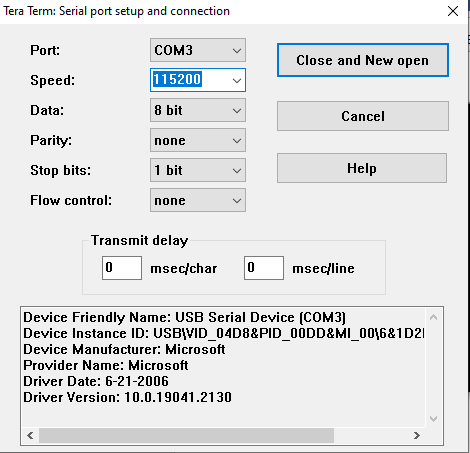

图 4-1 打开 Teraterm 中的串行端口窗口 - 此时将显示一个新窗口。选择连接 eSOM7 的 COM 端口(不是 COM1)。将速度更改为“115200”,然后点击“Close and New open”,请参阅图 4-2。

图 4-2 串行端口设置和连接

图 4-2 串行端口设置和连接 - 您现在应该会看到“agilex login:”,如果您没有看到任何文本,请按 Enter 键,屏幕上将出现“agilex login”。

- 键入 root 并按 Enter 键登录。

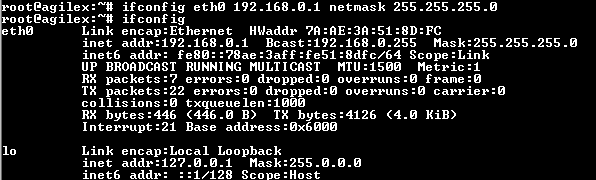

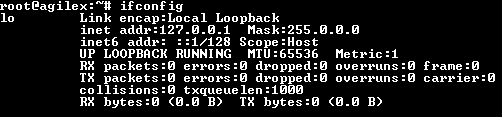

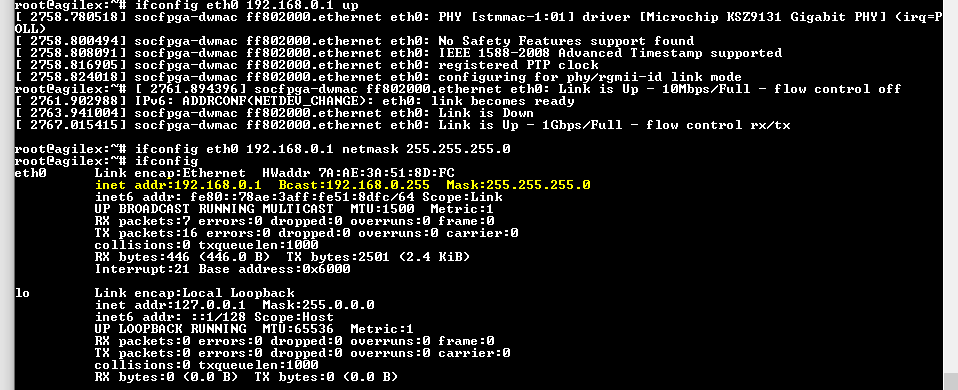

- 使用 ifconfig 命令获取 Arm 节点的 IP 地址。如果在 eth0 接口下看不到“inet4”IP 地址,请使用命令 ifconfig eth0 192.168.0.1 netmask 255.255.255.0 为 eth0 接口分配 192.168.0.1 IP 地址,请参阅图 4-3。

图 4-3 IP 地址获取

图 4-3 IP 地址获取 - 在 PowerShell 上,使用 cd < Hitek RF INTF release archive path> 命令将您的目录移至 Hitek RF INTF 版本归档。在我们的设置中,命令为 cd C:\Users\a0503061\Documents\Hitek\AG_eSOM_AFE77XX_RF_INTF_DEMO_Release_v3_3_2023-04-2 5。

- 使用 scp -r software/arm_ag/tools/ root@192.168.0.1:~/jesd_tools/ 命令将 software/arm_ag_/tools 文件夹从 AG_eSOM_AFE77XX_RF_INTF_DEMO_Release_v3_3_2023-04-25 文件夹复制到文件夹名为“jesd_tools”的 Arm 节点。

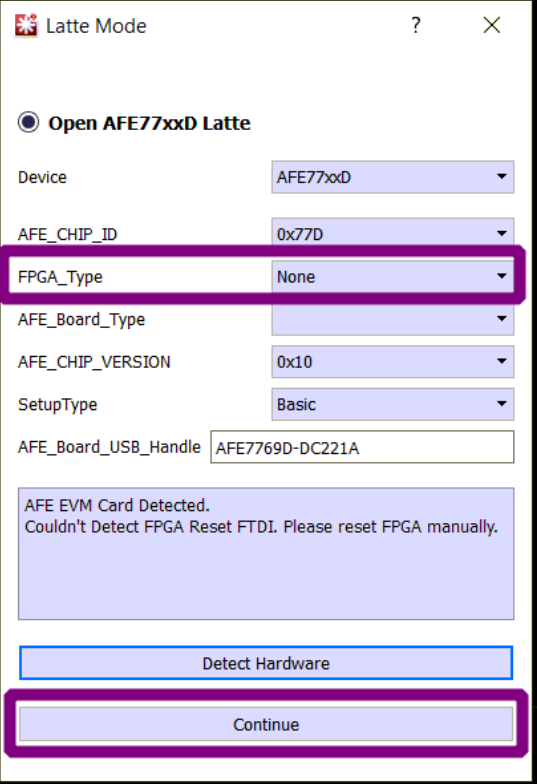

- 启动 TI AFE77xxD Latte GUI 软件,在标题为“Latte Mode”的第一个对话框窗口中,确保“FPGA_Type”设置为“None”,并显示“AFE EVM Card Detected”消息。应该会显示“Couldn't Detect FPGA Reset FTDI.Reset FPGA manually”。然后按“Continue”按钮打开 Latte 主 GUI。要正确导航到“Latte Mode”窗口,请参阅图 4-4。

图 4-4 启动 AFE77xxD Latte GUI

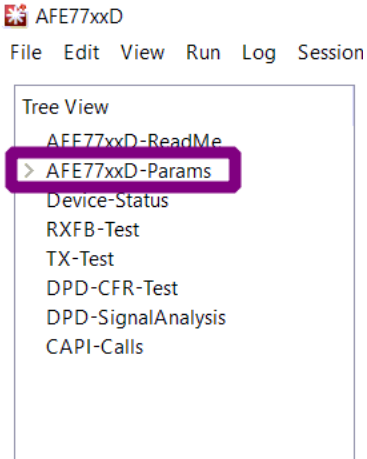

图 4-4 启动 AFE77xxD Latte GUI - 在 Latte 软件完成初始化步骤后,点击软件窗口左面板上的“AFE77xxD-Params”,转到“AFE77xxD Params”选项卡。图 4-5 显示了如何导航到软件面板上的相应选项卡。

图 4-5 导航至 AFE77xxD-Params

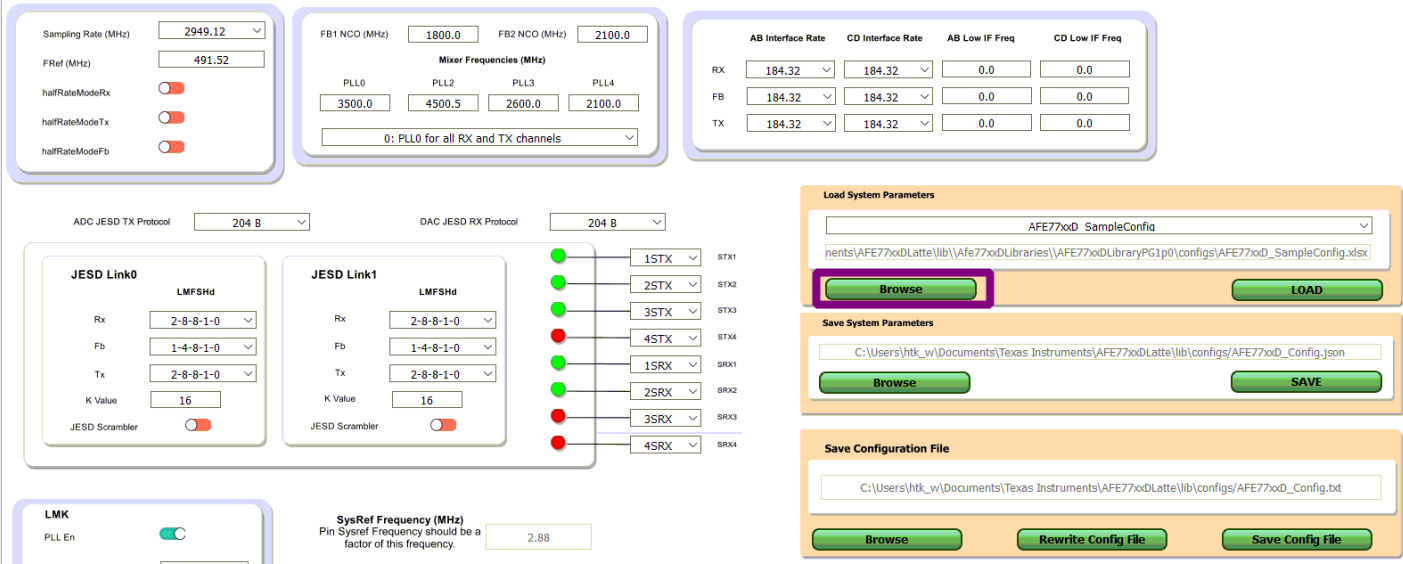

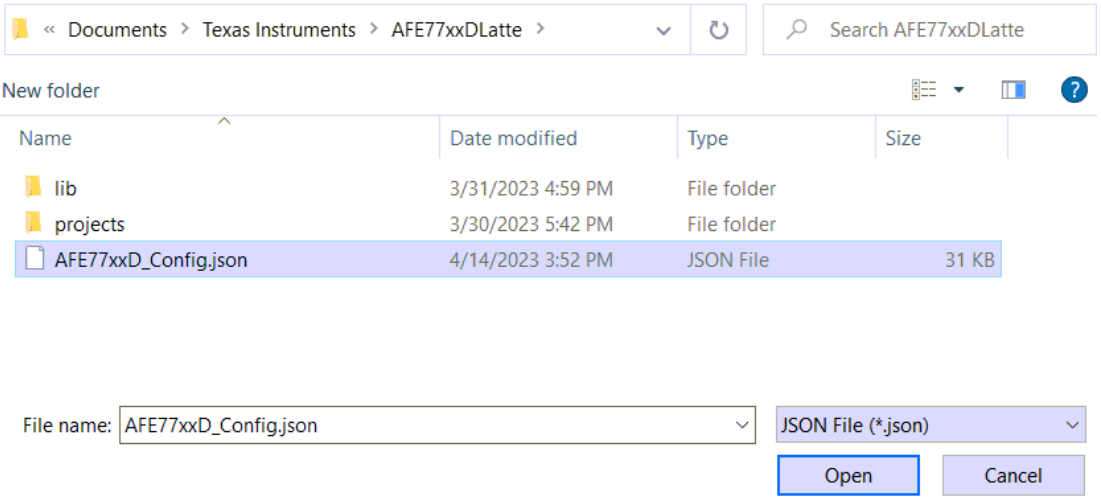

图 4-5 导航至 AFE77xxD-Params - 在“Load System Parameters”框中,点击“Browse”以搜索 AG_eSOM_AFE77XX_RF_INTF_DEMO_Release_v3_3_2023-04-25\software\x64_64\utilities\AFE77xxDLatte_v0p4 中提供的 AFE77xxD_Config.json 配置文件,并将其打开。有关“AFE77xxD-Params”显示视图以及如何加载该文件,请分别参阅图 4-6 和图 4-7。

图 4-6 AFE77xxD-Params 显示视图

图 4-6 AFE77xxD-Params 显示视图 图 4-7 将 AFE77xxD 配置文件加载到 Latte

图 4-7 将 AFE77xxD 配置文件加载到 Latte - 选择配置文件后,请点击“LOAD”按钮将此配置加载到 GUI 中。GUI 应更改为所需配置,以便能够与 Agilex FPGA 中的 JESD IP 建立 JESD 链路。

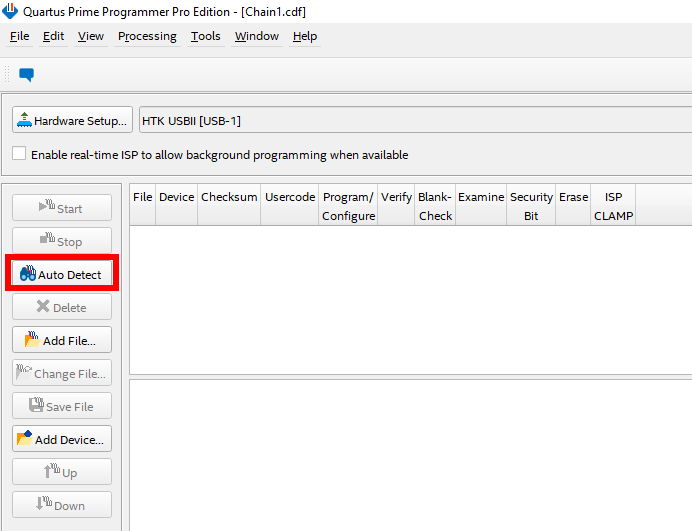

- 打开 Quartus Prime Programmer 并点击“Auto Detect”按钮。有关如何导航至相应功能的信息,请参阅图 4-8。如果这是 eSOM7 首次连接到 PC,而“Auto Detect”按钮为灰色,请点击“Hardware Setup...”按钮,在“Currently selected hardware”旁边的下拉菜单中选择“HTK USBII”,然后检查“Hardware frequency”是否设置为 24000000Hz。

图 4-8 Quartus Prime Programmer 中的自动检测

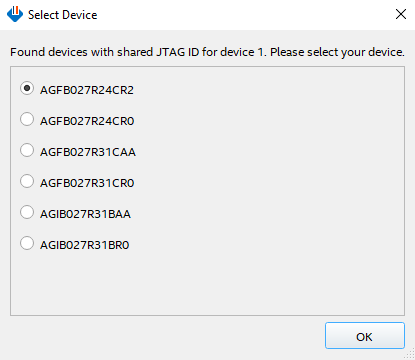

图 4-8 Quartus Prime Programmer 中的自动检测 - 点击“Auto Detect”后,将出现一个窗口;选择“AGFB027R24CR2”选项并点击“OK”。图 4-9 显示了选择器件时的典型视图。

图 4-9 器件选择

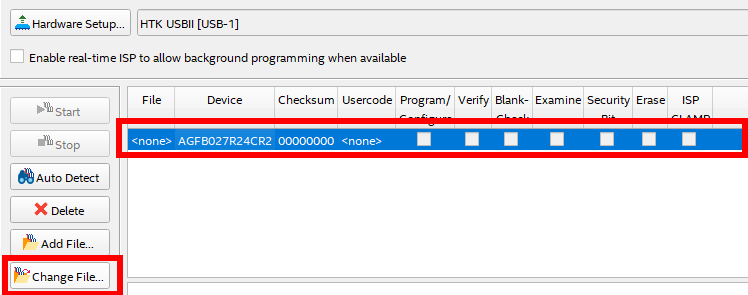

图 4-9 器件选择 - 选择“File”下的唯一行,然后点击“Change File”。选择 AG_eSOM_AFE77XX_RF_INTF_DEMO_Release_v3_3_2023-04-25\snapshots\hardware\fpga\agfb027_r24c_asyXX\ag_esom_top_afe77xx_jesd204c_4t4r2f_fpga_first_20230421_012455 目录中提供的名为 ag_esom_top_afe77xx_jesd204c_4t4r2f_fpga_first_hps_auto.sof 的 FPGA 图像,其中“XX”应与 eSOM7 板上的“ASY-XX-00047”标签匹配。压缩的 .tar.gz 文件夹中有这些文件的额外副本。图 4-10 显示了如何导航至适当的功能。

图 4-10 文件更改

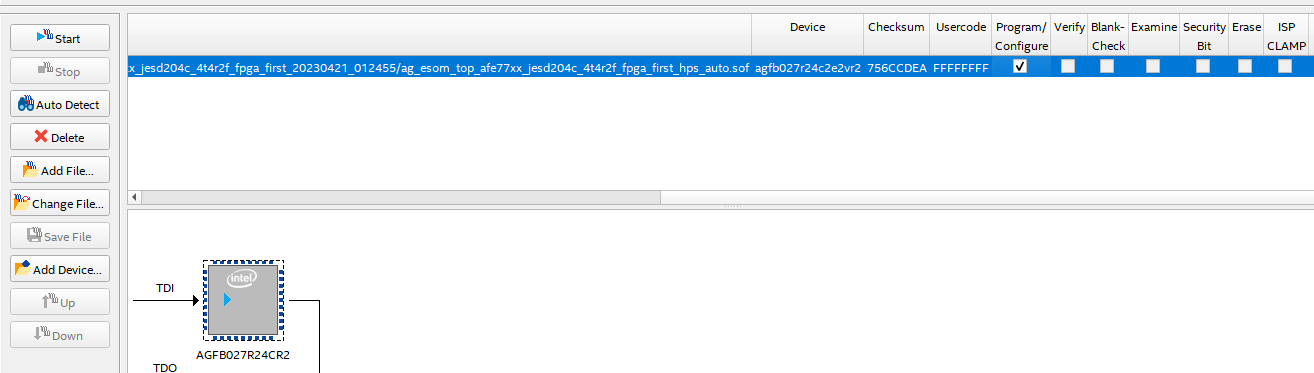

图 4-10 文件更改 - 接下来,选中“Program/Configure”下的框,请参阅图 4-11。

图 4-11 程序/配置

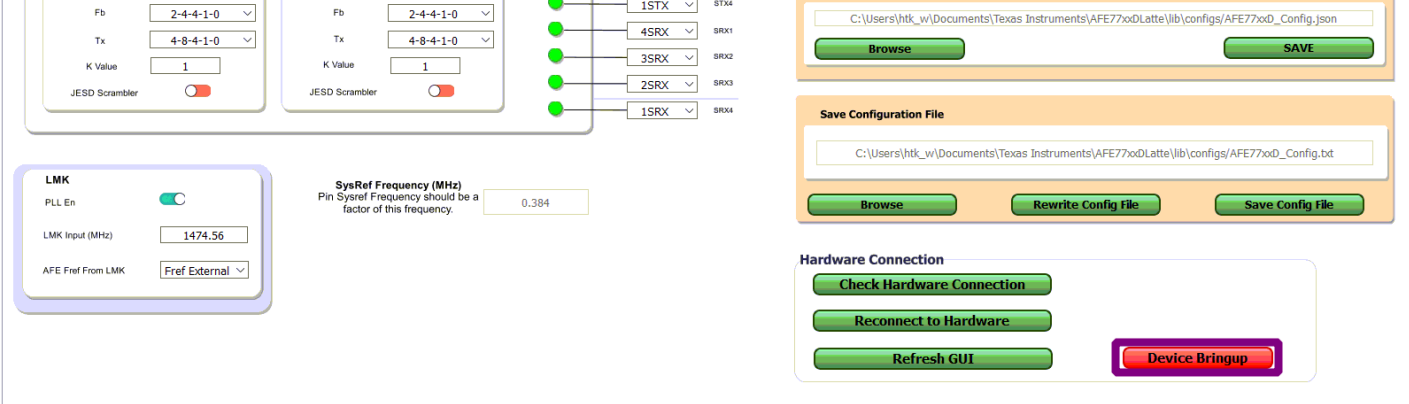

图 4-11 程序/配置 - 在 AFE77xxD GUI 上,应点击“AFE77xxD-Params”页面底部的“Device Bringup”按钮,开始配置 LMK04828 和 AFE7769D 芯片。图 4-12 显示了如何导航至相应的按钮。

图 4-12 器件启动,AFE77xxD-Params

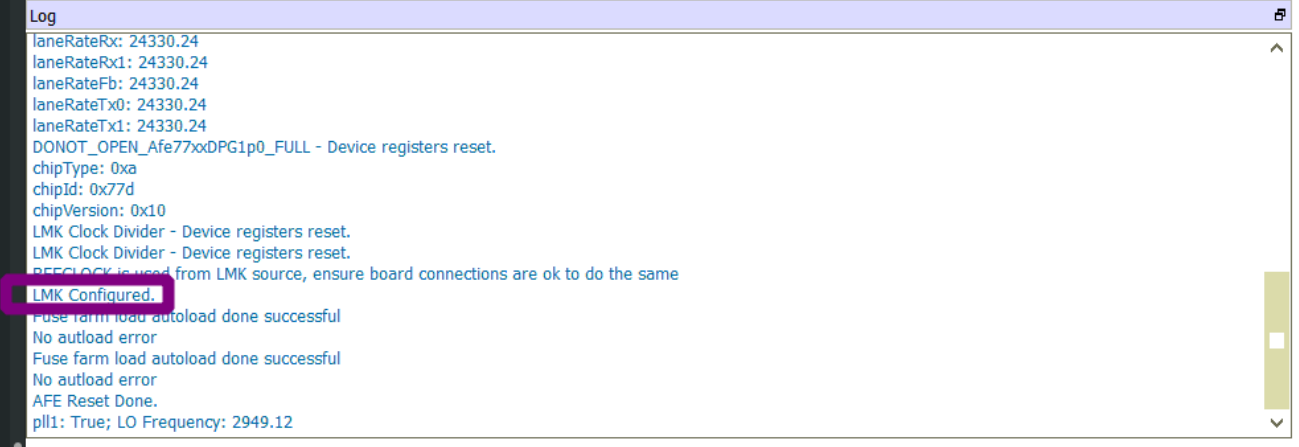

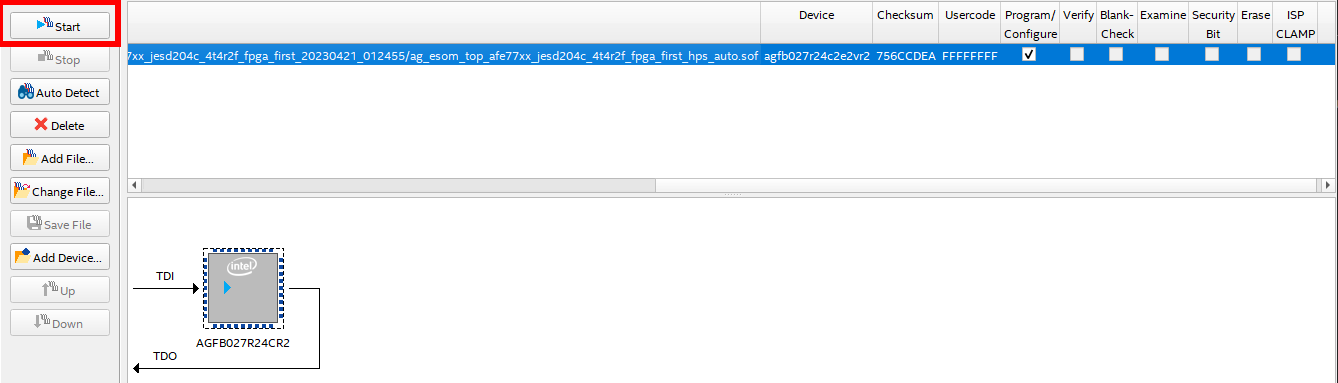

图 4-12 器件启动,AFE77xxD-Params - TI AFE77xxD Latte 软件日志窗口中出现“LMK Configured”消息后,说明 LMK04828 芯片配置完成,通过点击 Quartus Prime Programmer 上的“Start”按钮,对 Agilex FPGA 图像进行编程。图 4-13 和图 4-14 提供了器件编程步骤的直观参考。

图 4-13 在 AFE77xxD Latte GUI 中确认 LMK 配置

图 4-13 在 AFE77xxD Latte GUI 中确认 LMK 配置 图 4-14 点击开始按钮对 Agilex FPGA 进行编程

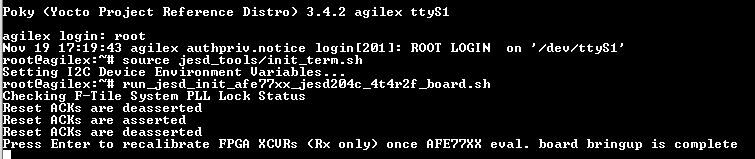

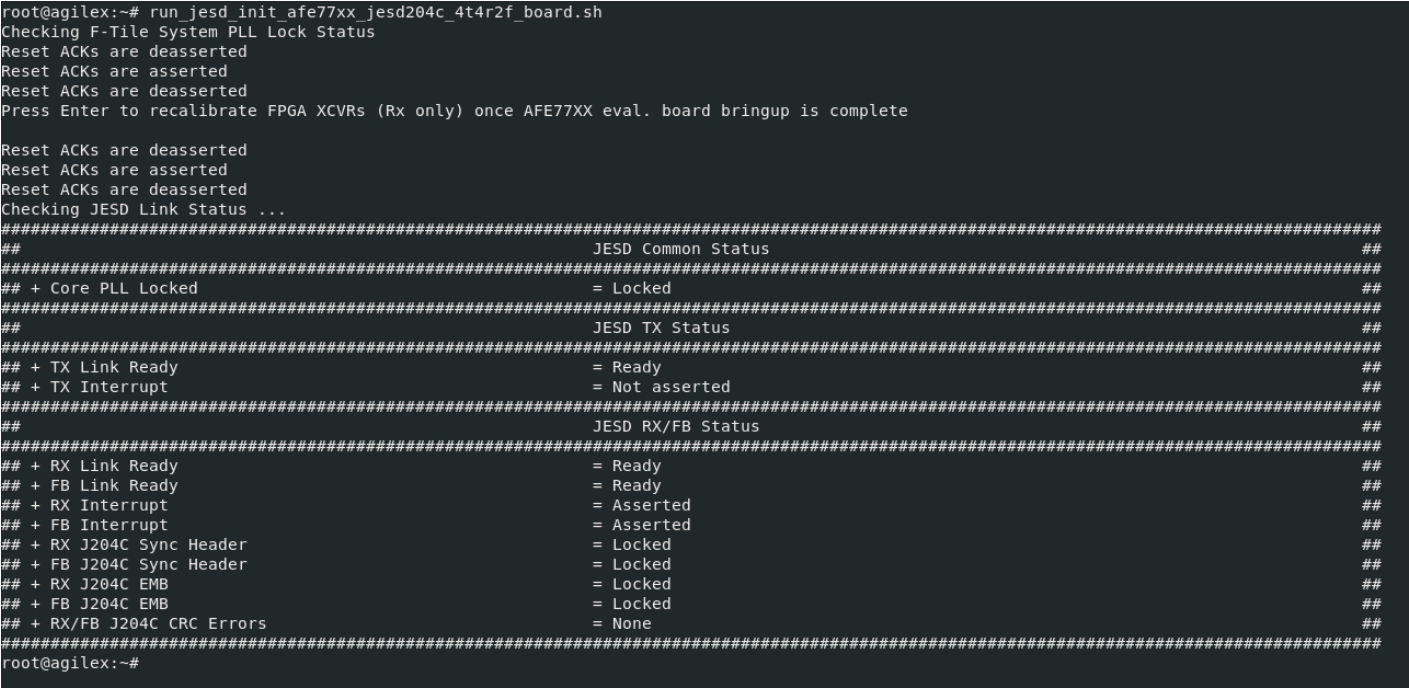

图 4-14 点击开始按钮对 Agilex FPGA 进行编程 - 等待 Arm 节点的 Linux 引导显示在 Teraterm 控制台上,并使用 root 用户名登录。然后,使用命令 source jesd_tools/init_term.sh 执行 jesd_tools 文件夹中的 init_term.sh 脚本,然后运行 Arm 节点上的 run_jesd_init_afe77xx_jesd204c_4t4r2f_board.sh 脚本。先不要按 Enter 键。图 4-15 显示了一个示例代码块。

图 4-15 在 Agilex FPGA 中初始化 JESD IP

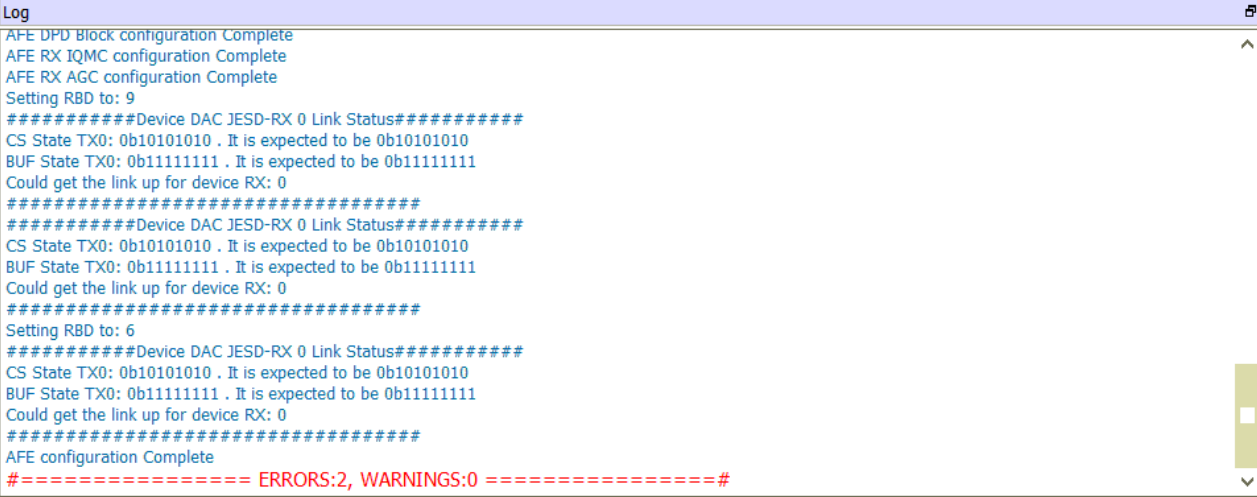

图 4-15 在 Agilex FPGA 中初始化 JESD IP - 等到 TI AFE77xxD Latte 软件中的 AFE7769D 配置完成,它应该会在“Log”窗口中报告 AFE7769D 芯片上的 JESD204C 链路成功(请注意,预计会出现与 FPGA 复位故障相关的 2 个错误)。图 4-16 显示了“Log”窗口,其中显示了器件能够为器件的 JESD RX 接通链路。

图 4-16 AFE 配置完成说明器件 JESD RX 的链路接通

图 4-16 AFE 配置完成说明器件 JESD RX 的链路接通 - 在 TI AFE77xxD Latte 软件中完成 AFE7769D 配置后,在 Arm 节点 (Teraterm) 上按 Enter 键以重新校准 FPGA XCVR(仅限 Rx),从而完成 FPGA 上的 JESD204C 链路。图 4-17 显示了 FPGA 中的链路状态报告。

图 4-17 完成 JESD204C 链路并显示链路的状态报告

图 4-17 完成 JESD204C 链路并显示链路的状态报告 - 运行 ifconfig 命令查看 eth0 接口的 IP 地址。图 4-18 显示了一个示例代码块。

- 如果 eth0 接口与上图中的不符,请使用 ifconfig eth0 192.168.0.1 up 命令启动接口。然后,使用 ifconfig eth0 192.168.0.1 netmask 255.255.255.0 命令设置接口的 IP 地址

- 然后,您可以使用 ifconfig 命令检查该接口是否分配了 IP 地址,请参阅图 4-18 作为参考。

图 4-18 确认 eth0 接口有正确的 IP 地址

图 4-18 确认 eth0 接口有正确的 IP 地址

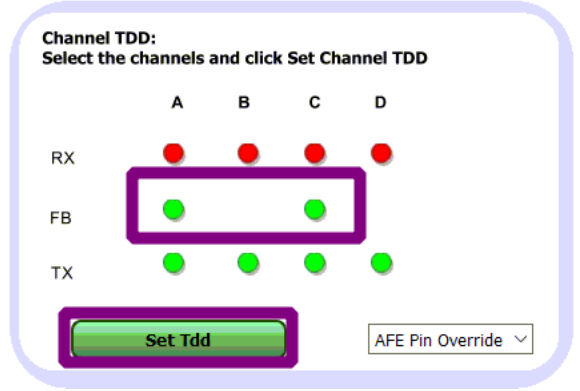

- 为了能够从 TX RF 端口输出信号以及从 RX 和 FB RF 端口输入信号,需要为所需的被测通道设置“Channel TDD”。为此,请点击软件窗口左侧的“RXFB-Test”,转到 AFE77xxD GUI 中的“RXFB-Test”页面。在此页面的“Channel TDD”框中,点击红点使其变为绿色,最后点击“Set Tdd”按钮,请参阅图 4-20。

图 4-20 TX 到 RX 测试的 TDD 配置

图 4-20 TX 到 RX 测试的 TDD 配置请注意,在测试 FB 通道时,不应设置 RX 通道的 TDD(因此,RX 通道的点不是绿色的),请参阅图 4-21。

图 4-21 TX 到 FB 测试的 TDD 配置

图 4-21 TX 到 FB 测试的 TDD 配置