ZHCUBI1 November 2023

3.1.2.2 输出

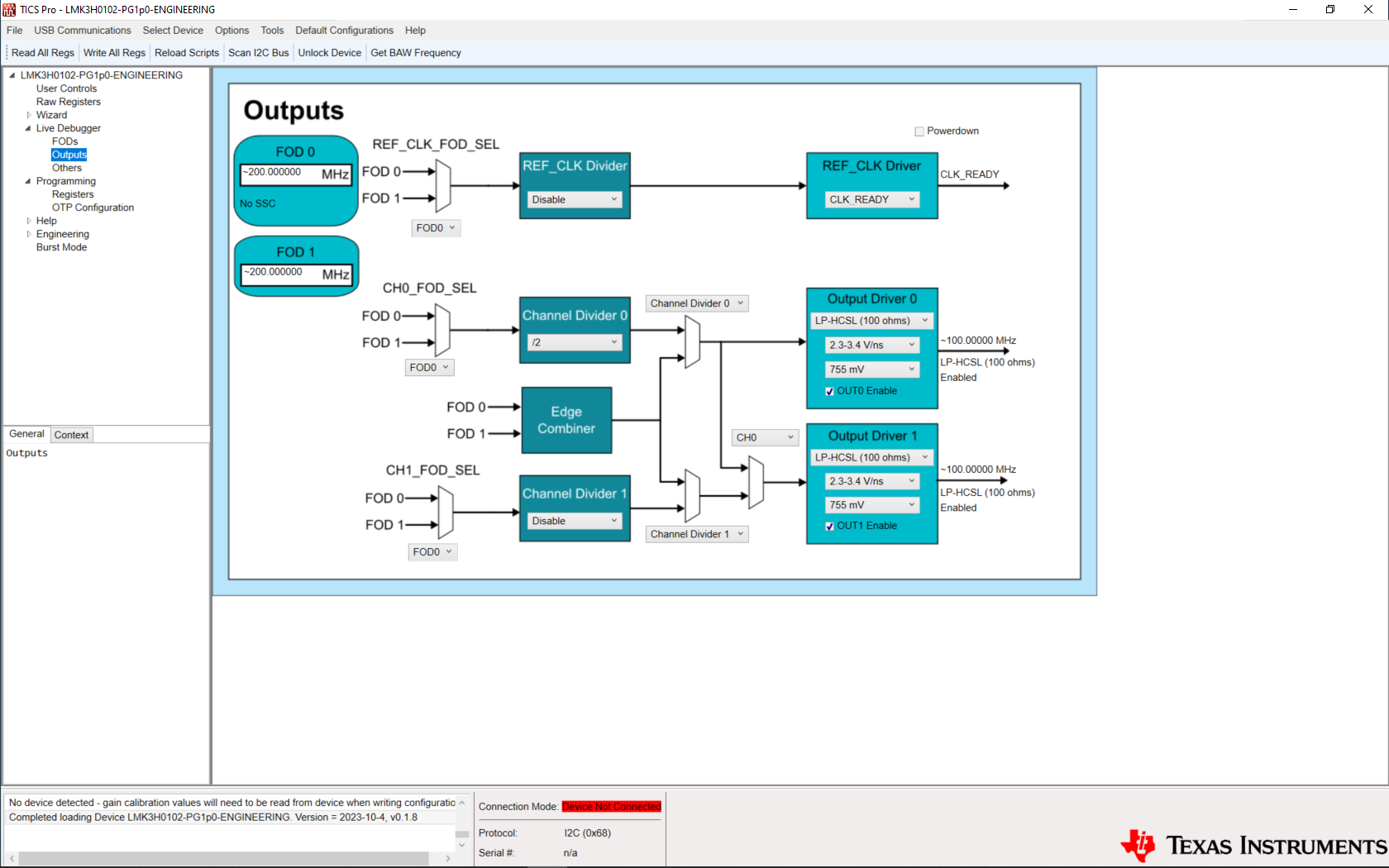

图 3-10 LMK3H0102“Outputs”页面

图 3-10 LMK3H0102“Outputs”页面利用 Outputs 页面,可以配置通道分频器和输出驱动器。在更改该页面中的任何设置之前,请点击 Powerdown 复选框,修改所需的设置,然后再次点击 Powerdown 复选框。任一通道分频器都可以由任一 FOD 驱动。每个输出驱动器都可以源自相应的通道分频器或边缘组合器。输出驱动器 1 可以源自任一通道分频器输出,如果 OUT0 和 OUT1 频率相同,则可以节省功耗。REF_CTRL 引脚可配置为 CLK_READY 信号、拉至低电平、高阻抗或源自任一 FOD 的附加 LVCMOS 时钟。

对于 LP-HCSL 输出,输出摆幅可根据应用要求在 625mV 和 950mV 之间调节。输出可以是交流耦合的,并用于模拟其他时钟格式(例如 LVPECL)的交流耦合版本。所有差分输出格式都具有可调节的压摆率控制。各个 LVCMOS 时钟输出可单独启用,可以同相或具有 180 度的相位差 - TI 建议除非提高性能需要,否则保持 P 和 N 输出异相。每个输出驱动器右侧的文本总结了输出频率、输出的使能状态和输出格式。