ZHCUBJ7 November 2023

4.4.2 相电压开关节点的传播延迟 PWM

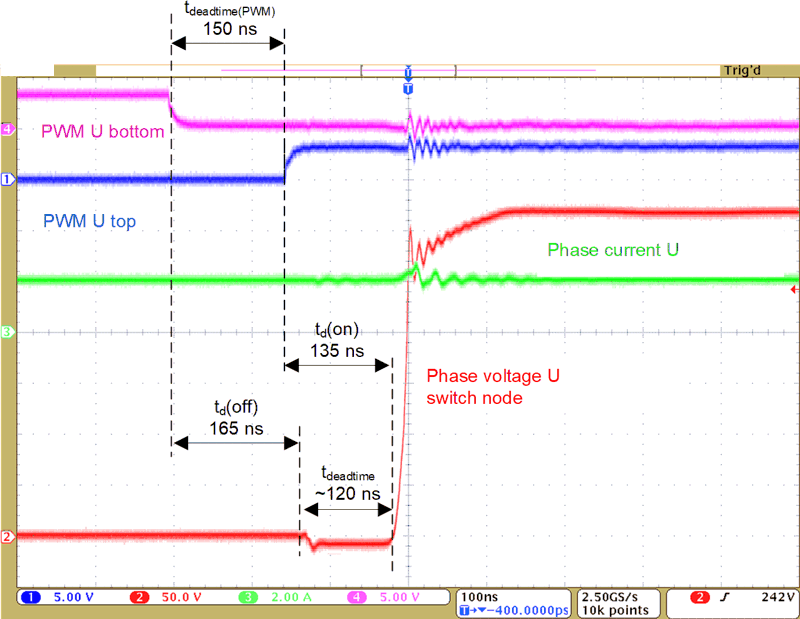

图 4-5 概述了从具有 150ns 死区时间的 MCU 互补 PWM 信号到 U 相开关节点的导通和关断传播延迟。当相电压 U 从 0V 变为约 –4V 时,可以确定底部 GaN-FET 的关断时间瞬间。然后,底部 FET 在第三象限模式下导通,其中漏源电压 VDS 约为 –4V,用虚线表示。有效关断延迟为 165ns。顶部 FET 的有效导通延迟(硬开关)约为 135ns。由于导通延迟和关断延迟的差异,有效死区时间为 120ns,如下所示。

图 4-5 PWM 导通和关断传播延迟

图 4-5 PWM 导通和关断传播延迟