ZHCUBK2 December 2023 AFE7728D , AFE7768D , AFE7769D

3.5 AFE7769D 编程方法 2:使用 GUI 模式

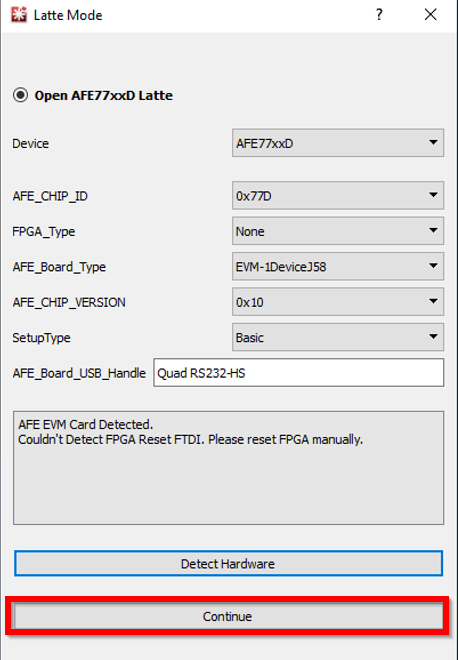

- 打开 AFE77xxD GUI 版本 0.4。确保其外观如图 3-8 所示,然后点击“Continue”。应该会显示“Couldn't Detect FPGA Reset FTDI.Please reset FPGA manually”消息,可以忽略该消息。

图 3-8 启动 AFE77xxD Latte 软件

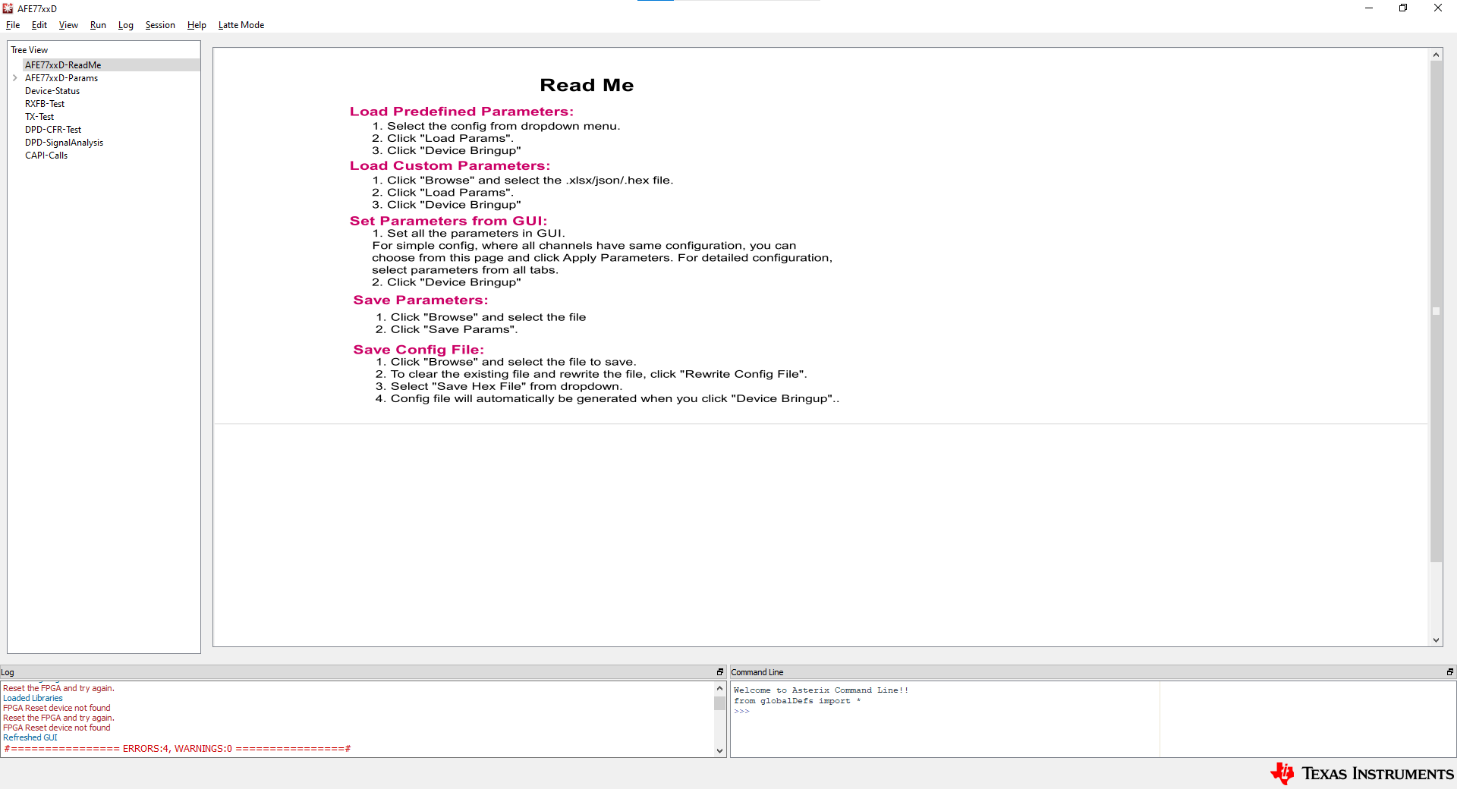

图 3-8 启动 AFE77xxD Latte 软件 - 等待 GUI 加载。它看起来如图 9 所示。点击左侧树形视图下方的“AFE77xxD-Device”选项卡,进入主参数屏幕。

图 3-9 自述文件 AFE77xxD Latte 软件

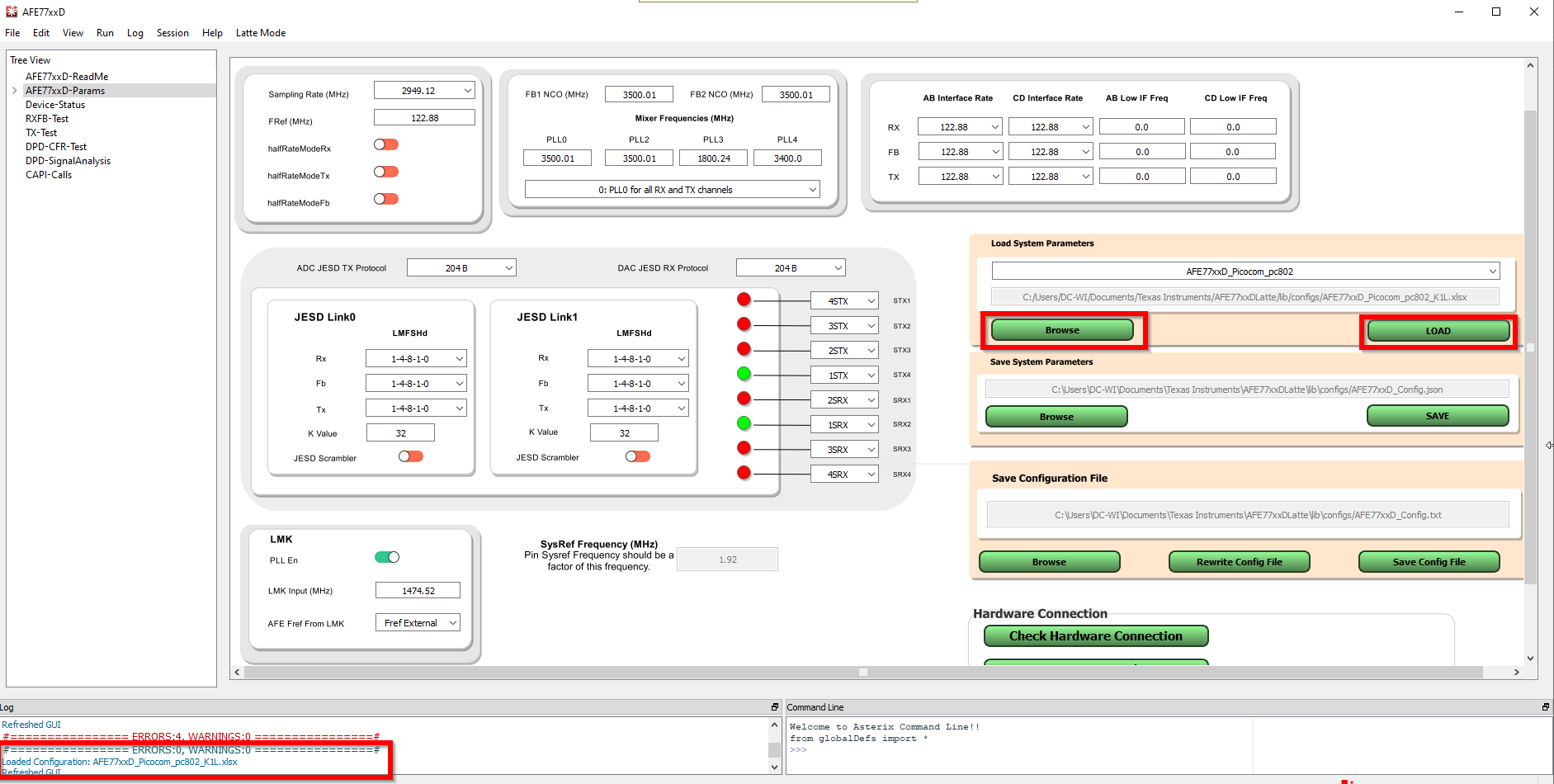

图 3-9 自述文件 AFE77xxD Latte 软件 - 点击“Load System Parameters”下的“Browse”,然后在“\Documents\Texas Instruments\AFE77xxDLatte\lib\configs”下选择“AFE77xxD_Picocom_pc802_K1L.xlsx”配置文件。选择该文件后,点击“LOAD”,屏幕应如图 3-10 所示。您还应该会看到一条消息,指出配置已加载到日志窗口中。

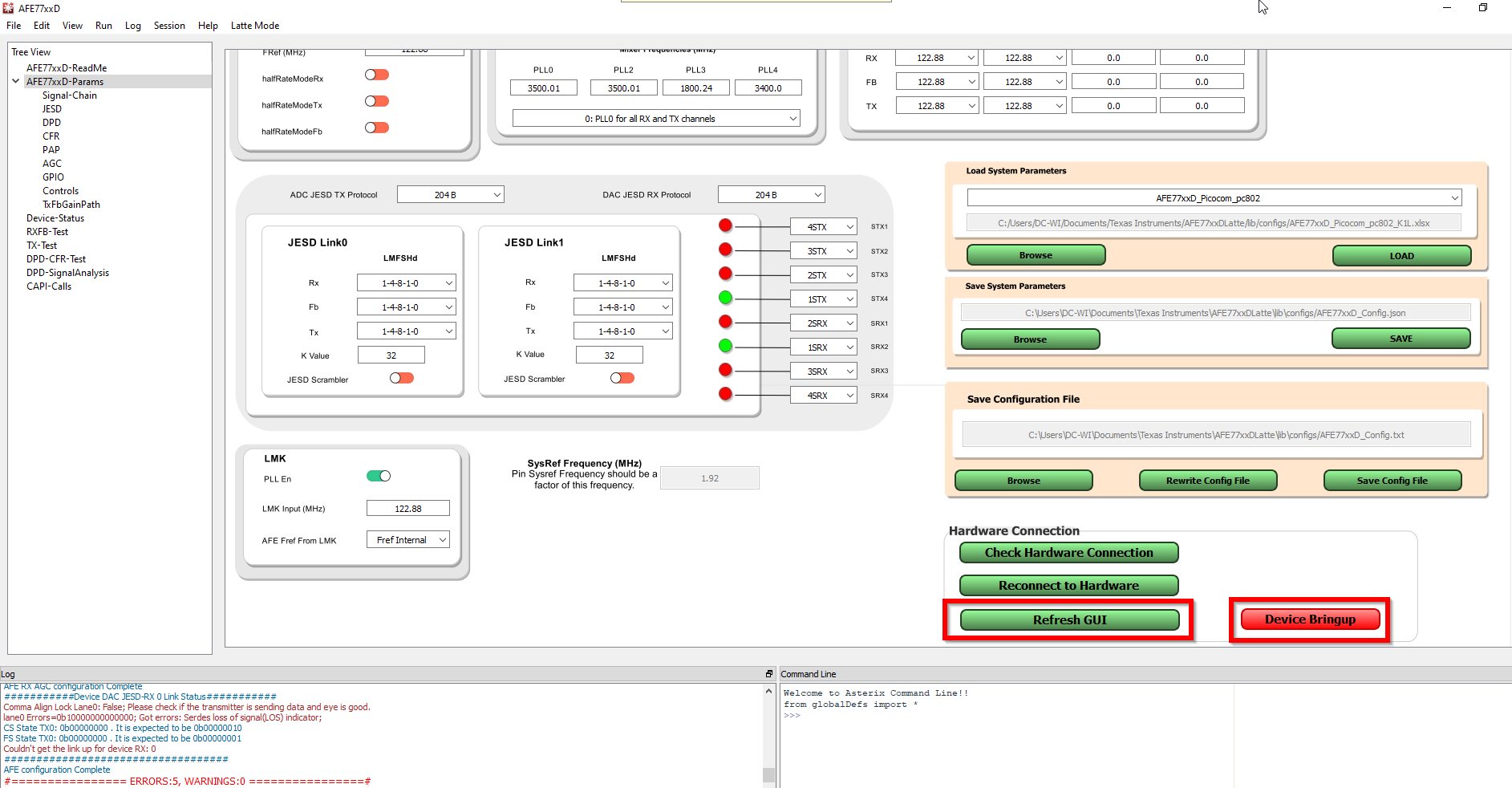

图 3-10 主窗口:GUI 模式

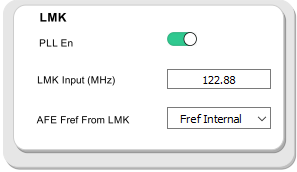

图 3-10 主窗口:GUI 模式 - 在左下角设置 LMK 参数,如图 3-11 所示。

图 3-11 设置 LMK 参数

图 3-11 设置 LMK 参数 - 之后,在“Hardware Connection”下,点击“refresh GUI”按钮,您将在日志窗口中看到一条内容为“Refreshed GUI”的消息。然后点击“Device Bringup”,这将启动器件的启动过程。要正确导航,请参阅图 3-12。

图 3-12 器件启动

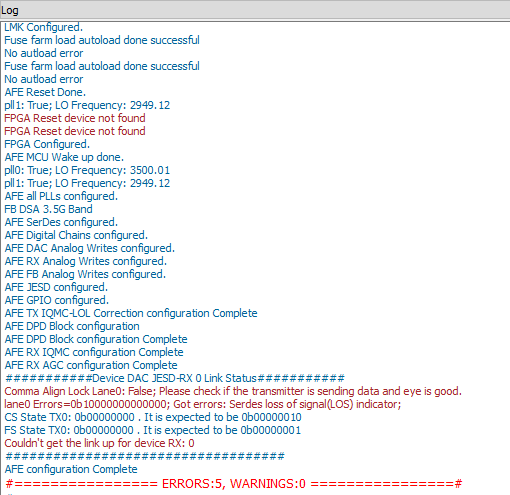

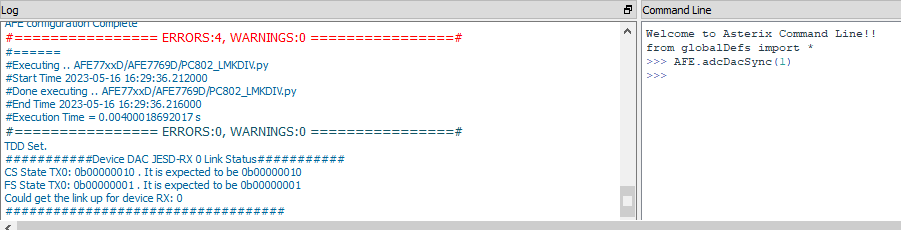

图 3-12 器件启动 - 器件启动完成后,您将在日志窗口中看到一些错误(如图 3-13 所示)。其中两个错误应该是“FPGA Reset device not found”,其余错误应该位于“Device DAC JESD-RX 0 Link Status”行下。由于 JESD 链路未建立,因此预计会出现这些错误。

图 3-13 启动后的 Latte 日志窗口

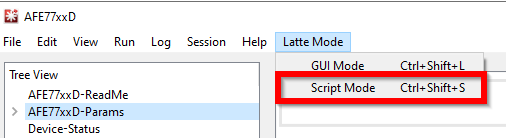

图 3-13 启动后的 Latte 日志窗口 - 在顶部,点击“Latte Mode”并导航至“Script Mode”,如图 3-14 中所示。

图 3-14 切换到“Script Mode”

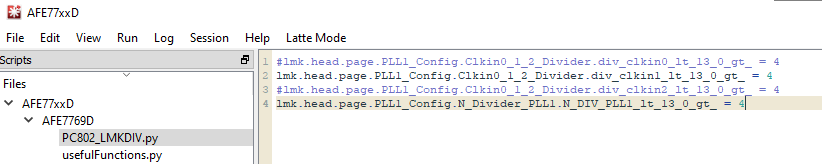

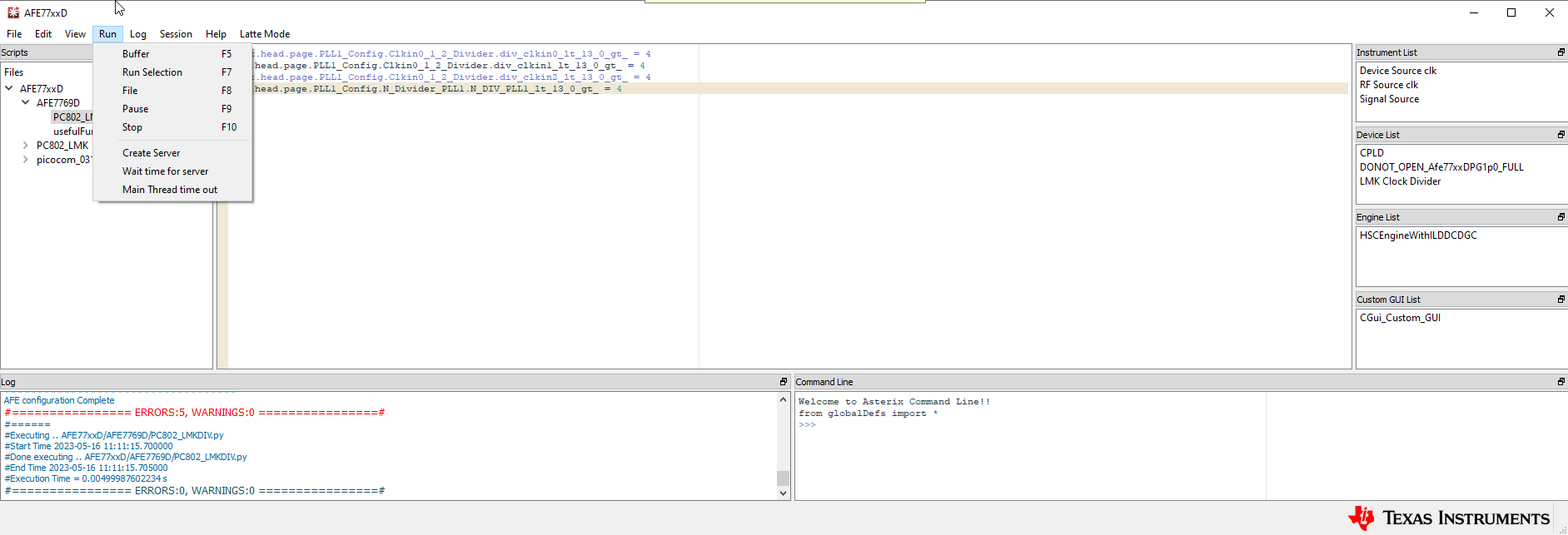

图 3-14 切换到“Script Mode” - 在左侧树视图中打开 PC802_LMKDIV.py 脚本,如图 3-15 中所示。

图 3-15 PC802 LMK 脚本

图 3-15 PC802 LMK 脚本 - 通过按 F5 或依次点击“Run”>“Buffer”来运行脚本。您应该会在日志窗口中看到如图 3-16 中所示的输出,表明脚本已运行且没有错误。运行该脚本后,如果连接了来自 PC802 的 122.88MHz 基准,则 LMK_LOCKED LED (D11) 会亮起。

图 3-16 运行 LMK 脚本

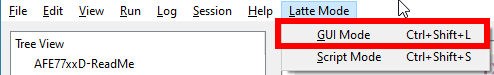

图 3-16 运行 LMK 脚本 - 点击“Latte Mode”并导航至“GUI Mode”,如图 3-17 中所示。

图 3-17 切换到“GUI Mode”

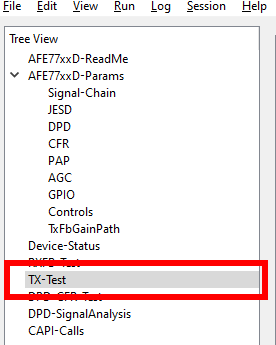

图 3-17 切换到“GUI Mode” - 点击树视图下的“TX-Test”,如图 3-18 所示。

图 3-18 在 Latte 中切换到“TX-Test”选项卡

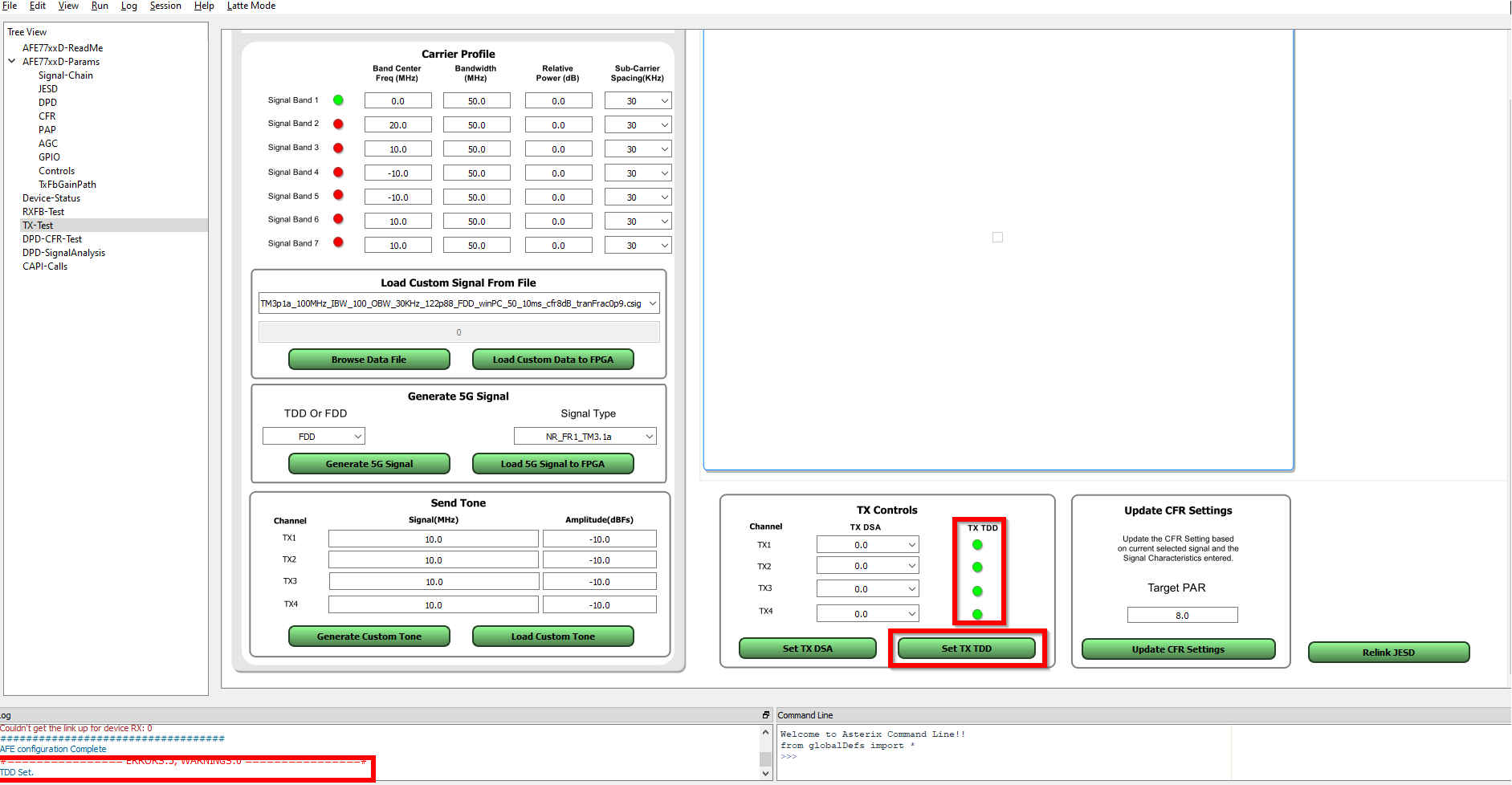

图 3-18 在 Latte 中切换到“TX-Test”选项卡 - 通过将 TX 通道设置为绿色,启用这些通道的 TDD,如图 3-19 所示。然后,点击“Set TX TDD”,日志窗口中应该会出现一条消息,显示“TDD set”。

图 3-19 启用 TDD 模式

图 3-19 启用 TDD 模式 - 按照 2.2 节中的 PC802 EVB RFIC 演示用户指南(版本 3)(此文档位于何处或文献编号是什么?)继续设置 PC802。进入第 2.2.5 节后,在测试模式工具上输入“start”命令开始发送数据后,在 AFE77xxD GUI 的命令行中键入“AFE.adcDacSync(1)”命令。现在,您应该能够在日志窗口中看到一份报告,报告指出 JESD 链接已建立且没有错误,如图 3-20 所示。数据将从 AFE TX 通道中传出。

图 3-20 JESD 链路启动

图 3-20 JESD 链路启动