ZHCUBL6 December 2023 CC3300 , CC3301 , CC3301MOD , CC3351

3.6 SDIO

SDIO 是与主机处理器连接用于实现 WLAN 功能的主要通信接口,也可用于共享 SDIO 协议中的 BLE 功能。由于时钟原因,这些信号特别敏感,因此应按原样设计。

SDIO 线路包括 SDIO_CLK、SDIO_CMD、SDIO_D0、SDIO_D1、SDIO_D2 和 SDIO_D3。特别是 SDIO_CLK 信号非常敏感,应特别关注。为了确保实现可靠的 SDIO 通信,应考虑以下布局注意事项:

- 建议 SDIO 线路的宽度至少为 5mil。

- SDIO 布线应尽可能远离其他数字或模拟信号布线。

- 建议在 SDIO 总线周围添加接地屏蔽。

- SDIO_CLK 必须通过接地过孔(拼接过孔)和相邻的接地平面与所有其他信号隔离。信号布线的间隙应至少为其他 SDIO 信号布线宽度的两倍。

- 将 SDIO 线路相互平行布线,长度要尽可能短(以便减少传播延迟),其间隙为布线宽度的 1.5 倍。

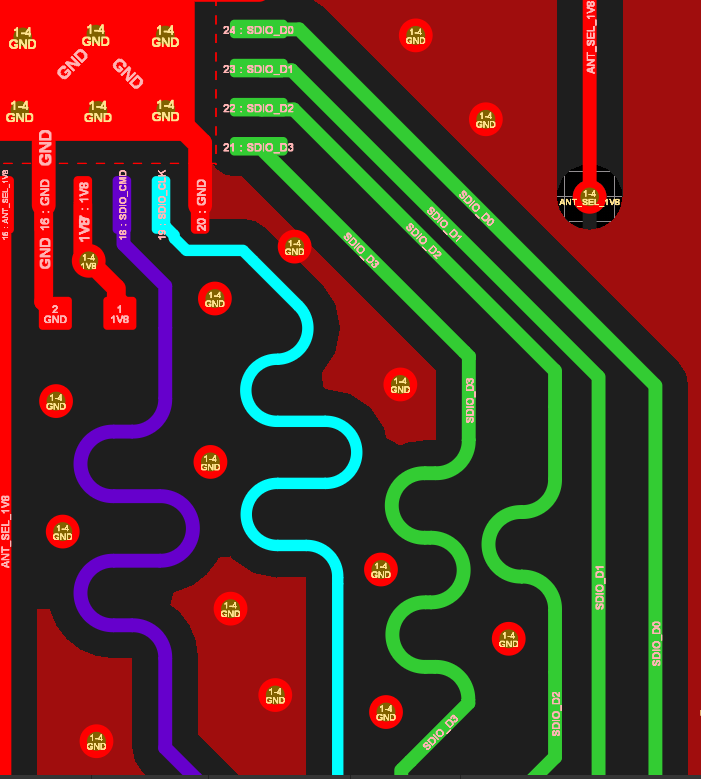

- SDIO 布线的长度必须在 20mil 容差范围内进行匹配,以便在所有布线上同时提供采样数据。有关长度调优的直观示例,请参阅图 3-15。

图 3-15 来自 BP-CC3301 设计文件。

图 3-15 SDIO 信号的参考布局

图 3-15 SDIO 信号的参考布局