ZHCUBN4 December 2023

2.3 默认运行模式

了解了电路板的设置方法以及如何为电路板供电后,下一个主题将介绍如何操作电路板。该电路板开箱即用,在通电后可将 THVD2412 作为全双工 RS-485 收发器运行。器件引脚分为四个不同的组:单端通信引脚、差分通信引脚、电源引脚和控制引脚。前面已经讨论了电源引脚,现在介绍其他三个类别。

单端通信引脚直接通过相应的跳线连接到单端总线 – 这些引脚是“R”和“D”引脚,分别表示 RX 和 TX 单端数据线。R 以 J1 为基准,D 以 J4 为基准;这些是 EVM 的信号连接点。

该电路板支持的控制信号是高电平有效的驱动器使能 (DE) 和低电平有效的接收器使能 (/RE)。这些引脚遵循 TTL 逻辑,对于逻辑低电平值,电压为 0V 至 0.8V;对于逻辑高电平值,电压为 2V 至 VCC。这些引脚分别通过跳线 J3 和 J2 进行访问

最后,最后一组信号是差分总线引脚 A、B、Y 和 Z。A 和 B 引脚是差分接收器,连接到标有 J11 的 3 引脚端子块,还可通过两个 4 引脚接头 J9 和 J10 连接 A 和 B 线路。Y 和 Z 引脚是差分驱动器引脚,连接到标有 J14 的 3 引脚端子块,还可通过两个 4 引脚接头 J12 和 J13 连接 Y 和 Z 线路。两条差分线路都具有 0805 元件焊盘,用于端接电容和电阻。

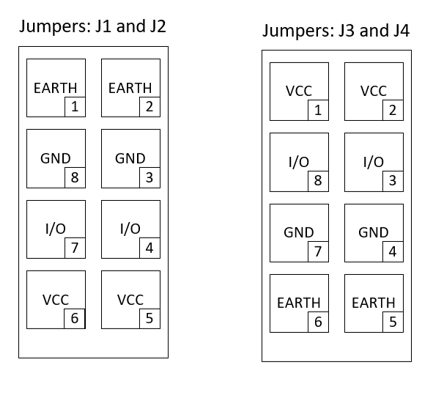

单端跳线配置映射可用于帮助操作电路板。接头的引脚 1 位于所示跳线的左上角,J5 位于电路板顶部,随后的每个引脚沿顺时针方向递增一个。

图 2-1 单端(控制台侧)跳线映射

图 2-1 单端(控制台侧)跳线映射| 跳线 ID | 信号 – 跳线引脚 | 说明 |

|---|---|---|

| J1 | R – 引脚 4 或 7 | 接收数据 – 为了始终保持高电平或低电平,应将 J1 I/O 引脚分流至 VCC 或 GND。 |

| J2 | /RE – 引脚 4 或 7 | /RE – 将 J2 I/O 引脚分流至 VCC 或 GND,以在引脚上设置恒定状态。 |

| J3 | DE – 引脚 3 或 8 | DE – 将 J3 I/O 引脚分流至 VCC 或 GND,以在引脚上设置恒定状态。 |

| J4 | D – 引脚 3 或 8 | 发送数据 – 为了始终保持高电平或低电平,应将 J4 I/O 引脚分流至 VCC 或 GND |

| J11 | 差分总线输入 | A 和 B 差分输入数据 |

| J14 | 差分总线输出 | Y 和 Z 差分输出数据 |