ZHCUBT9A January 2024 – September 2024

2.6.1.1 工业以太网 PHY

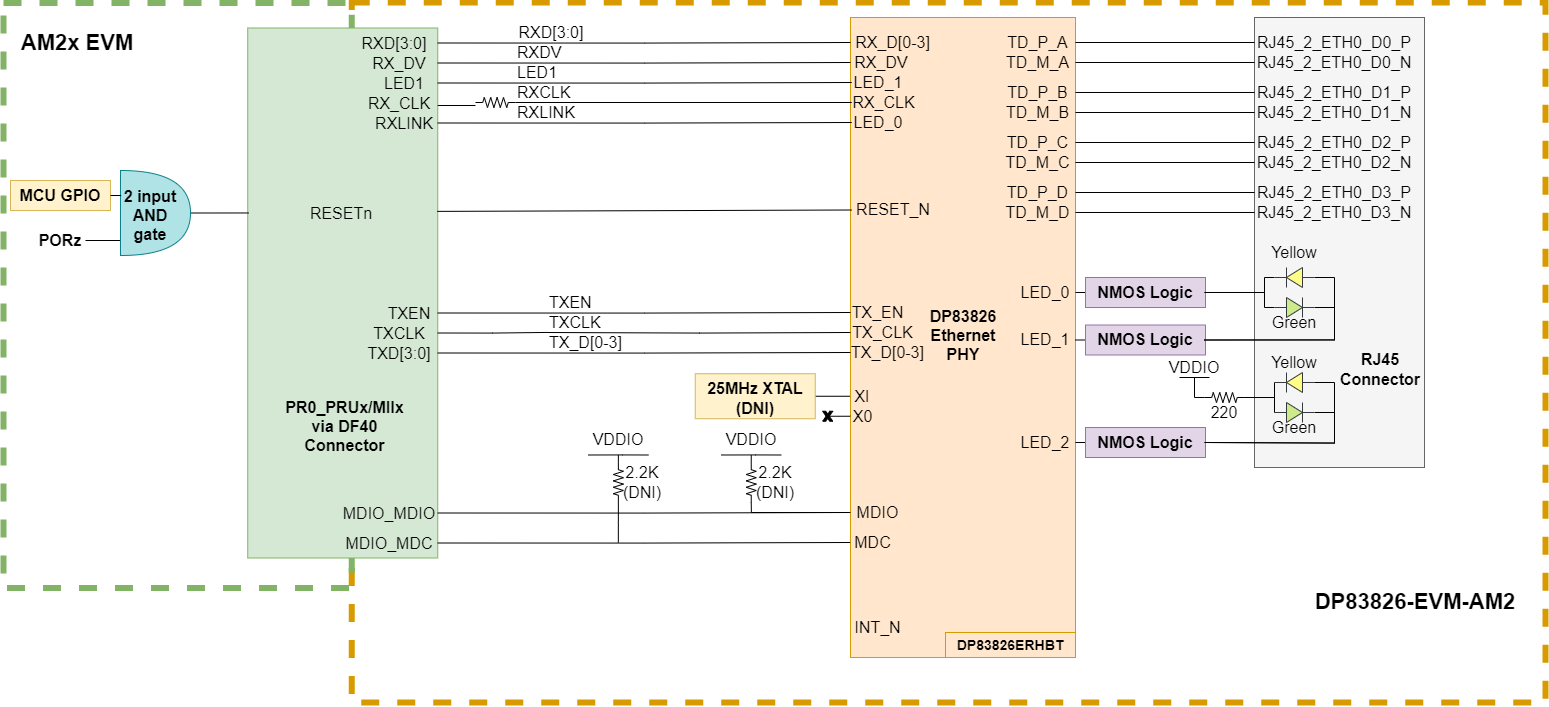

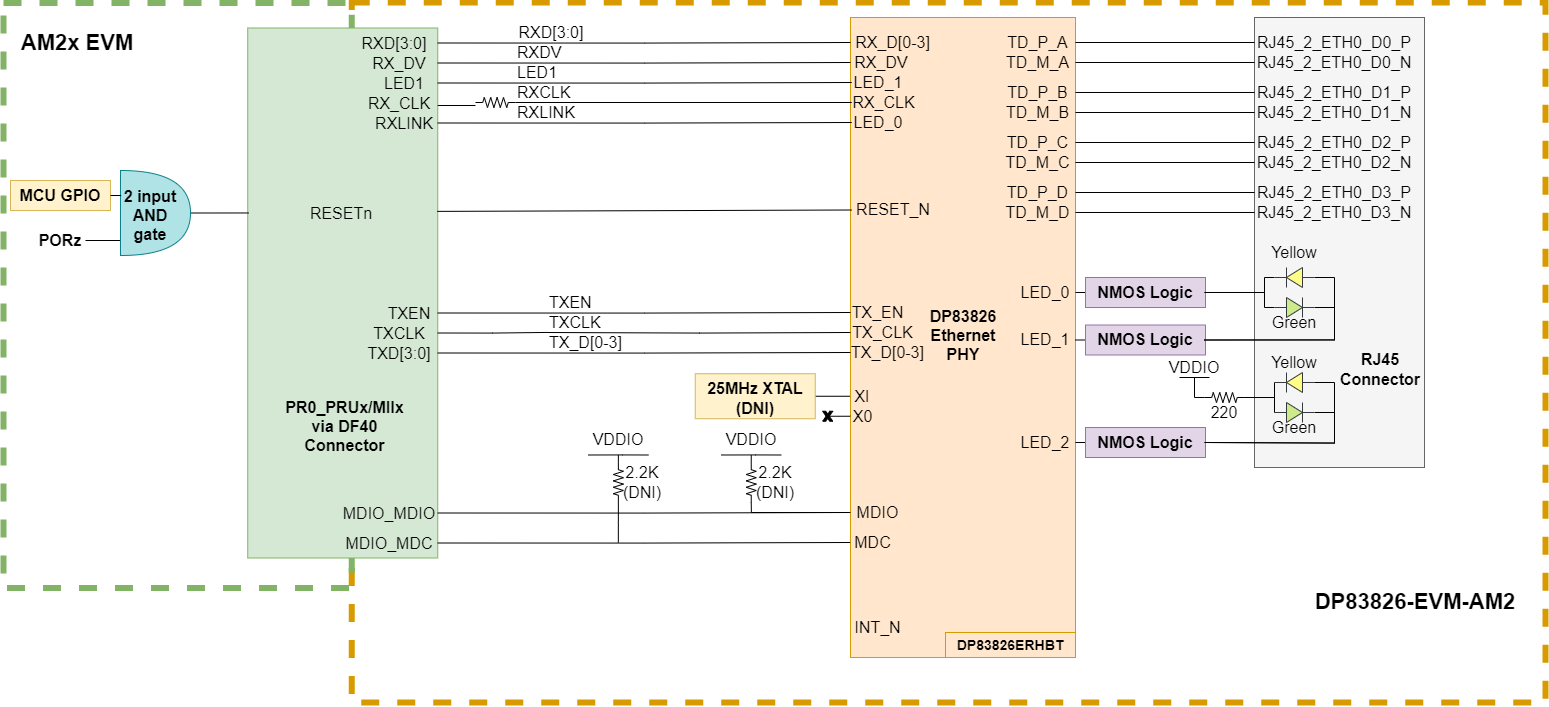

AM2x EVM 工业以太网 PHY 附加电路板使用一个 RGMII 信号端口和 PRU-ICSS 的 PRUx 内核连接到 32 引脚以太网 PHY (DP83826ERHBT)。该 PHY 配置为广播 10/100Mb 操作。该 PHY 的以太网数据信号端接至 RJ45 连接器。LED 用于指示链路状态和活动。

图 2-5 工业以太网 PHY

该以太网 PHY 需要两个电源,即 VDDIO(3.3V 或 1.8V)和 VDDA3V3 (3.3V),这些电源通过 DF40GB 连接器 (J2) 提供。

在一些 AM2x EVM 上,CPSW 信号的 RGMII 端口在 PRU-ICSS 以太网信号使用的相同 MCU 焊球上进行内部多路复用。要使用 RGMII,必须将焊球设置为适合 RGMII 的多路复用模式。

从主 EVM SoC 到 PHY 的 MDIO 和中断信号需要通过 2.2KΩ 上拉电阻器连接到 I/O 电源电压,才能正常工作。默认情况下,DP83826-EVM-AM2 上未组装这些电阻器,但如果主 EVM 没有上拉这些信号,则可以组装这些电阻器。中断信号由主 EVM SoC 映射的 GPIO 信号驱动。

以太网 PHY 的复位信号多数情况下由 2 路输入与门驱动。与门的输入是由主 SoC EVM 生成的 GPIO 信号和主 EVM 上的上电复位信号。