ZHCUBV0 March 2024 DLPC964

- 1

- 摘要

- 商标

- 1概述

- 2Apps FPGA 模块

- 3功能配置

-

4附录

- 5.1 Vivado Chipscope 捕获结果

- 5.2 DLPC964 Apps 位流加载

- 5.3

使用 Aurora 64B/66B 连接到 DLPC964 控制器

- 5.3.1 工作原理

- 5.3.2 概述

- 5.3.3

Aurora 64B/66B TX 内核和 RTL 生成

- 5.3.3.1 从 IP Catalog 中选择 Aurora 64B66B

- 5.3.3.2 配置 Core Options

- 5.3.3.3 信道配置

- 5.3.3.4 Shared Logic 选项

- 5.3.3.5 生成示例设计文件

- 5.3.3.6 RTL 文件列表

- 5.3.3.7 单通道 3 信道 Aurora 内核 RTL 包装器

- 5.3.3.8 四通道 12 信道顶层 RTL 包装器

- 5.3.3.9 块以块控制字开始

- 5.3.3.10 块以 DMDLOAD_REQ 完成

- 5.3.3.11 DMDLOAD_REQ 建立时间要求

- 5.3.3.12 单通道传输模式

- 5.3.3.13 DMD 块阵列数据映射

- 5.3.3.14 Xilinx IBERT

- 5缩略语和首字母缩写词

- 6米6体育平台手机版_好二三四 (TI) 相关文档

4.3.3.10 块以 DMDLOAD_REQ 完成

请参阅图 4-11:DLPC964 系统方框图

DMDLOAD_REQ 是从 Apps FPGA 发送到 DLPC964 控制器的信号。

一旦 Aurora 块数据传输完成,Apps FPGA 用户逻辑必须将 DMDMDLOAD_REQ 置为有效以便向 DLPC964 指示这是 DMD 块的结束位置并触发执行块控制字中编码的操作。

将 DMDLOAD_REQ 信号置为有效和发送块控制字的指南:

- Apps FPGA 用户逻辑必须等待块传输在全部四个 Aurora 数据通道上完成,然后再将 DMDLOAD_REQ 置为有效。

- Apps FPGA 必须考虑到四个 Aurora 数据通道接口彼此不完全同步,因此不会在完全相同的时钟周期完成数据传输。所以,在将 DMDLOAD_REQ 置为有效前,Apps FPGA 必须监控并验证 Aurora 块数据传输在所有四个通道上均已完成。

注: 在 Aurora 块传输完成前将 DMDLOAD_REQ 置为有效可能导致数据不能正确加载到 DMD。 - 在完成一个 Aurora 块传输后,只要满足 300ns 的 DMDLOAD_REQ 建立时间,即可将 DMDLOAD_REQ 立即置为有效(更多信息,请参阅节 4.3.3.11)。

- Apps FPGA 用户逻辑必须在启动下一个新 DMD 块的发送之前将当前块的 DMDLOAD_REQ 置为有效。每个块必须以一个块控制字数据包开头并以 DMDLOAD_REQ 置位结束。

- 对于不涉及块数据传输的操作(例如块清除/置位操作),仍然需要 DMDLOAD_REQ,并且仍然必须满足 300ns 的建立时间(更多信息,请参阅节 4.3.3.11)。

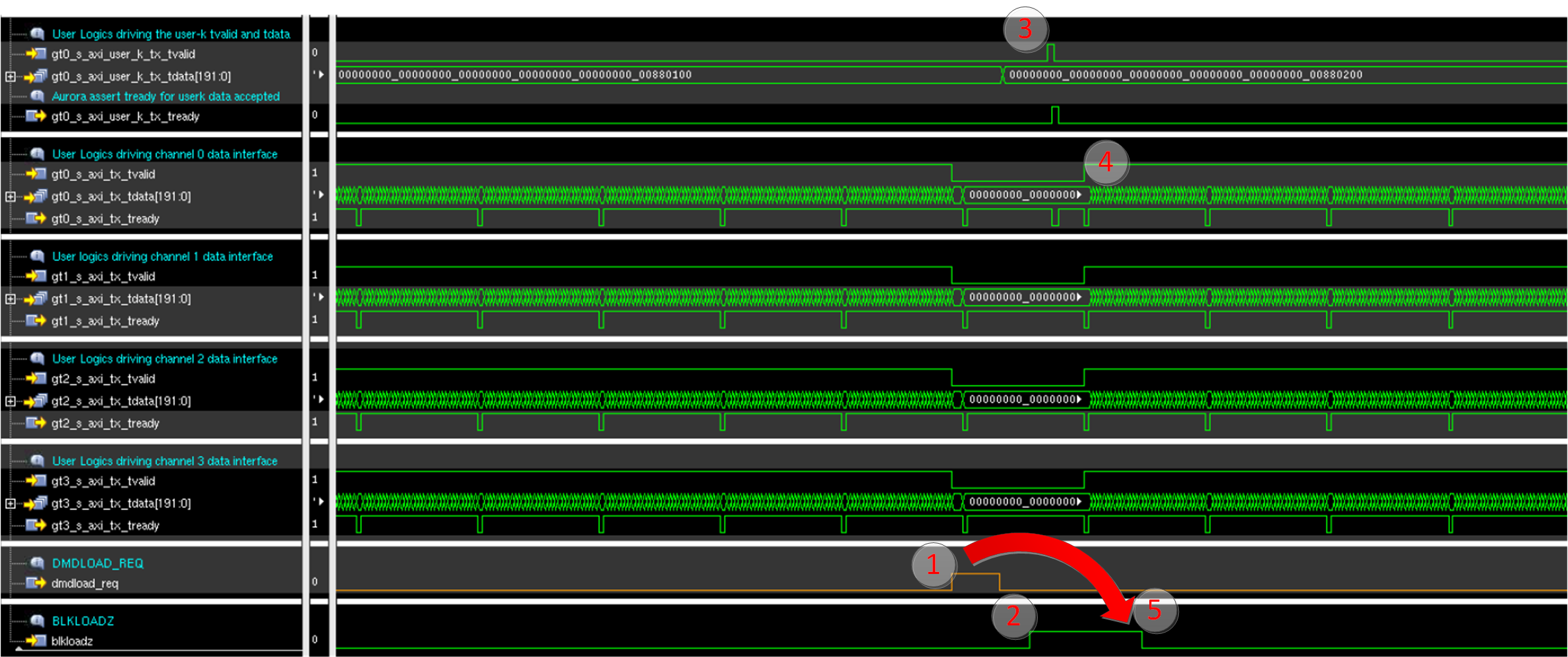

- 请参阅图 4-19,了解在 Apps 用户逻辑完成当前块的传输后的情况。用户可以发现 DLPC964 仍在将上一个块加载到 DMD 中(例如,BLKLOADZ 为低电平)。在 BLKLOADZ 为低电平时,Apps FPGA 仍可以将 DMDLOAD_REQ 置为有效,因为 DLPC964 可以检测并存储该 DMDLOAD_REQ 请求。在完成当前 DMD 块的 Aurora 数据传输并将 DMDLOAD_REQ 信号置为有效后,Apps FPGA 必须等待 DLPC964 将 BLKLOADZ 置为无效(例如,BLKLOADZ 从低电平转换为高电平),然后再启动下一个块的传输。BLKLOADZ 置为无效意味着 DLPC964 已完成了前一个块的 DMD 数据加载操作,并且释放了数据缓冲器以便从 Aurora 接口接受新的数据块。注: DLPC964 具有两个数据块缓冲器:一个用于接收传入的 Aurora 数据块,另一个用于保存前一个数据块以将数据流式输出到 DMD。如果 Apps FPGA 没有将 Aurora 块传输与 BLKLOADZ 的“置为无效”信号同步,则缓冲器可能会溢出,数据也无法正确加载到 DMD。

- 请参阅图 4-20,了解 Apps FPGA 选择向 DLPC964 发送 DMD 数据块但延迟 DMDLOAD_REQ 置为有效的情况。

图 4-19 块 DMDLOAD_REQ 置为有效结束之后的新块控制字波形

图 4-19 块 DMDLOAD_REQ 置为有效结束之后的新块控制字波形- 在全部四个 Aurora 数据接口上的当前块数据传输完成后,Apps FPGA 用户逻辑立即将 DMDLOAD_REQ 置为有效。

- DLPC964 将 BLKLOADZ 置为无效以指示前一个 DMD 块的数据加载操作完成。

- APPS FPGA 用户逻辑会检测 BLKLOADZ 置为无效的情况,并在 Aurora 通道 0 user-k 端口上为下一个块发送新的块控制字。

- Apps FPGA 用户逻辑发送下一个块的数据。

- BLKLOADZ 由 DLPC964 置为低电平有效,指示当前块的数据加载操作由 DMDLOAD_REQ 触发。

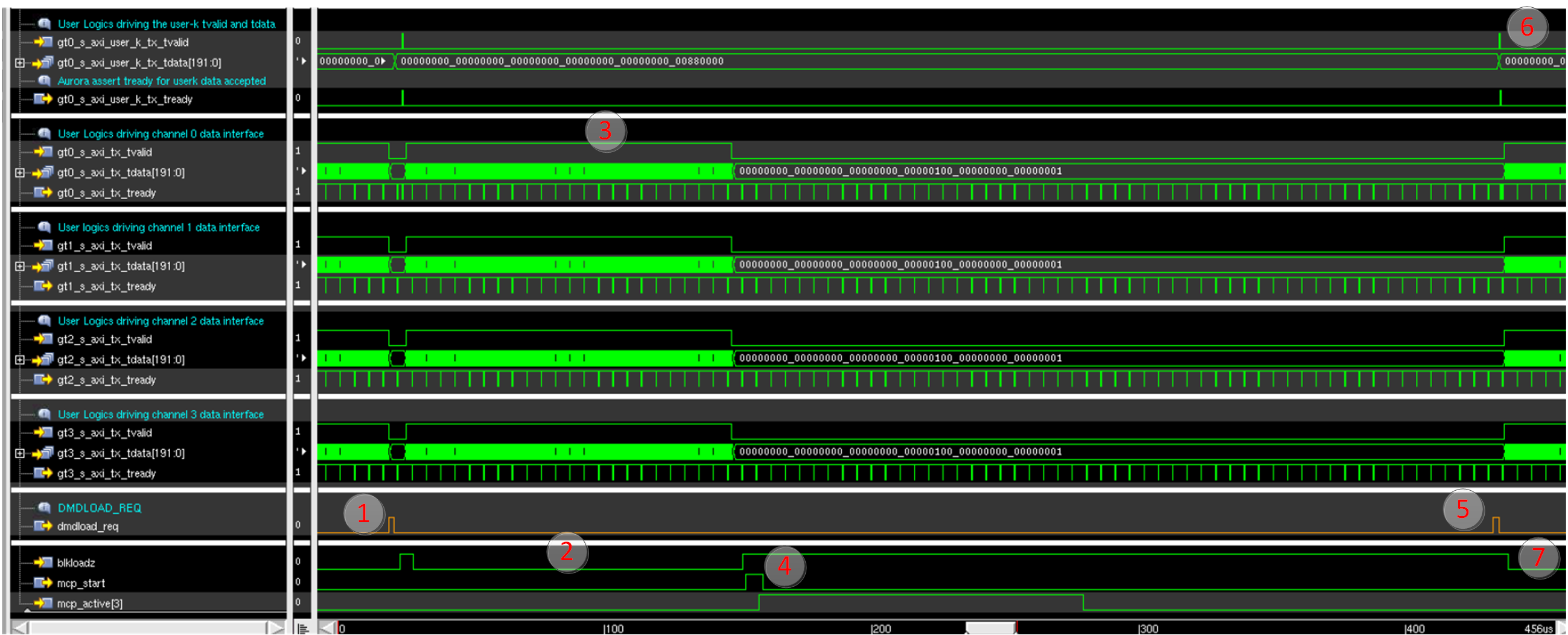

图 4-20 DMDLOAD_REQ 延迟置为有效波形

图 4-20 DMDLOAD_REQ 延迟置为有效波形- Apps FPGA 完成当前图形的最后一个块(块 15)的数据发送,并将 DMDLOAD_REQ 置为有效以指示 DLPC964 执行数据加载操作。

- 从块 1 到块 15,DLPC964 均由 DMDLOAD_REQ 触发加载数据。

- 当 DLPC964 加载当前图形的块 15 时,Apps FPGA 通过 Aurora 数据接口发送下一个图形第一个块(块 0)的数据。

- 在当前图形的块 15 的数据加载完成后,DLPC964 会将 BLKLOADZ 置为无效。Apps FPGA 检测到针对当前图形最后一个块的 BLKLOADZ 已置为无效并且这个块已经加载到 DMD 上,然后发出 MCP_START 以进行全局块复位操作。

- 由于需要满足微镜稳定时间的要求,Apps FPGA 延迟将下一个图形中块 0 的 DMDLOAD_REQ 置为有效。

- 将下一个图形的块 0 的 DMDLOAD_REQ 置为有效后,发送块 1 的块控制字。

- DLPC964 将 BLKLOADZ 置为有效以指示 DMD 数据加载操作是由第 5 部分的 DMDLOAD_REQ 触发的。